Document identifier: MCXNx4xSRM Reference Manual Rev. 4, 09/2024

# MCX Nx4x Security Reference Manual

Supports MCXN54x and MCXN94x

# **Contents**

| Chapter 1 About this manual                        |     |

|----------------------------------------------------|-----|

| 1.1 About This Document                            |     |

|                                                    |     |

| Observation Oslatus desettos                       | 40  |

| Chapter 2 Introduction                             |     |

| 2.1 Overview                                       |     |

| 2.2 Target applications                            |     |

| 2.3 Block diagram                                  |     |

| 2.4 System bus priority and arbitration            | 13  |

|                                                    |     |

| Chapter 3 Security Overview                        |     |

| 3.1 Disclaimer                                     |     |

| 3.2 Overview                                       |     |

| 3.3 Immutable Root of Trust                        |     |

| 3.4 Life-cycle management                          |     |

| 3.5 Secure boot                                    |     |

| 3.6 Secure update                                  |     |

| 3.7 Secure debug                                   |     |

| 3.8 IP protection                                  | 17  |

| 3.9 Secure isolation                               |     |

| 3.10 Secure attestation                            |     |

| 3.11 Secure storage                                |     |

| 3.12 Trust provisioning                            |     |

| 3.13 Secure key management                         |     |

| 3.14 Anomaly Detection and Reaction                |     |

| 5. 14 Anomaly Detection and Neaction               | 10  |

| Ohantan 4 Cana Owaniawa                            | 40  |

| Chapter 4 Core Overview                            |     |

| 4.1 Introduction                                   |     |

| 4.2 CPU0 and CPU1 Cortex-M33 Code and System buses |     |

| 4.3 Nested Vectored Interrupt Controller (NVIC)    |     |

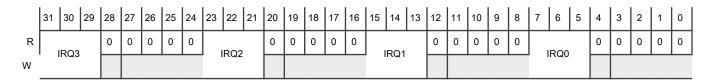

| 4.4 Implementation Defined Attribution Unit (IDAU) |     |

| 4.5 System memory map                              |     |

| 4.6 Peripheral Bridge (PBRG)                       | 31  |

|                                                    |     |

| Chapter 5 Life Cycle States                        | 40  |

| 5.1 Life cycle states for secure devices           | 40  |

|                                                    |     |

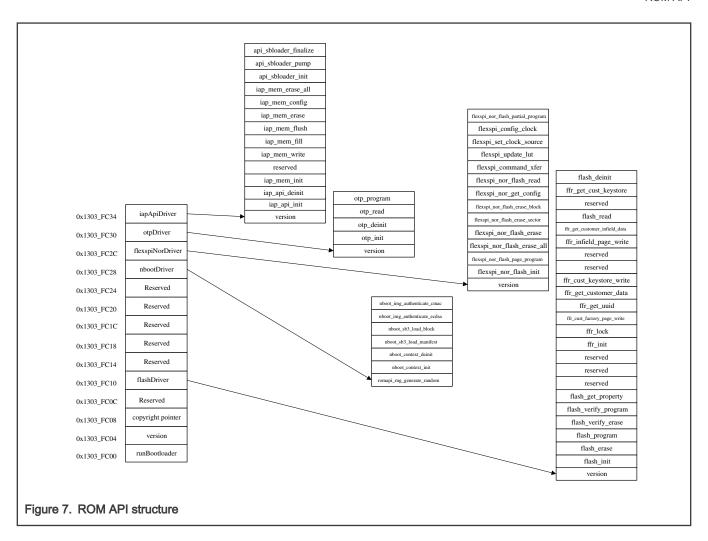

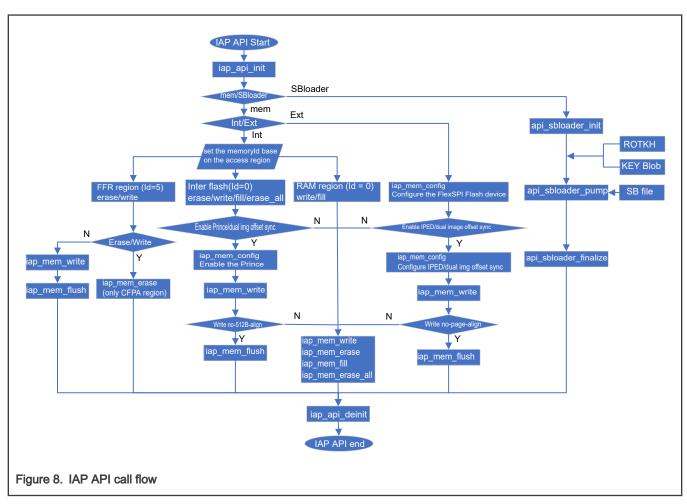

| Chapter 6 ROM API                                  | 49  |

| 6.1 Overview                                       |     |

| 6.2 Functional description.                        |     |

| 0.2 i undudna description                          |     |

| Chantar 7 In System Programming (ISD)              | 447 |

| Chapter 7 In-System Programming (ISP)              |     |

| 7.1 Overview                                       |     |

| 7.2 Functional description                         |     |

| 7.3 ISP protocol                                   | 119 |

| 7.4 Bootloader packet types                        | 120 |

|                                                      | Contents |

|------------------------------------------------------|----------|

| 12.5 Initialization                                  | 524      |

| 12.6 Application information                         |          |

| 12.7 Memory map and register definition              |          |

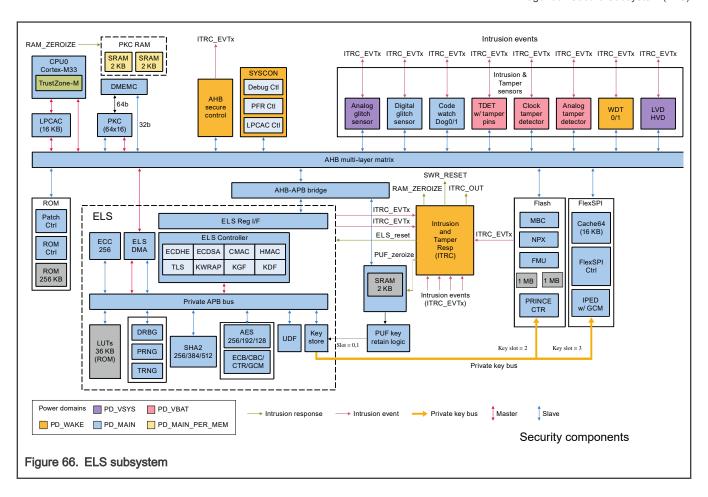

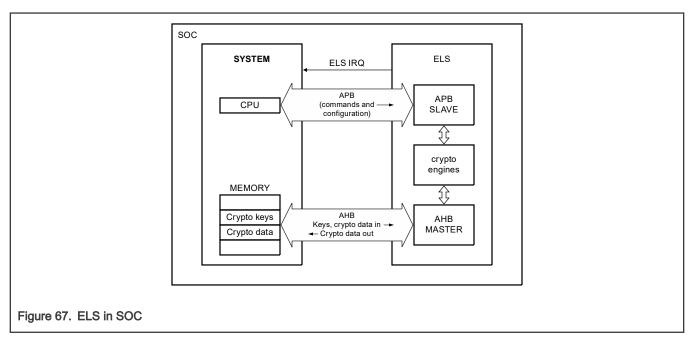

| Chapter 13 EdgeLock Secure Subsystem (ELS)           | 586      |

| 13.1 Chip-specific ELS information                   |          |

| 13.2 Terminology                                     |          |

| 13.3 Overview                                        |          |

| 13.4 Functional description                          |          |

| 13.5 External signals                                |          |

| 13.6 Initialization                                  |          |

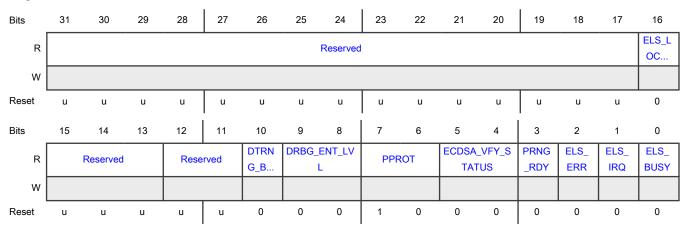

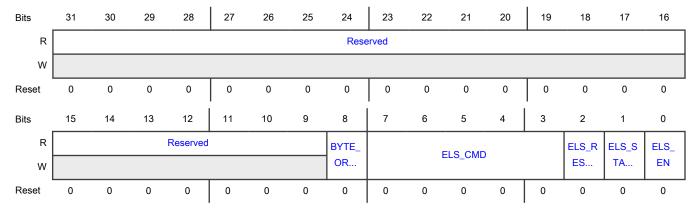

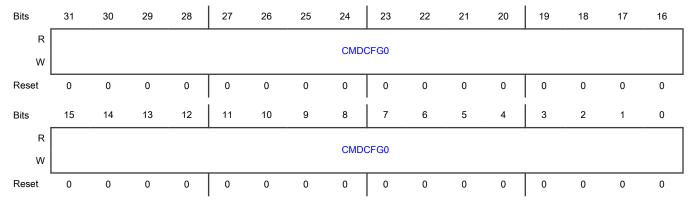

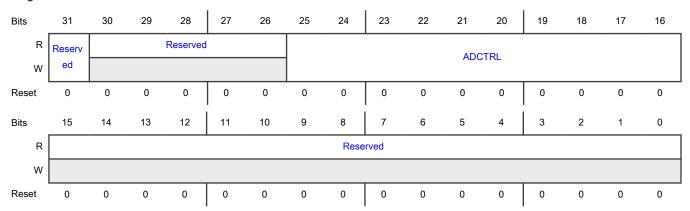

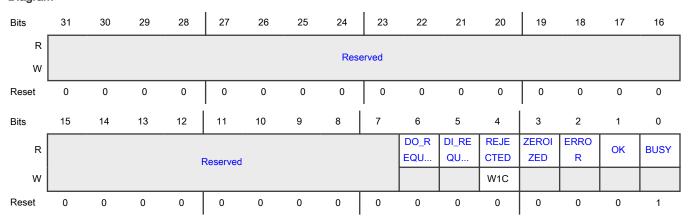

| 13.7 ELS register descriptions                       | 700      |

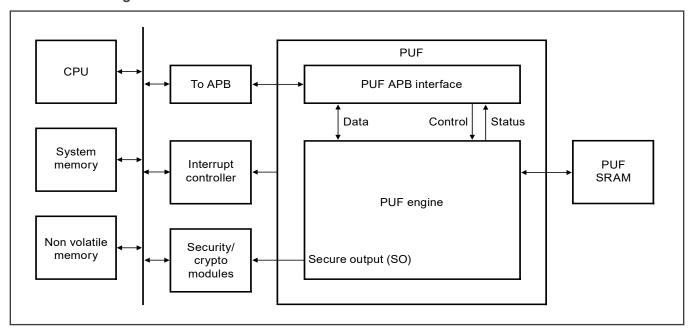

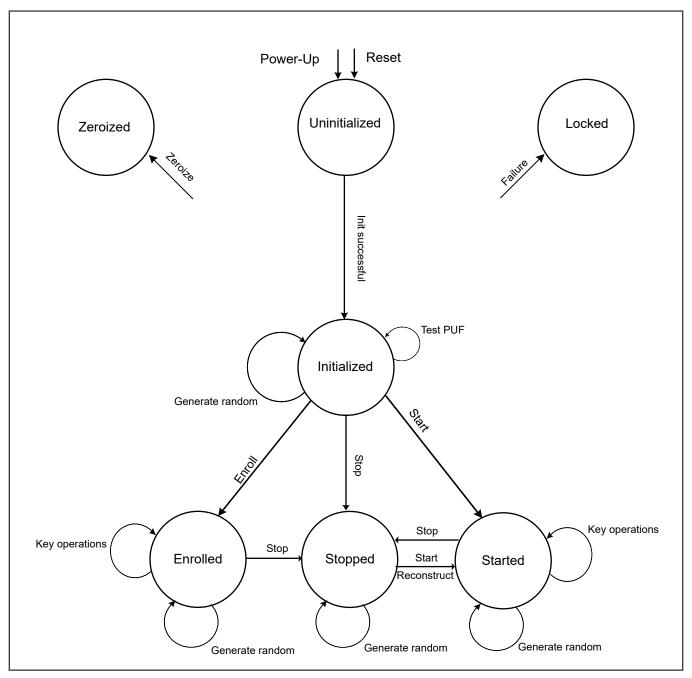

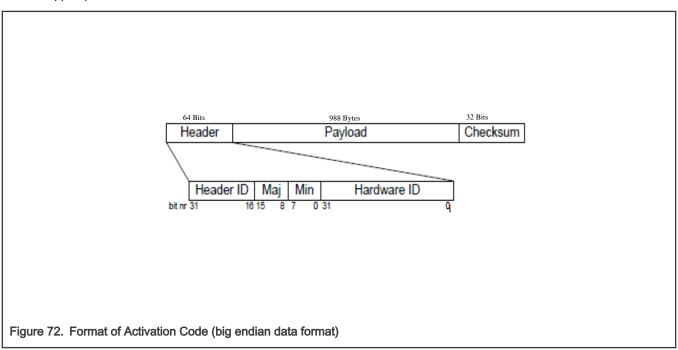

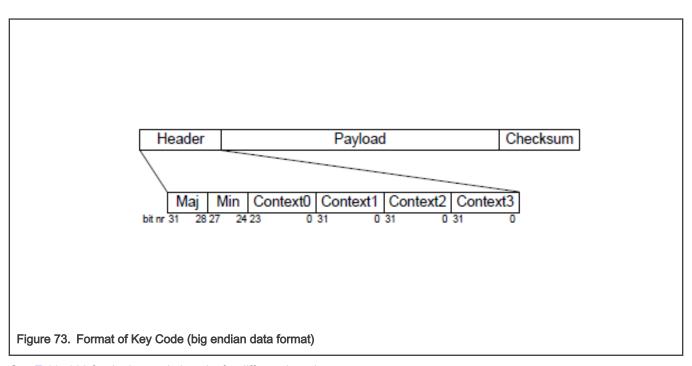

| Chapter 14 Physically Unclonable Function (PUF)      | 729      |

| 14.1 Chip-specific PUF information                   |          |

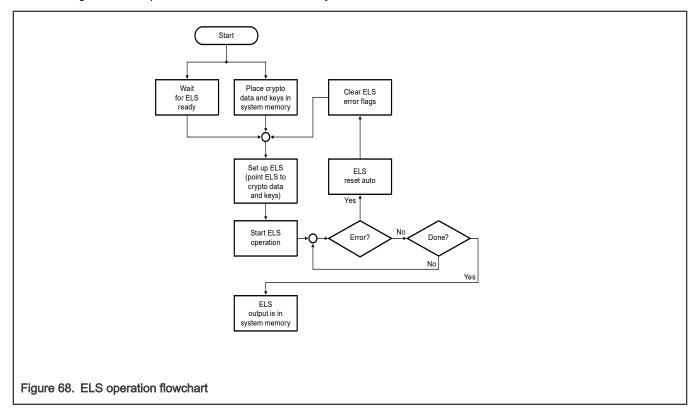

| 14.2 Overview                                        |          |

| 14.3 Functional Description                          |          |

| 14.4 Memory Map and register definition              | 752      |

| 14.5 Glossary                                        |          |

| Chapter 15 PUF Key Context Management                | 785      |

| 15.1 Chip-specific PUF_CTRL information              |          |

| 15.2 Overview                                        | 785      |

| 15.3 PUF Context Key Management                      | 785      |

| 15.4 Memory Map and register definition              |          |

| Chapter 16 Public-key Cryptography Accelerator (PKC) | 796      |

| 16.1 Chip-specific PKC information                   |          |

| 16.2 Overview                                        |          |

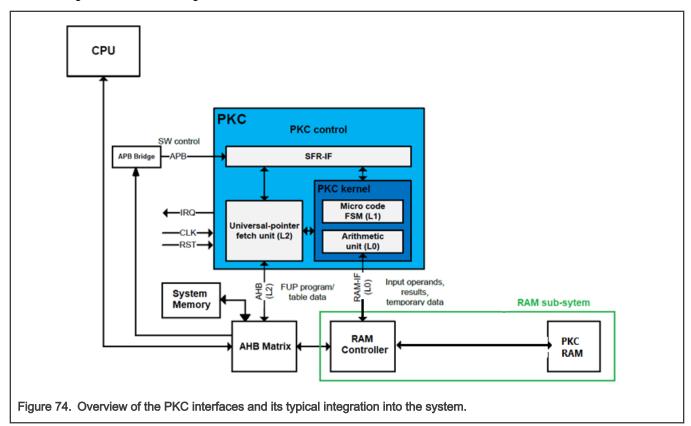

| 16.3 Block diagram                                   | 797      |

| 16.4 Functional description                          |          |

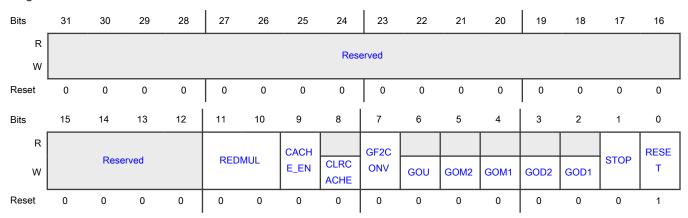

| 16.5 Handling of PKC_CTRL[RESET] and PKC_CTRL[STOP]  |          |

| 16.6 PKC register descriptions                       | 853      |

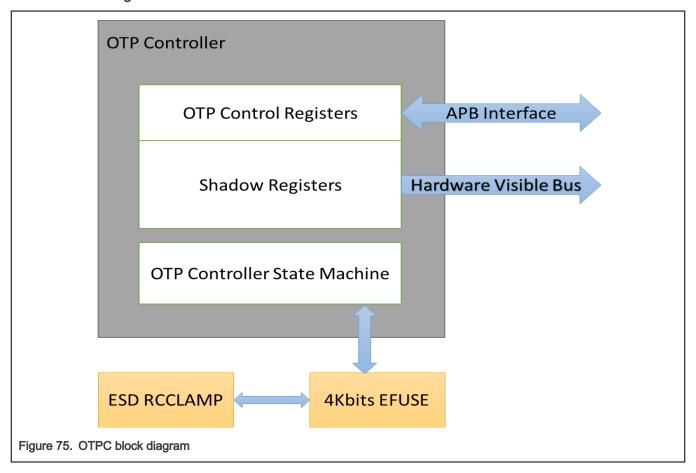

| Chapter 17 OTP Controller (OTPC)                     | 884      |

| 17.1 Chip-specific OTPC information                  |          |

| 17.2 Overview                                        |          |

| 17.3 Functional description                          |          |

| 17.4 External signals                                |          |

| 17.5 Initialization                                  |          |

| 17.6 Application information                         |          |

| 17.7 Memory Map and register definition              | 888      |

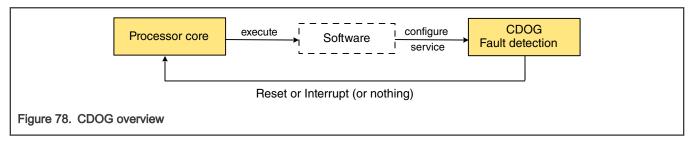

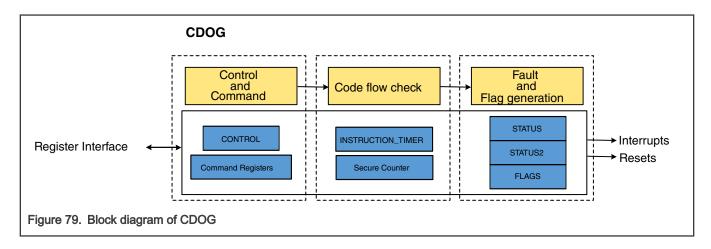

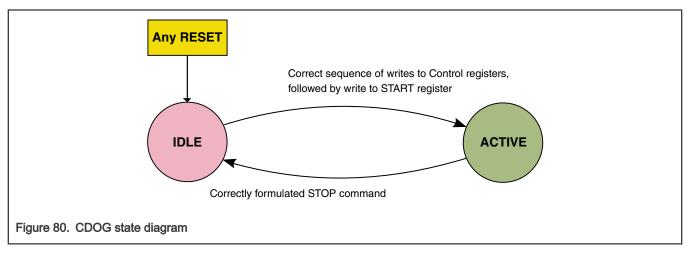

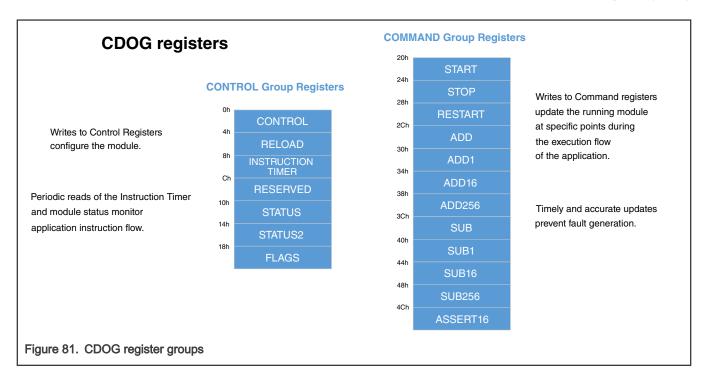

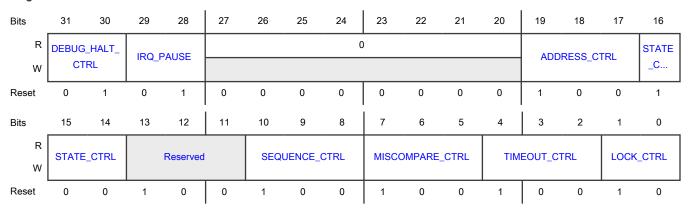

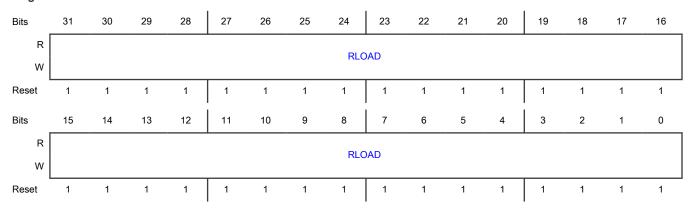

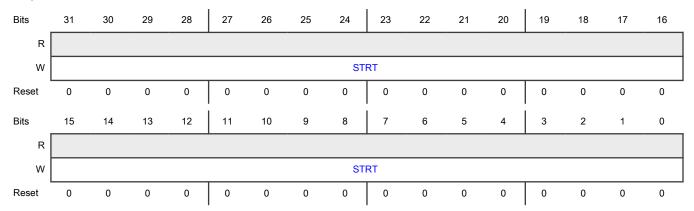

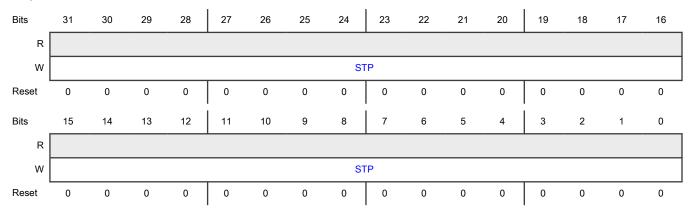

| Chapter 18 Code Watchdog Timer (CDOG)                | 908      |

| 18.1 Chip-specific CDOG information                  |          |

| 18.2 Overview                                        | 908      |

| 18.3 Functional description                          | 909      |

| 18.4 Application information                         | 913      |

| 18.5 Memory map and register definition              | 914      |

| Chapter 19 Glitch Detect (GDET)                            | 937  |

|------------------------------------------------------------|------|

| 19.1 Chip-specific GDET information                        |      |

| 19.2 Overview                                              |      |

| 19.3 Architecture Description                              |      |

| 19.4 Terms and Definition                                  | 948  |

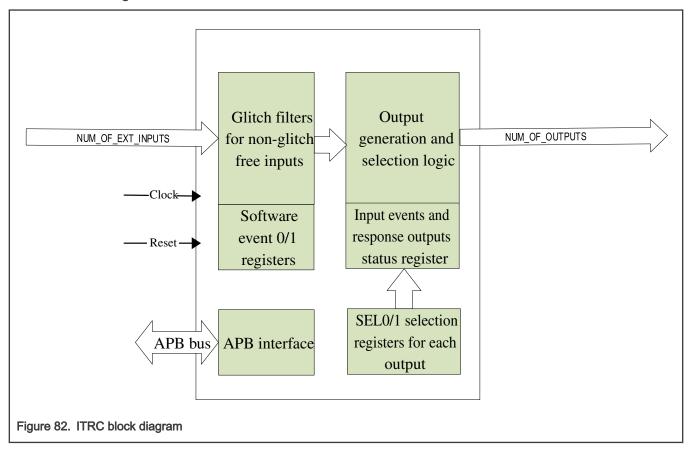

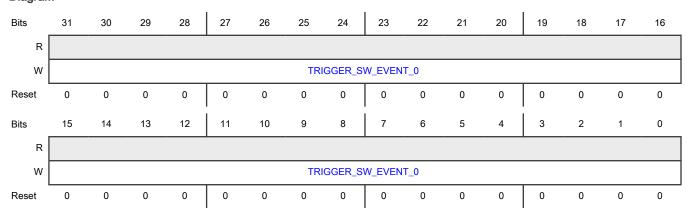

| Chapter 20 Intrusion and Tamper Response Controller (ITRC) | 950  |

| 20.1 Chip-specific ITRC information                        |      |

| 20.2 Overview                                              |      |

| 20.3 Functional description                                |      |

| 20.4 Signals                                               |      |

| 20.5 Memory map and register definition                    | 954  |

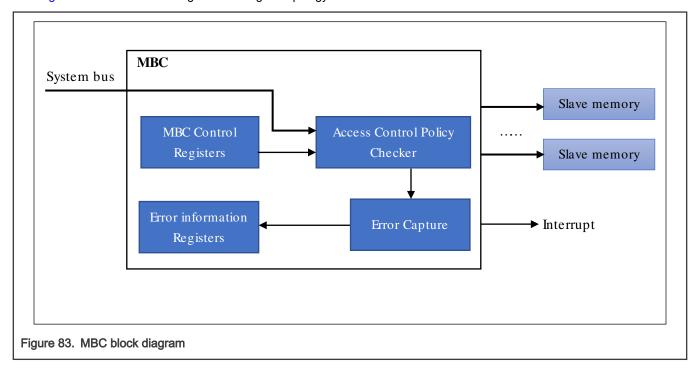

| Chapter 21 Memory Block Checker (MBC)                      | 974  |

| 21.1 Chip-specific MBC information                         |      |

| 21.2 Overview                                              | 975  |

| 21.3 Functional description                                |      |

| 21.4 External signals                                      |      |

| 21.5 Register descriptions                                 | 978  |

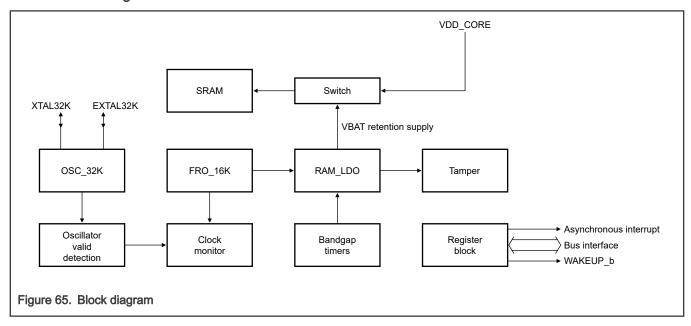

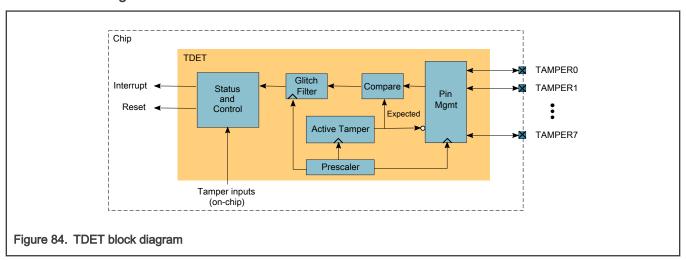

| Chapter 22 Digital Tamper (TDET)                           | 1010 |

| 22.1 Chip-specific TDET information                        | 1010 |

| 22.2 Overview                                              |      |

| 22.3 Functional description.                               |      |

| 22.4 External signals                                      |      |

| 22.5 Initialization                                        |      |

| 22.0 rogistor dominatorio                                  |      |

| Chapter 23 Secure AHB bus and AHB Controller (AHBSC)       | 1032 |

| 23.1 Chip-specific Secure AHB Controller information       |      |

| 23.2 Overview                                              |      |

| 23.3 Functional description                                |      |

| 23.4 Memory Map and Registers                              | 1050 |

| Chapter 24 Flash Controller (FMC)                          | 1223 |

| 24.1 Chip-specific FMC information                         |      |

| 24.2 Overview                                              |      |

| 24.3 Functional description                                |      |

| 24.4 External signals                                      |      |

| 24.5 Initialization and application information            |      |

| 24.6 Register descriptions                                 | 1228 |

| Chapter 25 FlexSPI                                         |      |

| 25.1 Chip-specific FlexSPI information                     |      |

| 25.2 Overview                                              |      |

| 25.3 Functional description                                |      |

| 25.4 External signals25.5 Initialization                   |      |

| 25.6 Application information                               |      |

| 20.0 / 17/110011110111101111011111111111111                | 1000 |

# Chapter 1 About this manual

#### 1.1 About This Document

### 1.1.1 Audience

This manual is intended for the board-level product designers and product software developers. This manual assumes that the reader has a background in computer engineering and/or software engineering and understands the concepts of the digital system design, microprocessor architecture, Input/Output (I/O) devices, industry standard communication, and device interface protocols.

# 1.1.2 Organization

This document is organized into two main sets of chapters.

- 1. First set covers the chip at a system level and provides an architectural overview. It also covers the system memory map, system-level interrupt events, clock, reset and system controller.

- 2. Chapters in the second set provides a technical description of individual modules along with chip-specific contents at the beginning of each chapter.

### 1.1.3 Suggested Reading

This section lists the additional resources that provide background for the information in this manual, as well as general information about the architecture.

#### 1.1.3.1 General Information

The following documentation provides useful background information about the Arm® Cortex® processor.

For information about the Arm Cortex processor see:

· http://infocenter.arm.com

Refer Security Primitives: Requirements in (I)IoT Systems document to familiarize with NXP's security nomenclature.

#### 1.1.3.2 Related Documentation

For a current list of documentation, refer to http://www.nxp.com.

#### 1.1.4 Conventions

This document uses the following notational conventions:

cleared / set When a bit has a value of zero, it is said to be cleared; when it has a value of one, it is said to be set.

mnemonics Instruction mnemonics are shown in lowercase bold.

italics Italics indicate variable command parameters, for example, bcctrx.

The book titles in the text are set in italics.

**15** An integer in decimal.

**0x** the prefix to denote a hexadecimal number.

**0b** The prefix to denote a binary number. Binary values of 0 and 1 are written without a prefix.

**n'H4000CA00** The n-bit hexadecimal number.

**BLK\_REG\_NAME** The register names are all uppercase. The block mnemonic is prepended with an underscore delimiter

**BLK\_REG[FIELD]** The fields within registers appear in brackets. For example, ESR[RLS] refers to the Receive Last Slot field of the ESAI Status Register.

**BLK\_REG[** *n***]** The bit number *n* within the BLK.REG register.

BLK\_REG[ /:r] The register bit ranges. The ranges are indicated by the left-most bit number / and the right-most bit

number r, separated by a colon (:). For example, ESR[15:0] refers to the lower half word in the ESAI

Status Register.

x, U In some contexts, such as signal encodings, an unitalicized x indicates a "don't care" or "uninitialized".

The binary value can be 1 or 0.

**x** An italicized x indicates an alphanumeric variable.

**n, m** Italicized *n or m* represent integer variables.

Binary logic operator NOT.

Binary logic operator AND.

Binary logic operator OR.

**^ or <O+>** Binary logic operator XOR. For example, A <O+> B.

Bit-wise OR. For example, 0b0001 | 0b1000 yields the value of 0b1001.

& Bit-wise AND. For example, 0b0001 and 0b1000 yields the value of 0b0000.

**{A,B}** Concatenation, where the *n*-bit value A is prepended to the *m*-bit value B to form an (n+m)-bit value. For

example, {0, REGm [14:0]} yields a 16-bit value with 0 in the most significant bit.

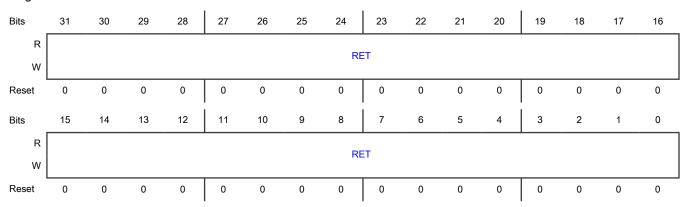

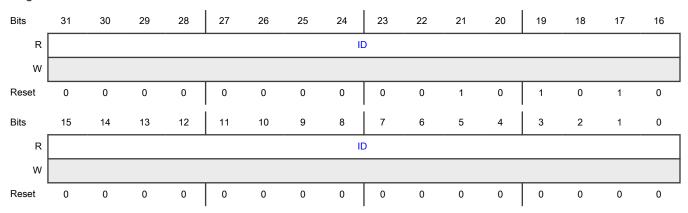

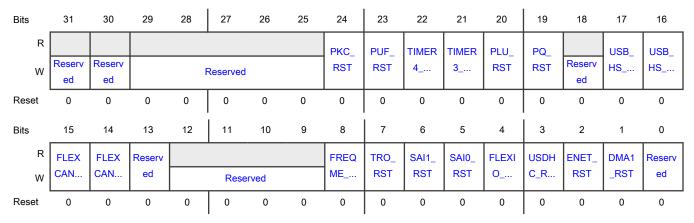

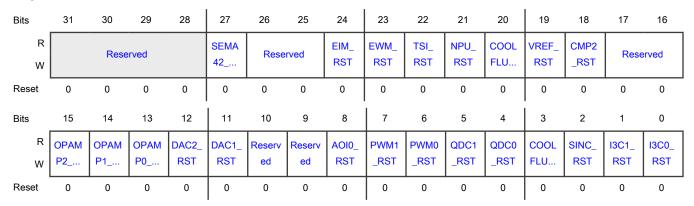

- or grey fill Indicates a reserved bit field in a register. Although these bits can be written to with ones or zeros, they

always read zeros.

Shift right logical one position.

Shift left logical one position.

<= Assignment.

== Compare equal.

!= Compare not equal.

> Greater than.

< Less than.

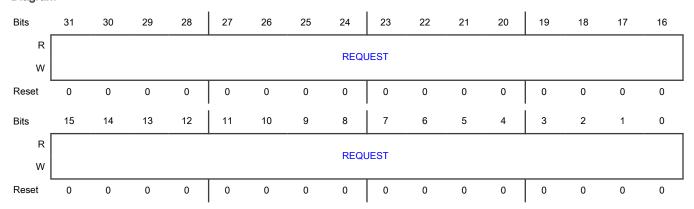

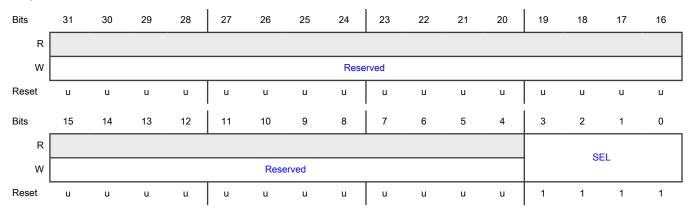

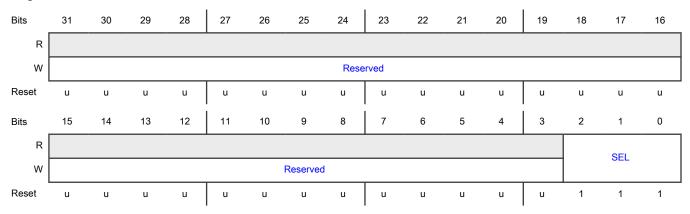

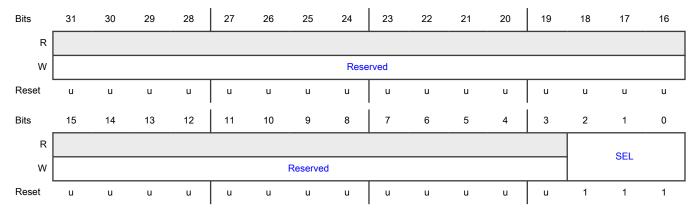

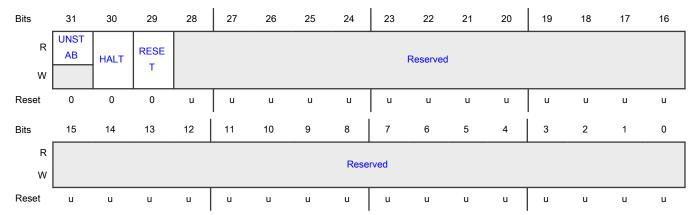

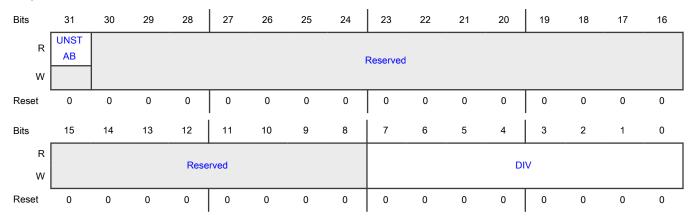

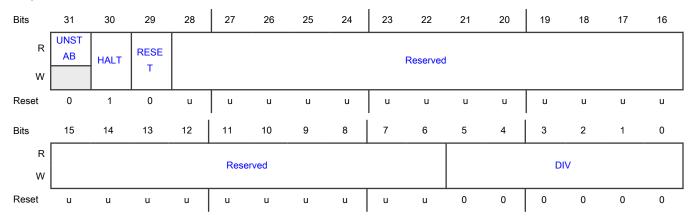

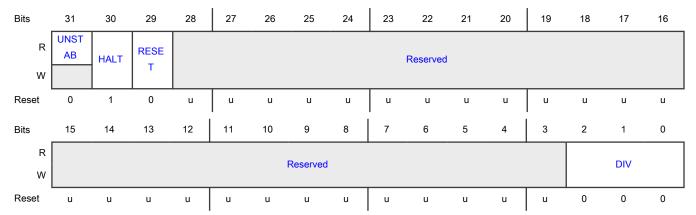

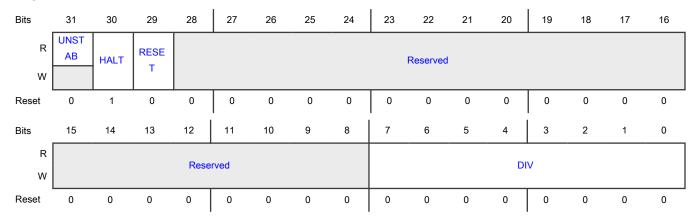

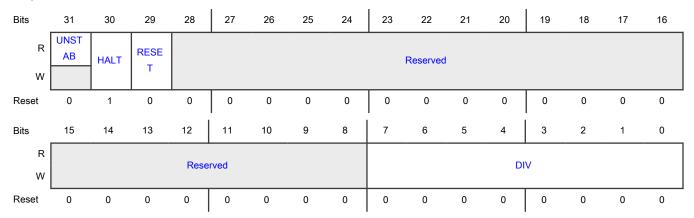

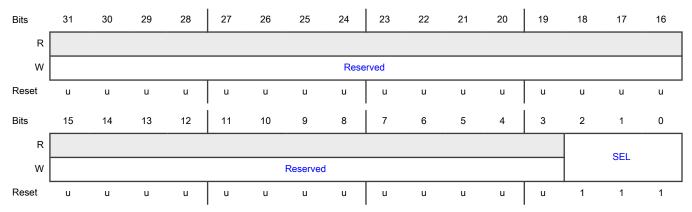

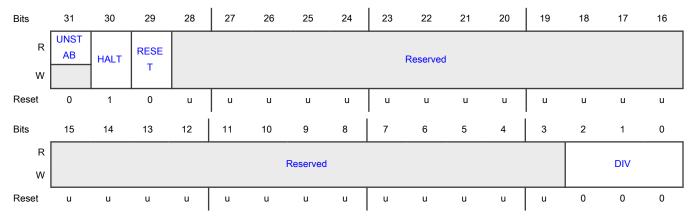

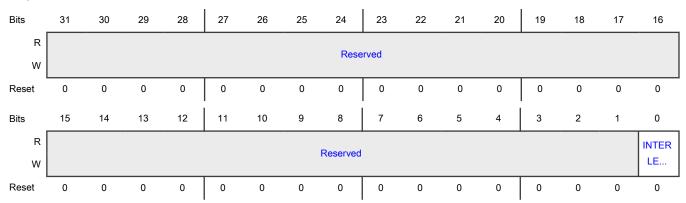

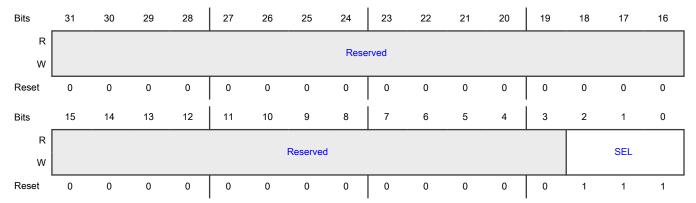

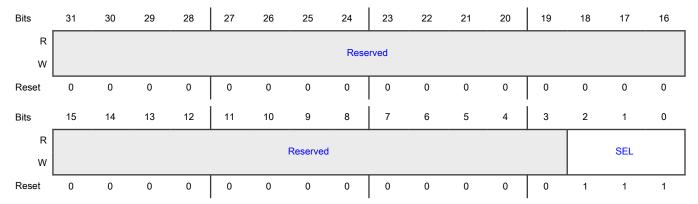

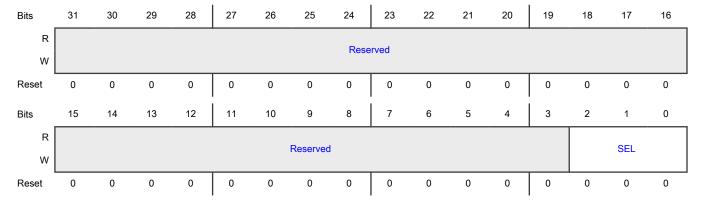

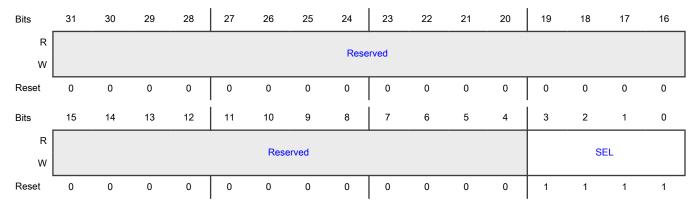

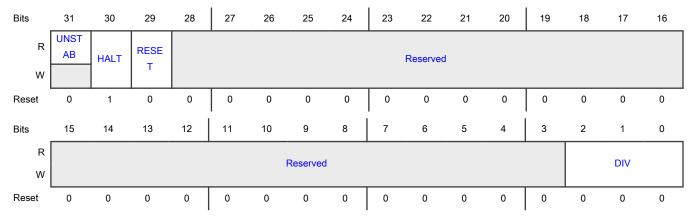

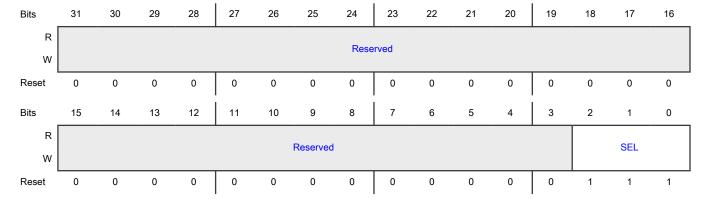

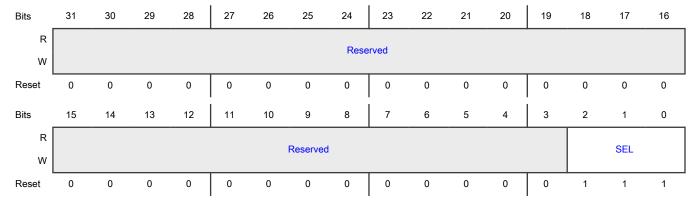

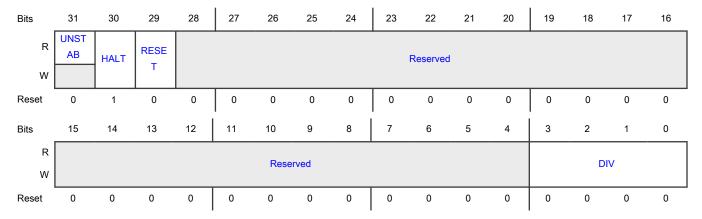

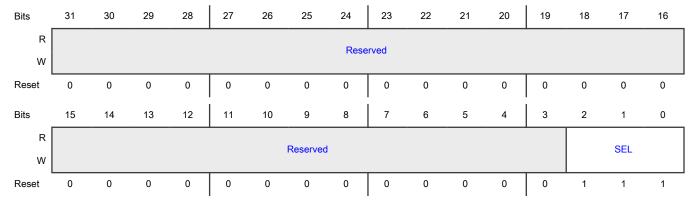

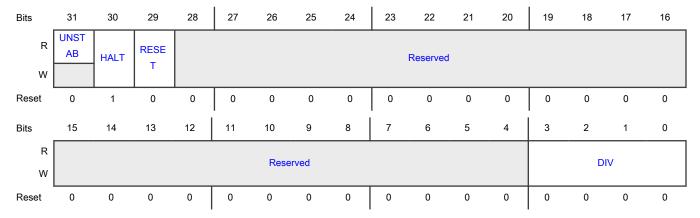

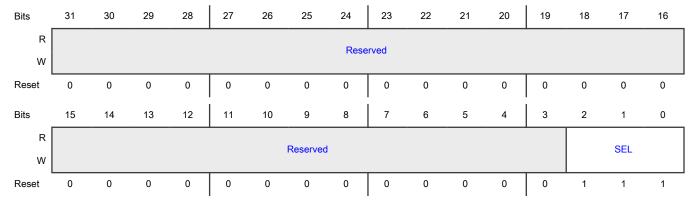

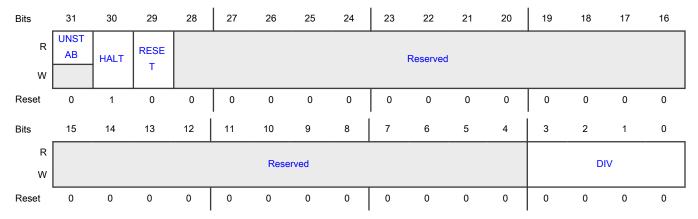

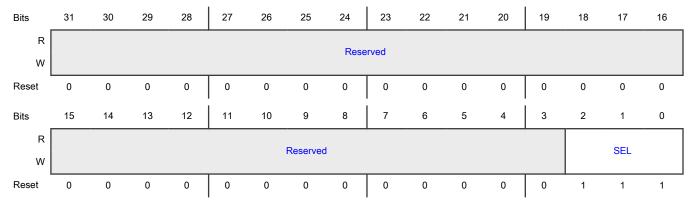

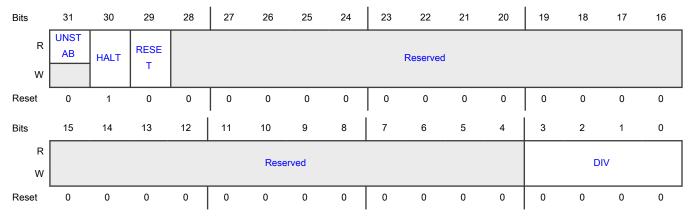

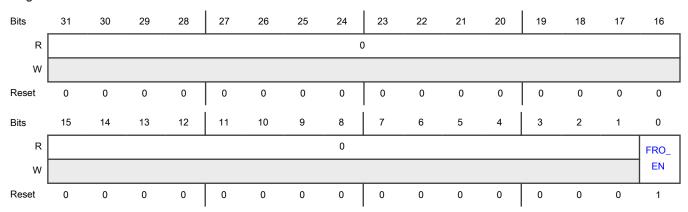

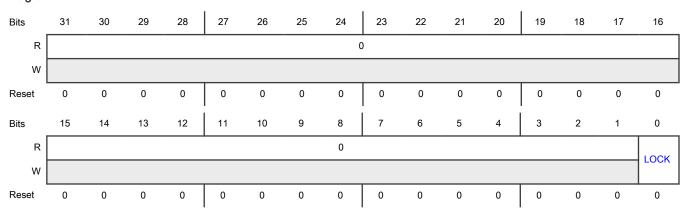

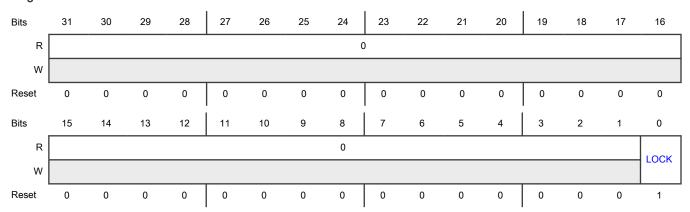

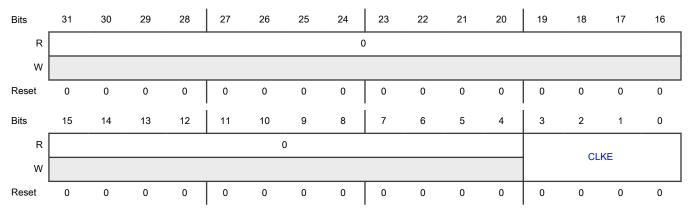

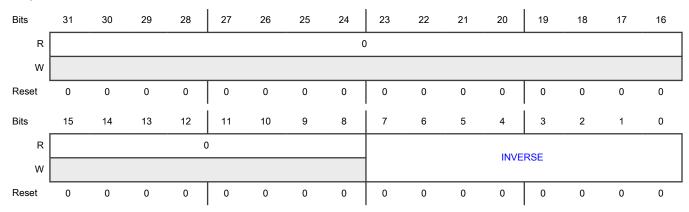

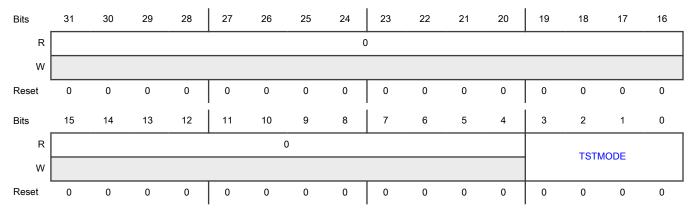

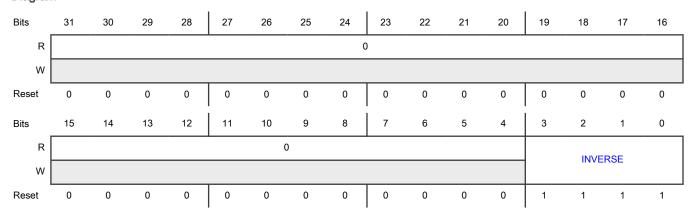

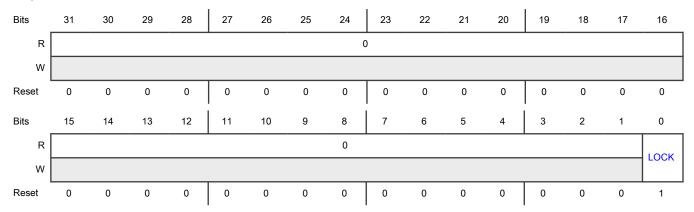

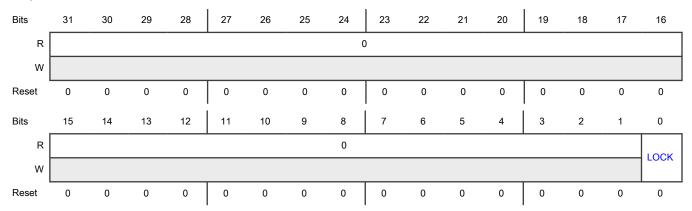

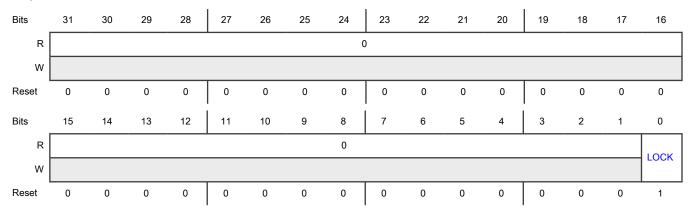

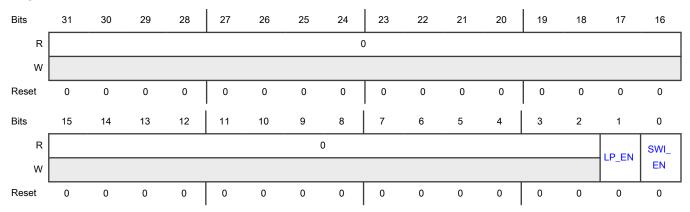

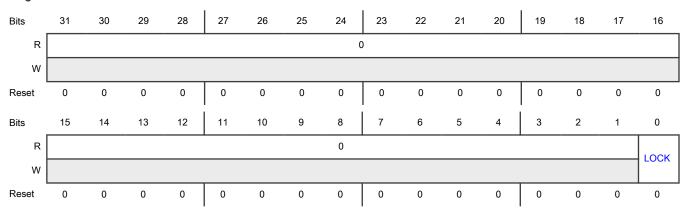

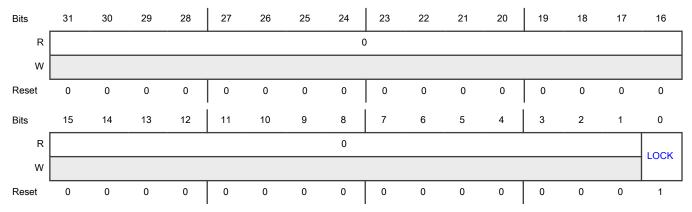

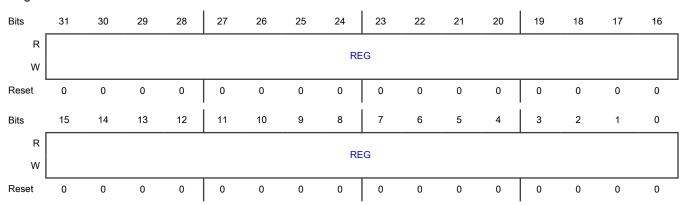

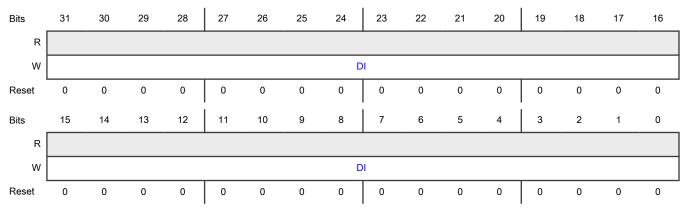

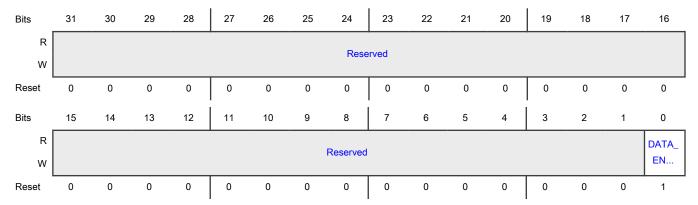

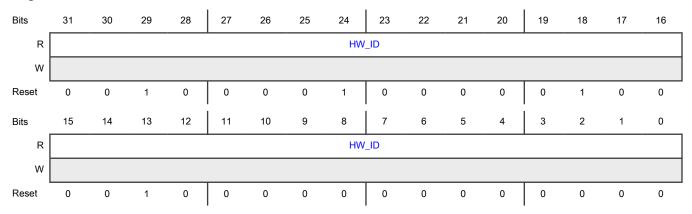

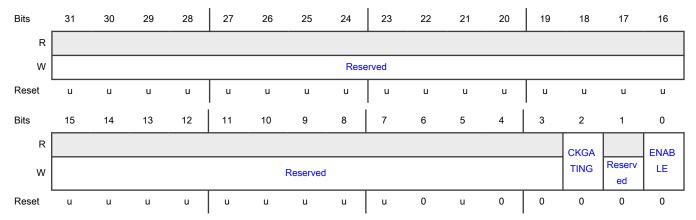

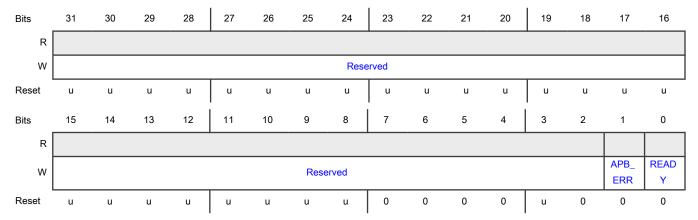

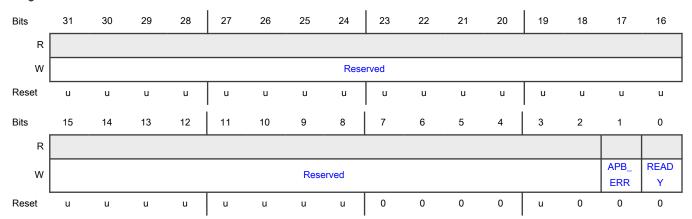

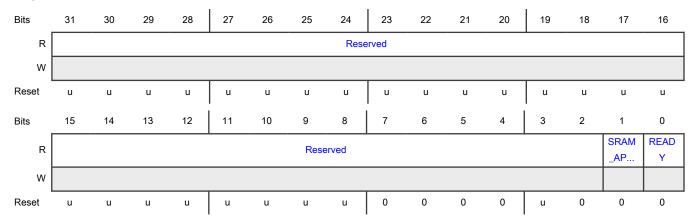

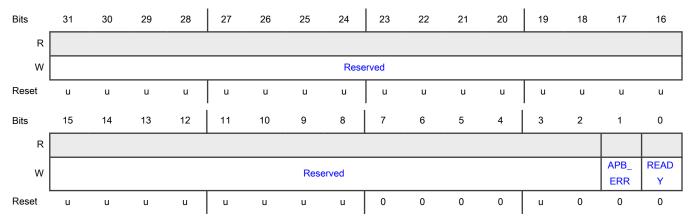

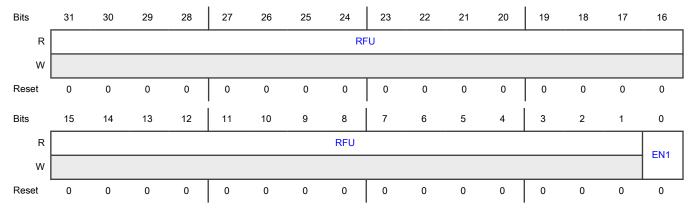

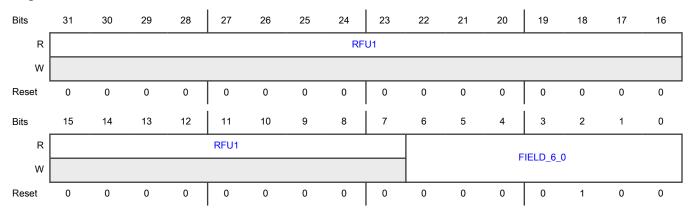

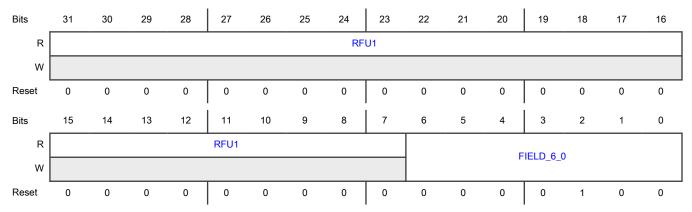

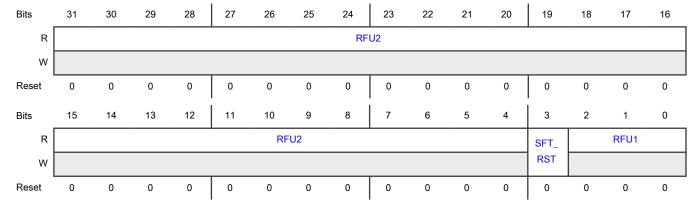

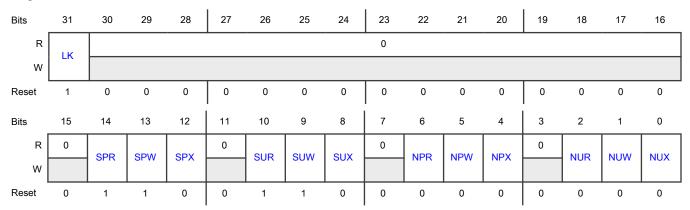

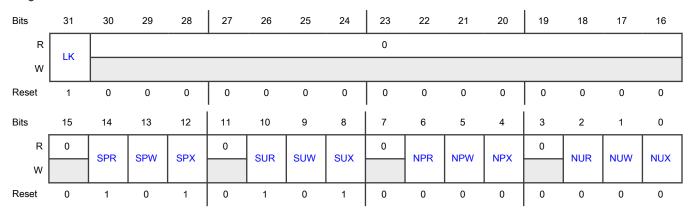

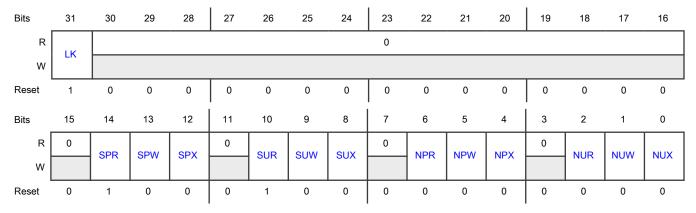

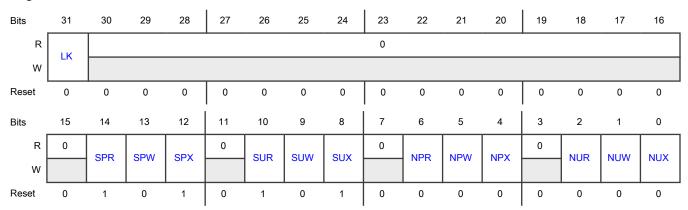

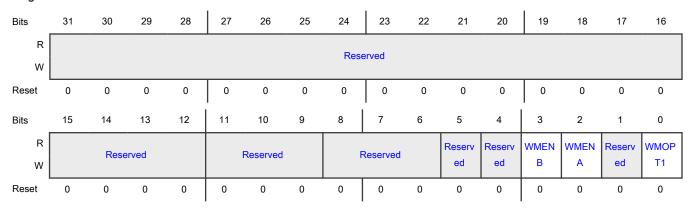

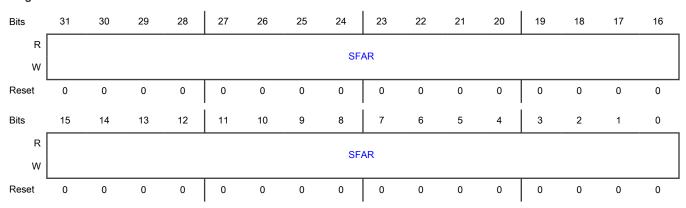

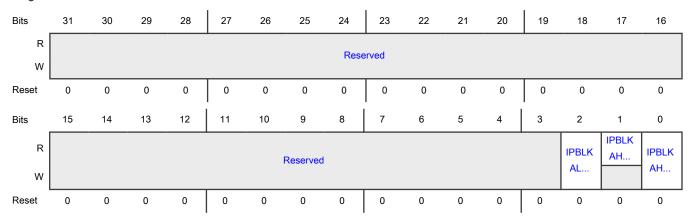

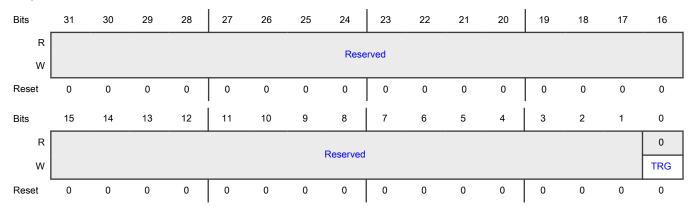

#### 1.1.5 Register Access

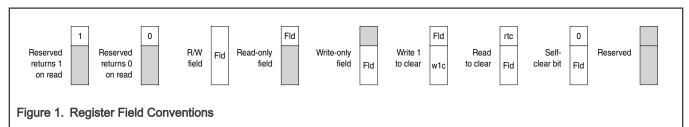

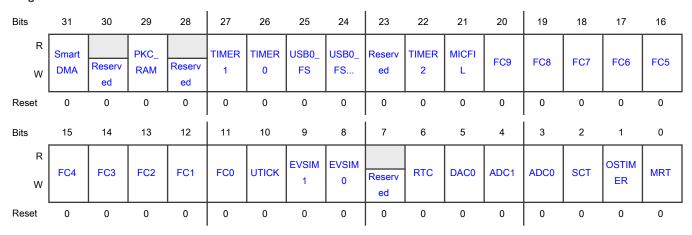

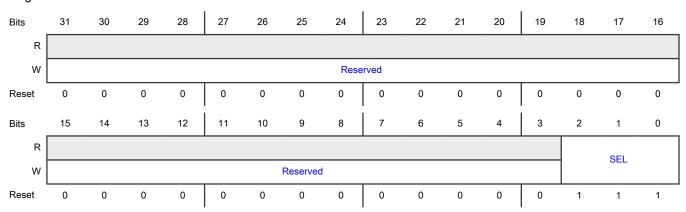

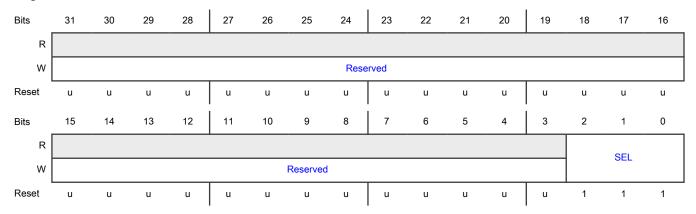

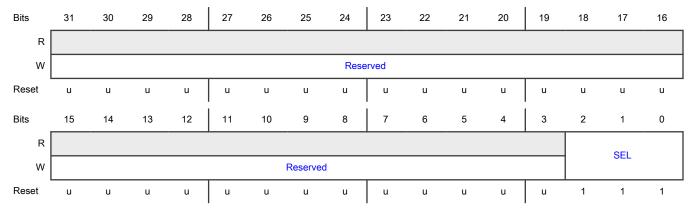

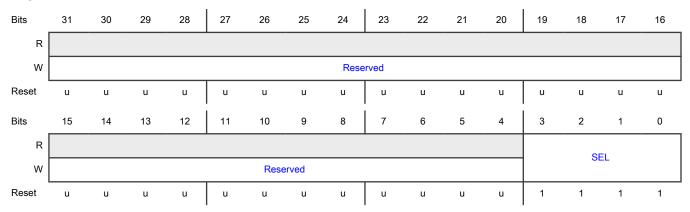

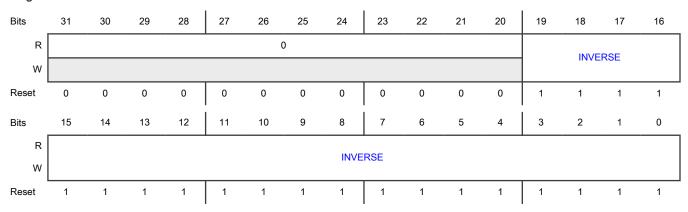

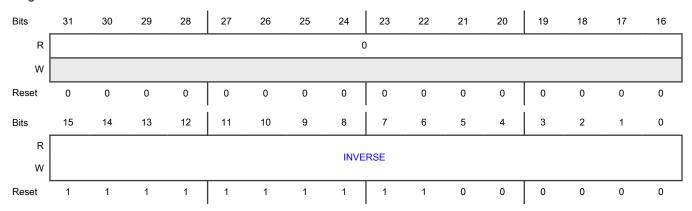

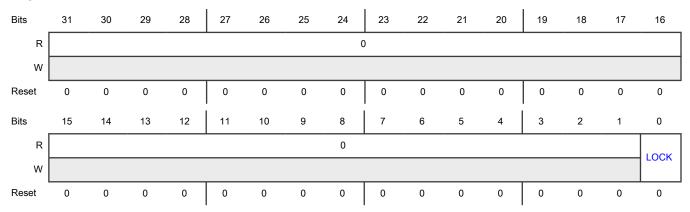

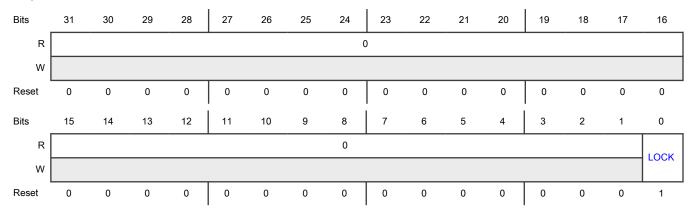

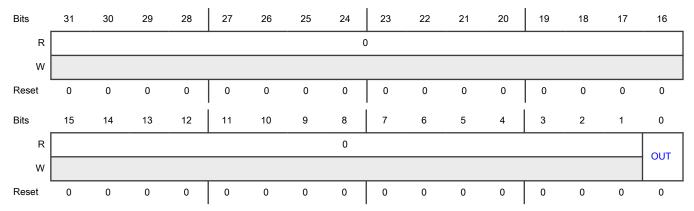

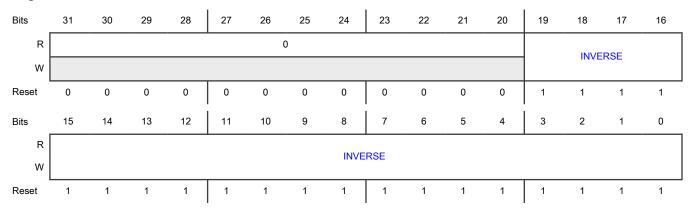

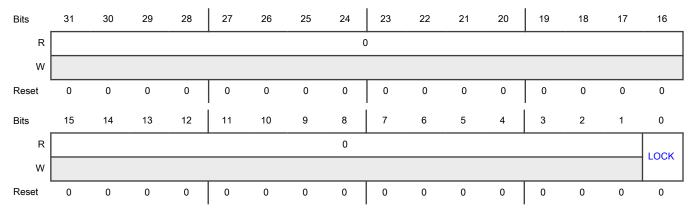

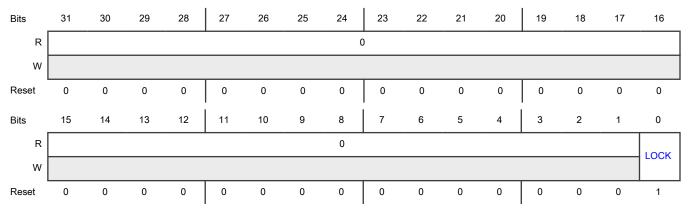

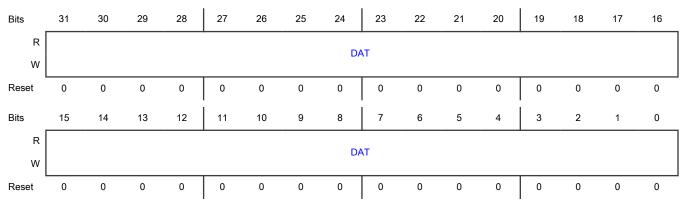

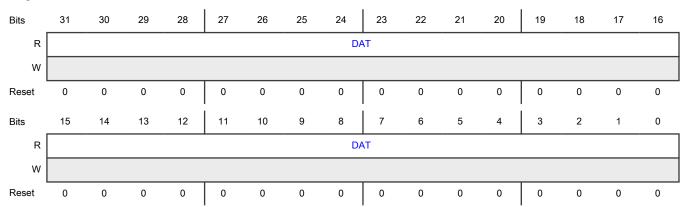

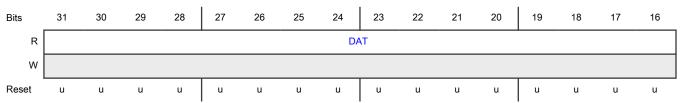

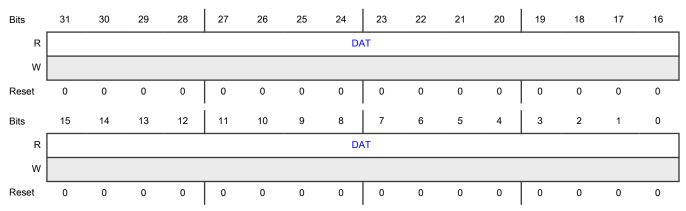

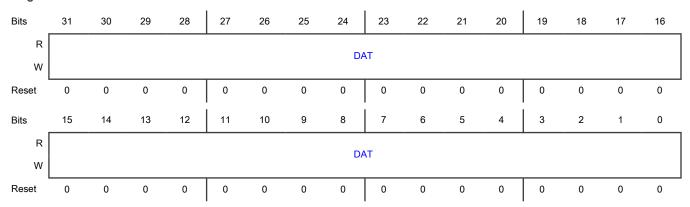

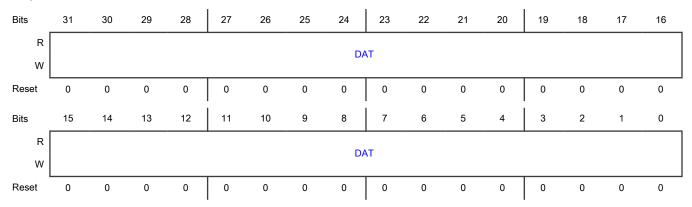

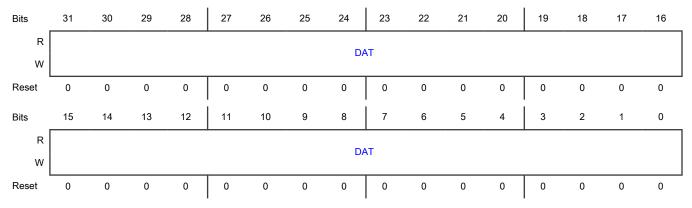

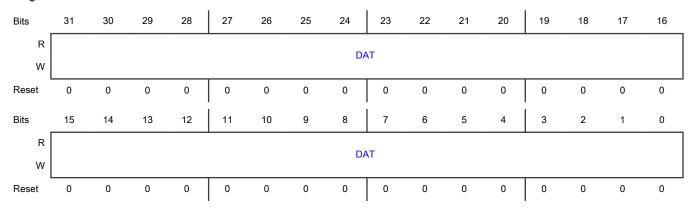

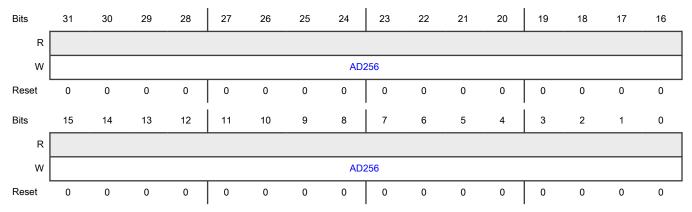

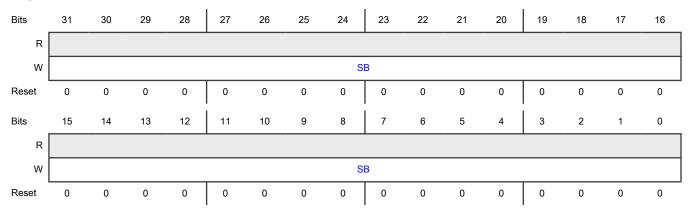

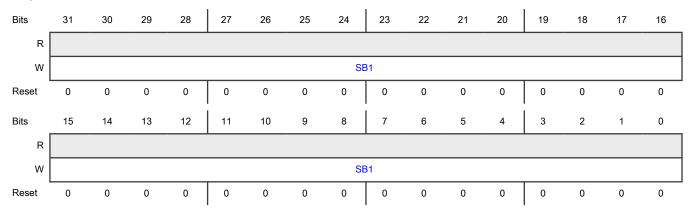

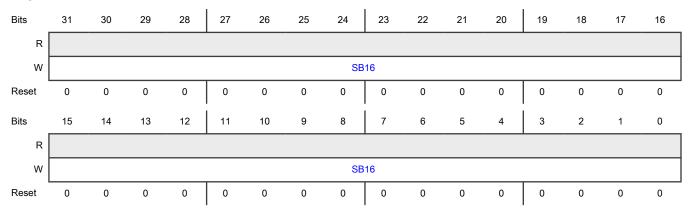

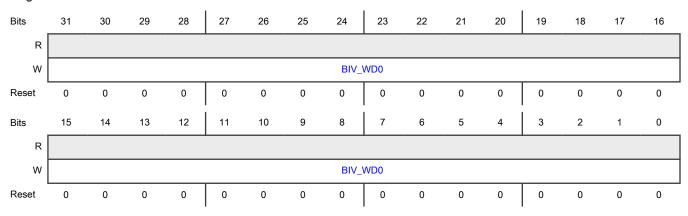

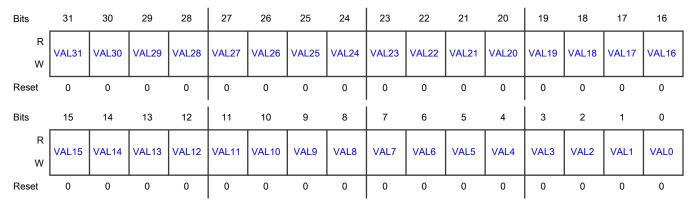

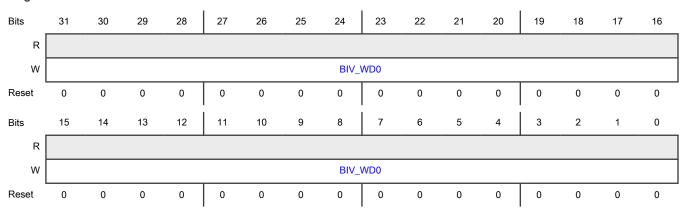

#### 1.1.5.1 Register Diagram Field Access Type Legend

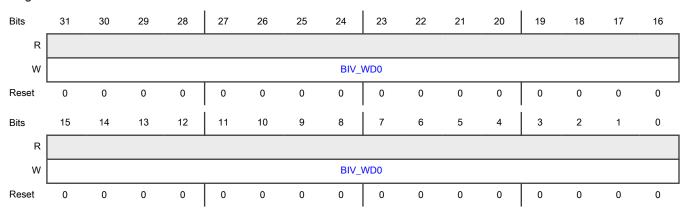

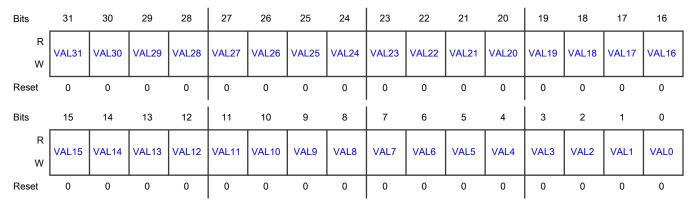

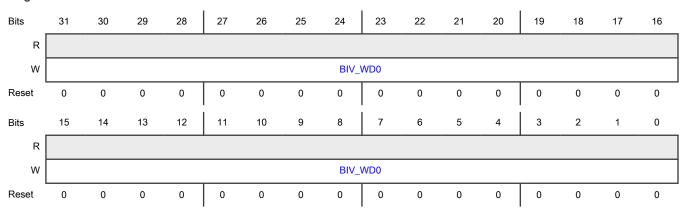

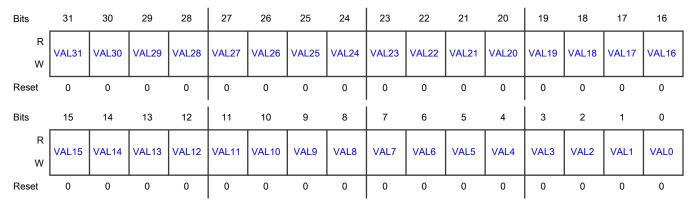

This figure provides the interpretation of the notation used in the register diagrams for a number of common field access types:

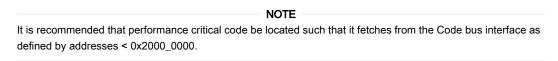

#### NOTE

For reserved register fields, the software should mask off the data in the field after a read (the software can't rely on the contents of data read from a reserved field) and always write all zeros.

#### 1.1.5.2 Register Macro Usage

A common operation is to update one field without disturbing the contents of the remaining fields in the register. Normally, this requires a read-modify-write (RMW) operation, where the CPU reads the register, modifies the target field, then writes the results back to the register. This is an expensive operation in terms of CPU cycles, because of the initial register read.

To address this issue, some hardware registers are implemented as a group, including registers that can be used to either set, clear, or toggle (SCT) individual bits of the primary register. When writing to an SCT register, all the bits set to 1 perform the associated operation on the primary register, while the bits set to 0 are not affected. The SCT registers always read back 0 and should be considered write-only. The SCT registers are not implemented if the primary register is read-only.

With this architecture, it is possible to update one or more fields using only register writes. First, all bits of the target fields are cleared by a write to the associated clear register, then the desired value of the target fields is written to the set register. This sequence of two writes is referred to as a clear-set (CS) operation.

A CS operation does have one potential drawback. Whenever a field is modified, the hardware sees a value of 0 before the final value is written. For most fields, passing through the 0 state is not a problem. Nonetheless, this behavior is something to consider when using a CS operation.

Also, a CS operation is not required for fields that are one-bit wide. While the CS operation works in this case, it is more efficient to simply set or clear the target bit (that is, one write instead of two). A simple set or clear operation is also atomic, while a CS operation is not.

Note that not all macros for set, clear, or toggle (SCT) are atomic. For registers that do not provide hardware support for this functionality, these macros are implemented as a sequence of read-modify-write operations. When an atomic operation is required, the developer should pay attention to this detail, because unexpected behavior might result if an interrupt occurs in the middle of the critical section comprising the update sequence.

A set of SCT registers is offered for registers in many modules on this device, as described in this manual. In a module memory map table, the suffix SET, CLR, or TOG is added to the base name of the register. For example, the CCM\_ANALOG\_PLL\_ARM register has three other registers called CCM\_ANALOG\_PLL\_ARM\_SET, CCM ANALOG PLL ARM CLR, and CCM ANALOG PLL ARM TOG.

In the sub-section that describes one of these sets of registers, a short-hand convention is used to denote that a register has the SCT register set. There is an italicized n appended to the end of the short register name. Using the above example, the name used for this register is CCM\_ANALOG\_PLL\_ARMn. When you see this designation, there is a SCT register set associated with the register, and you can verify this by checking it in the memory map table. The address offset for each of these registers is given in the form of the following example:

Address: 20C\_8000h base + 0h offset + (4d × i), where i=0d to 3d

In this example, the address for each of the base registers and their three SCT registers can be calculated as:

| Register               | Address   |

|------------------------|-----------|

| CCM_ANALOG_PLL_ARM     | 20C_8000h |

| CCM_ANALOG_PLL_ARM_SET | 20C_8004h |

| CCM_ANALOG_PLL_ARM_CLR | 20c_8008h |

| CCM_ANALOG_PLL_ARM_TOG | 20C_800Ch |

# Chapter 2 Introduction

#### 2.1 Overview

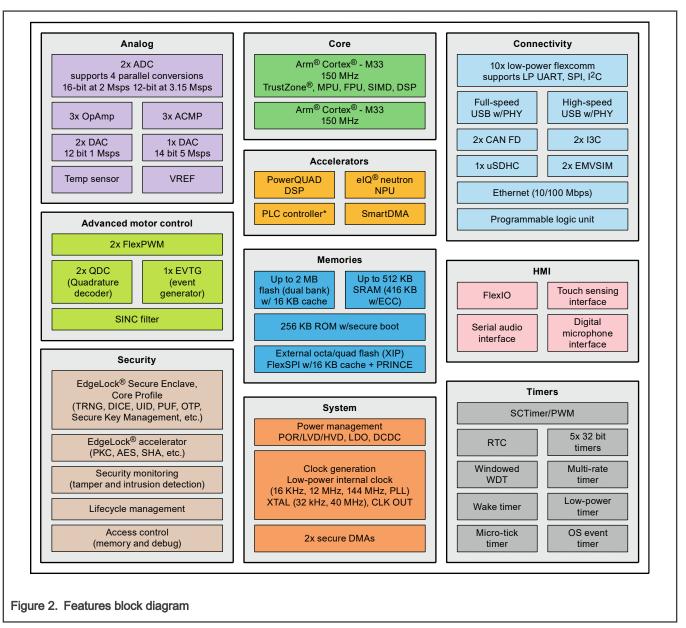

The MCX Nx4x series microcontrollers combine the Arm Cortex-M33 TrustZone® core with a CoolFlux BSP32, a PowerQuad DSP Co-processor, and multiple high-speed connectivity options running at 150 MHz. To support a wide variety of applications, the MCX N-series includes advanced serial peripherals, timers, high-precision analog, and state-of-the-art security features like secure user code, data, and communications. All MCX Nx4x products include dual-bank flash which supports read while write operation from internal flash. The MCX Nx4x series also supports large external serial memory configurations.

The MCX Nx4x are as follows:

- N54x: Mainstream MCU with a second M33 core, advanced timers, analog and high-speed connectivity (including Hi-Speed USB), 10/100 Ethernet, and FlexIO which can be programmed as an LCD controller.

- N94x: Integration CPU and DSP of serial connectivity, advanced timers, high precision analog, and high-speed connectivity

including Hi-Speed USB, CAN 2.0, 10/100 Ethernet, and FlexIO which can be programmed as an LCD controller.

The chip includes these key features:

Table 1. Key features

| Function            | Features                                                                                                              |

|---------------------|-----------------------------------------------------------------------------------------------------------------------|

| Security            | TrustZone for Armv8M                                                                                                  |

|                     | Secure boot, firmware update, and debug authentication using ROM                                                      |

|                     | EdgeLock® secure subsystem (ELS) S50                                                                                  |

|                     | Public-key cryptography (PKC)                                                                                         |

|                     | <ul> <li>External and internal flash memory interface with on-the-fly PRINCE decryption and<br/>encryption</li> </ul> |

|                     | Physically Unclonable Function (PUF) hardware options                                                                 |

|                     | Factory Root of Trust (RoT) programming                                                                               |

|                     | Tamper detection                                                                                                      |

|                     | Analog and digital glitch detection                                                                                   |

|                     | Code Watchdog (CDOG)                                                                                                  |

|                     | Intrusion and Tamper Response Controller (ITRC)                                                                       |

| Industrial strength | Industrial temperature rating                                                                                         |

|                     | Industrial communication protocol support (CAN-FD)                                                                    |

|                     | High-resolution mixed signal analog                                                                                   |

|                     | BLDC and PMSM motor control support                                                                                   |

|                     | <ul> <li>Integrated sensor interfaces: I3C, I2C, SPI, and UART</li> </ul>                                             |

|                     | 15-year longevity                                                                                                     |

|                     | Configurable RAM ECC                                                                                                  |

|                     | Ethernet (ENET) with QoS                                                                                              |

Table continues on the next page...

Reference Manual 10 / 1409

Table 1. Key features (continued)

| Function                        | Features                                                                                                                            |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Power-efficient operating modes | • Down to 57 µA/MHz (3.3 V, @25 ℃)                                                                                                  |

|                                 | • 170 μA in Deep Sleep mode (full 512 KB SRAM retention, 3.3 V, @25 °C)                                                             |

|                                 | <ul> <li>5.2 μA in Power Down mode (full 512 KB SRAM retention, 3.3 V, @25 °C)</li> </ul>                                           |

|                                 | <ul> <li>Down to 2.0 μA in Deep Power Down mode, 5.3 ms wake-up (RTC enabled 8 KB<br/>RAM and Reset pin enabled, @25 °C)</li> </ul> |

# 2.2 Target applications

The MCX Nx4x MCUs are ideal solutions for:

- Industrial

- Energy Storage and Management System

- Smart Metering

- Power Line Communication

- Factory Automation

- Industrial HMI

- Mobile Robotics Ecosystem

- Motion Control and Robotics

- Motor Drives

- Brushless DC Motor (BLDC) Control

- Permanent Magnet Synchronous Motor (PMSM)

- Edge AI/ML Anomaly Detection and Predictive Maintainence

- · Smart Home

- Home Control Panel

- Home Security and Surveillance

- Major Home Appliances

- Robotic Appliance

- Smart Speaker

- Soundbar

- Gaming Accessories

- Smart Lighting

- Smart Power Socket and Light Switch

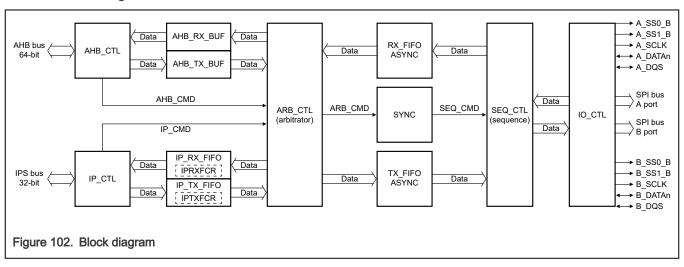

# 2.3 Block diagram

Figure 2 shows a top-level view of the modules within the chip, organized by functional category.

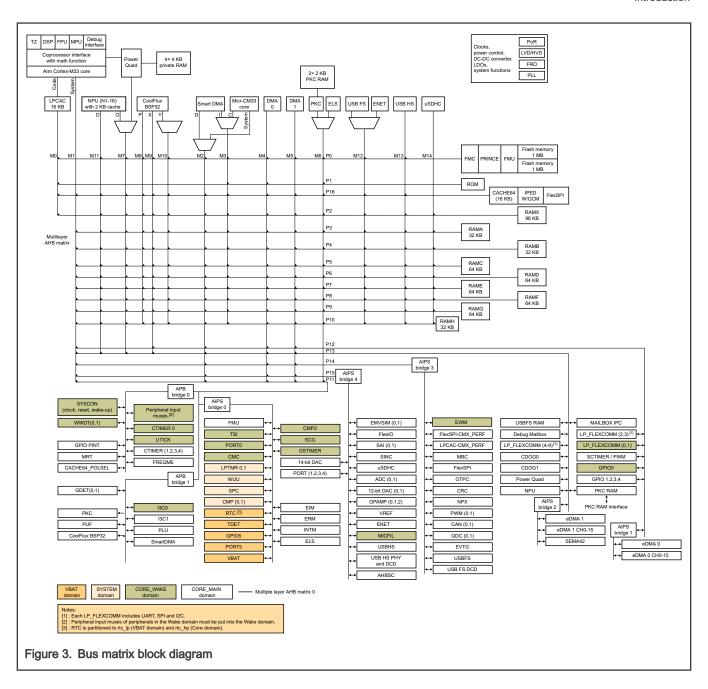

Figure 3 shows the chip's block diagram, including bus connections.

# 2.4 System bus priority and arbitration

As shown in Figure 3, this device includes a number of masters that can access the various slave ports. The multiple masters are attempting to access different slave ports. If multiple masters attempt an access to the same slave port at the same time then arbitration is required.

The SYSCON\_AHBMATPRIO register is where the programmable priorities for each of the master ports can be configured. Masters are assigned a priority value between zero and three with three being the highest priority. If two ports have the same priority, then the lowest port number is given priority.

There are some master ports that are shared between two masters. Where the port is shared, only one of the masters can have an active access at a time. The priority between two masters sharing a port uses a fixed arbitration scheme. The table below lists the master or masters for each of the ports. In the case where the port is shared, the high-priority master is specified:

Table 2. AHB bus matrix ports

| Master port | Master                                     | Accessible slave ports                 | Inaccessible slave ports | AHB ID |

|-------------|--------------------------------------------|----------------------------------------|--------------------------|--------|

| MO          | CPU0 (CM33) code bus                       | CPU0 (CM33) code bus P0 - P2 and P16   |                          | 0      |

| M1          | CPU0 (CM33) system bus                     | P3 - P16                               | P0 - P2                  | 1      |

| M2          | CPU1 (Micr-CM33) code bus (low-priority)   | P0 and P2 - P16                        | P1                       | 2      |

|             | SmartDMA data bus (high-priority)          |                                        |                          | 3      |

| M3          | CPU1 (Micr-CM33) system bus (low-priority) | P0 - P10 and P16                       | P11 - P15                | 4      |

|             | SmartDMA instruction bus (high-priority)   |                                        |                          | 5      |

| M4          | DMA0                                       | P0 - P16                               | None                     | 6      |

| M5          | DMA1                                       | P0 and P2 - P16                        | P1                       | 7      |

| M6          | PKC (low-priority)                         | P0 - P11 and P16                       | P12 - P15                | 8      |

|             | ELS (high-priority)                        |                                        |                          | 9      |

| M7          | PowerQuad (low-priority)                   | P0, P2 - P10, P13, and P16             | P1, P11 - P12, and P14   | 10     |

|             | NPU operand bus (high-priority)            |                                        | - P15                    | 11     |

| M8          | CoolFlux BSP32 program memory bus          | P0, P2 - P10, and P16                  | P1 and P11 - P15         | 12     |

| M9          | CoolFlux BSP32 X-data memory bus           | P0, P2 - P10, P12 - P13,<br>and P16    | P1, P11, and P14 - P15   | 13     |

| M10         | CoolFlux BSP32 Y-data memory bus           | P0, P2 - P10, and P16                  | P1 and P11 - P15         | 14     |

| M11         | NPU data bus                               | PU data bus P0, P2 - P10, P13, and P16 |                          | 16     |

| M12         | USBFS (low-priority)                       | P0, P2 - P10, and P16                  | P1 and P11 - P15         | 17     |

|             | Ethernet (high-priority)                   |                                        |                          | 18     |

| M13         | USBHS                                      | P0, P2 - P10, and P16                  | P1 and P11 - P15         | 19     |

| M14         | uSDHC                                      | P2 - P10                               | P0 - P1 and P11 - P16    | 20     |

# Chapter 3 Security Overview

#### 3.1 Disclaimer

As system security requirements and the attack surface evolves, it is important for customers to understand the types of attacks (especially advanced physical attacks) which NXP does not claim to protect against, or strongly mitigate, so that appropriate mitigation can be taken by the customer at the system level if necessary.

- This SoC has built-in security event detection features. However, NXP does not guarantee against advanced tamper

attempts, including operation of the device beyond the defined specification limits. NXP does not guarantee the protection

against semi-invasive and invasive attacks.

- This SoC has several built-in features addressing side channel attacks. However, there is no claim to be completely

resistant. The effectiveness of these features has not been independently evaluated. Therefore NXP does not guarantee

that the result will meet specific customer requirements.

- This SoC's security trust architecture relies on the strength of cryptographic algorithms and digital signatures. If these are subsequently determined to have inherent flaws, then the impact for each flaw must be evaluated and, in this case, NXP does not guarantee the underlying trust architecture claims.

- This SoC has some built-in access control mechanisms to support the logical separation of executed code. However, NXP

does not guarantee that the device completely ensures logical separation by itself. Any vulnerabilities identified in Trusted

Execution Environments or Hypervisor software may impact this separation and data integrity, and may require additional

mitigations.

NXP recommends customers to implement appropriate design and operating safeguards based on defined threat models, to minimize the security risks associated with their applications and products.

# 3.2 Overview

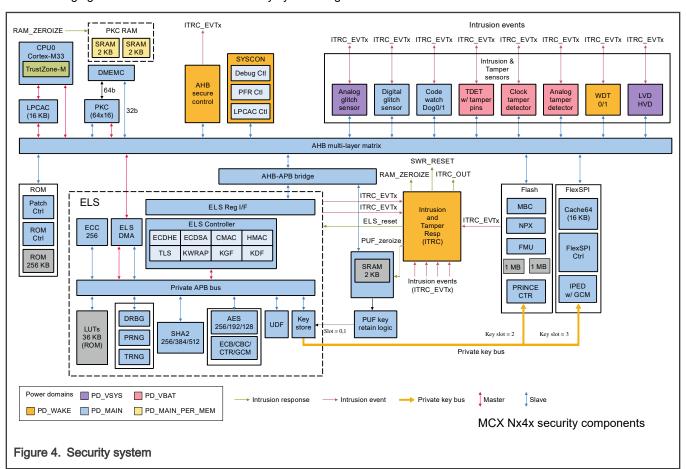

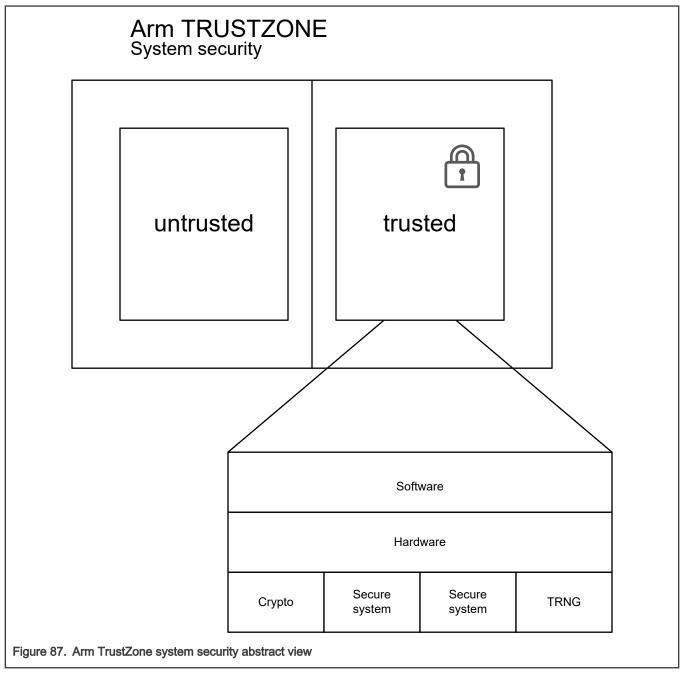

This chapter provides an overview of Platform Security features the device implements using following on-chip components.

- ELS security subsystem provides key isolation. It also includes random number generation functionality.

- Physically Unclonable Function (PUF) SRAM controller PUF

- PUF subsystem that stores the applications keys, which are provisioned to ELS S50 key store, securely.

- Public-key cryptography accelerator (PKC) PKC.

- OTP controller (OTPC) which supports loading and housing of EFUSE content into shadow registers.

- Code Watch Dog (CDOG) to ensure software integrity by detecting unexpected changes in the code execution flow.

- Intrusion and Tamper Response Controller (ITRC) to configure the response action for an intrusion event detected by an on-chip security sensors.

- Memory Block Checker (MBC) that provides read, write, and execute access control per block of internal flash memory.

- Digital tamper (TDET) to support tamper detection.

- · Secure AHB bus and AHB Controller to support secure trusted execution at the system level AHBSC.

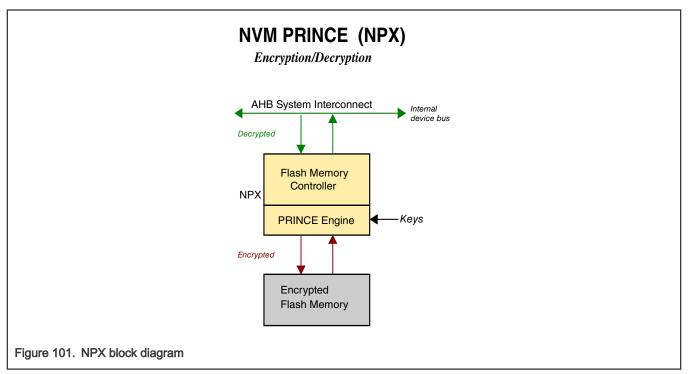

- PRINCE in CTR mode of operation to provide confidentiality protection of the content stored on internal flash.

- FlexSPI providing support of inline Prince Encryption Decryption (IPED) in GCM mode of operation.

- Digital and analog Glitch Detect (GDET) to provide power supply glitch detection.

- Cyclic Redundancy Check (CRC) that provides error detection for multi-bit errors. Refer the MCX Nx4x Reference Manual to see this chapter.

Reference Manual 15 / 1409

#### NOTE

The EdgeLock Secure Subsystem (ELS) is also known as EdgeLock Secure Enclave, Core Profile (ELE). This document uses the ELS name, but other materials might refer to this module as EdgeLock Secure Enclave, Core Profile or ELE.

The following figure shows the MCX Nx4x security system diagram:

#### 3.3 Immutable Root of Trust

As defined by Trusted Computing Group, "an Immutable Root of Trust (RoT) is expected to remain identical across all devices within a set of device models based on a defined threat model. It is also expected not to change across time and, therefore, will behave the same during each device's lifespan." It consists of truly immutable hardware logic, including analog and digital logic, read-only memory and one-time programmable memory. Immutable RoT is essential for guaranteeing any security feature, including Secure Boot, Secure Debug, Life-cycle Management, and a number of others. In this device, Immutable RoT is embedded in the Boot ROM (immutable bootloader). It uses the device hardware cryptographic functionality for its function.

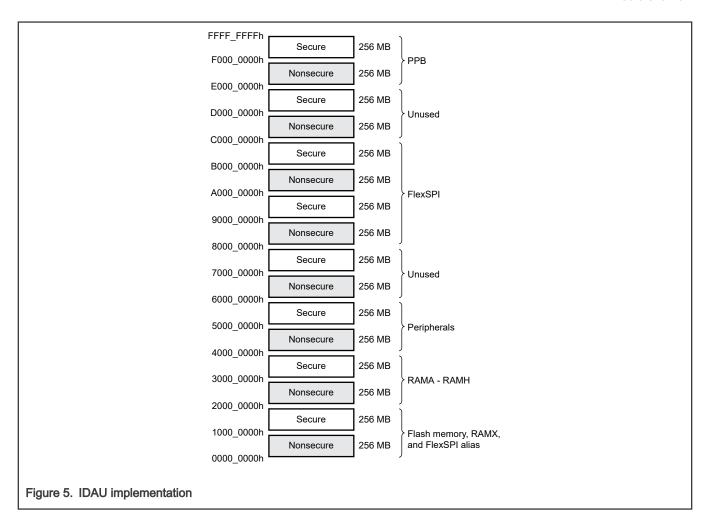

# 3.4 Life-cycle management

During its lifespan, a typical device finds itself in various places around the world. It is manufactured in a semiconductor factory, tested and packaged in silicon manufacturer facilities, sold to various distributors, sold further to the Original Equipment Manufacturer (OEM), assembled, tested and provisioned by their Contract Manufacturers and, finally, delivered to the endcustomer. In the case of failure, a device is returned to OEM or even back to the silicon manufacturer for further failure analysis.

Device life-cycle state is used to reflect the actual state of the device, which is further used to instruct the device on how exactly to protect the assets a device hosts during specific time. For example, when a device is being tested at a silicon manufacturer facility and no OEM or end-customer assets have been provisioned on it, then access to the device, in terms of debug or test, is less restrictive than when a device is with the end-customer.

Life-cycle state is monotonic, meaning it can only always be increased. Immutable RoT is in charge of life-cycle management and it enforces device access policies accordingly. Refer Life cycle states chapter in MCX Nx4x Security Reference Manual for details.

#### 3.5 Secure boot

Secure Boot ensures authenticity, integrity and confidentiality of the device bootloader, firmware, and other software during the boot process and ensures that the intended secure life-cycle state is reached. ECDSA P-256 with SHA-256 or ECDSA P-384 with SHA-384 are there to guarantee authenticity and integrity of the firmware image. PRINCE-based memory encryption using a device-unique key derived from PUF can be used to provide code/data confidentiality while the firmware image is stored in internal or external FLASH. Immutable RoT is in charge of enforcing Secure Boot and it does so according to the policies defined by the life-cycle state.

Refer Overview chapter for details. Also see "NPX submodule" section in the Flash controller chapter and PRINCE IP GCM function support section in the FlexSPI chapter.

# 3.6 Secure update

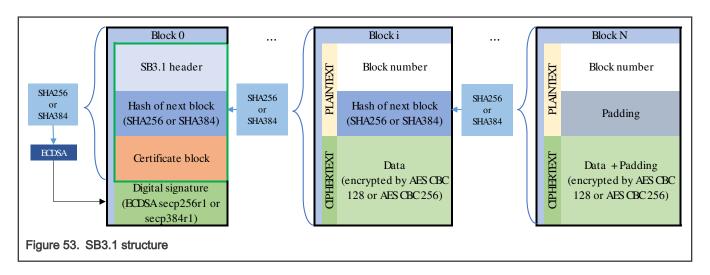

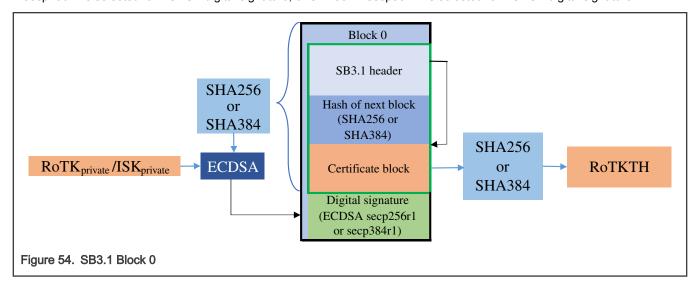

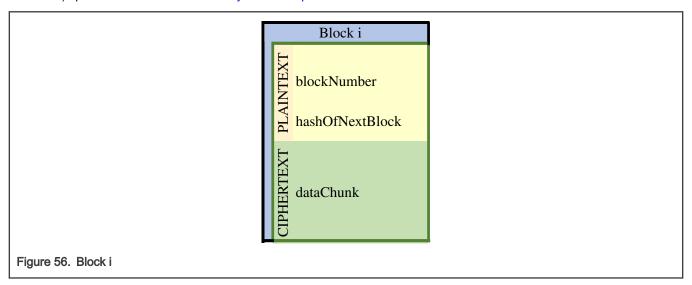

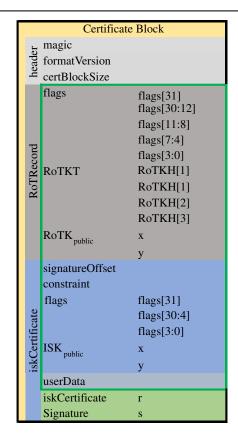

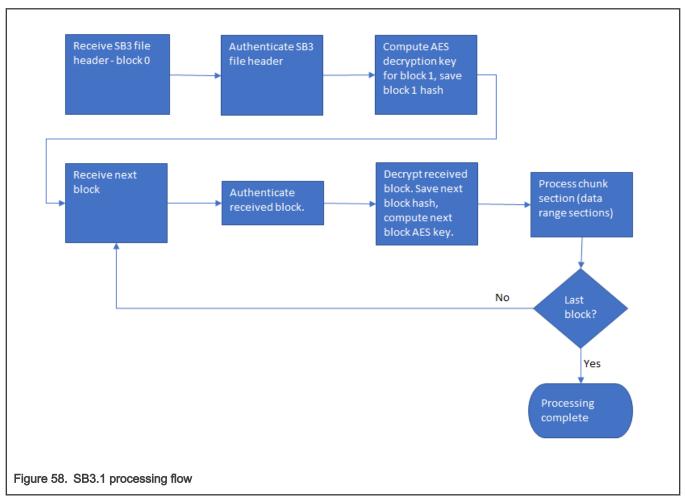

Secure Update is the process used to securely update the firmware image in the field. The firmware image is encrypted using AES-128 or AES-256 and signed using ECDSA P-256 or ECDSA P-384, following the SB3.1 firmware image format. Secure Update guarantees authenticity and confidentiality of the new image. It also ensures that the new image is up-to-date, preventing the rollback to an older image. Running firmware is in charge of receiving and verifying the new firmware image. The follow-up Secure Boot verifies the new firmware image again, making sure the Immutable RoT is still in charge of ensuring authenticity of the latest firmware.

Refer Overview chapter for details.

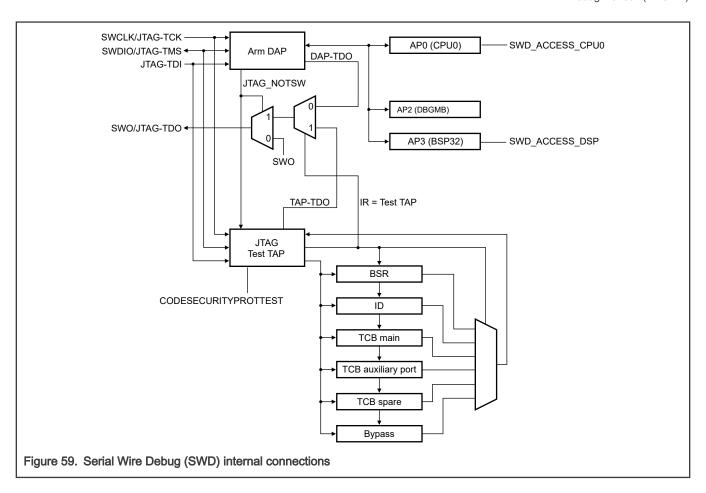

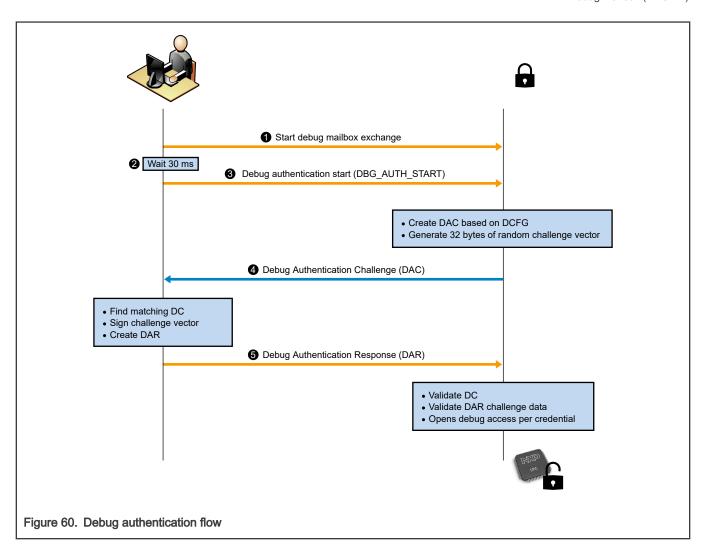

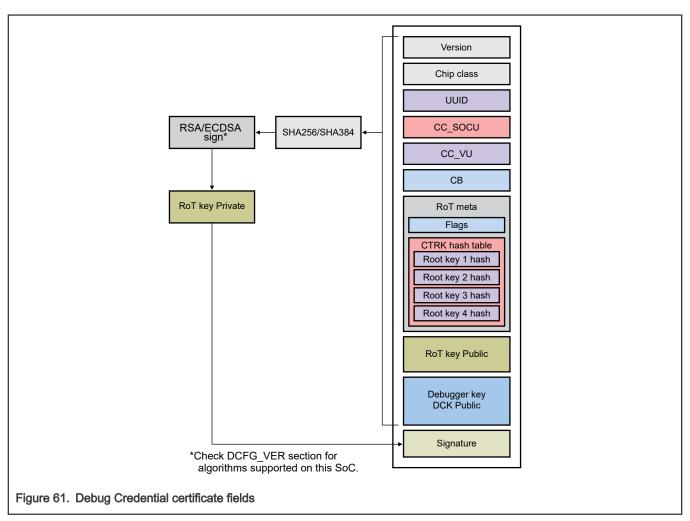

# 3.7 Secure debug

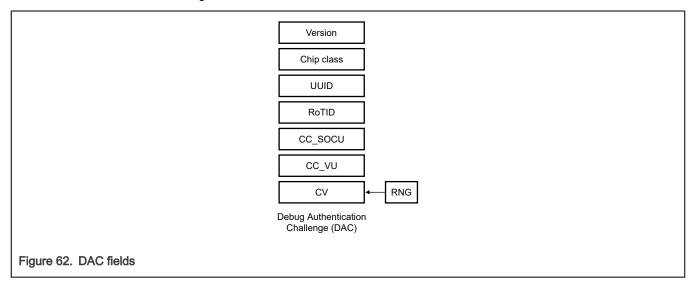

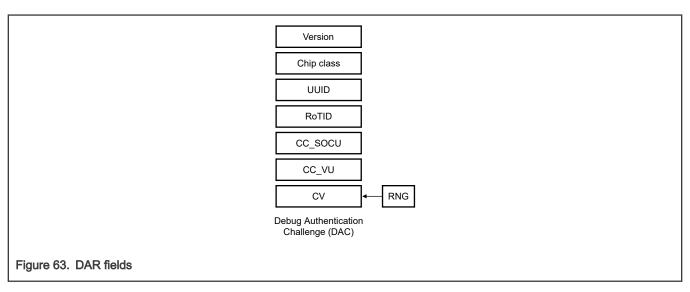

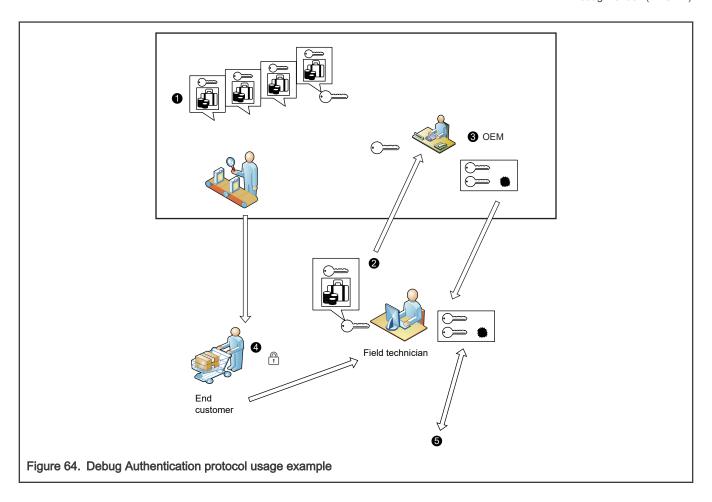

Secure Debug is the process used to securely access debug, following the policy defined by the life-cycle state. When a debugger wants to debug a device, they indicate that through a so-called debug mailbox and initiate reset. During boot, a device is checking the debug mailbox and starting a full asymmetric-key crypto based challenge-response protocol. A 128-bit random challenge is issued by the device and signed by a debugger. The response is then verified by the device and, if successful, debug is allowed. Immutable RoT is in charge of the whole process.

Refer Debug mailbox chapter for details.

### 3.8 IP protection

IP Protection is a set of mechanisms used to protect confidentiality and integrity of valuable code and data stored on the device. During Secure Update, the firmware image is encrypted using AES. While at rest and during Secure Boot, the firmware image is encrypted using PRINCE. Data or code stored in internal or external memory is encrypted using PRINCE as well. PRINCE encryption is done using a device-unique key, which is derived from PUF by the Immutable RoT. Up to 4 independent memory regions of internal FLASH and up to 4 independent memory regions of external FLASH can be used for protecting IP content from various vendors.

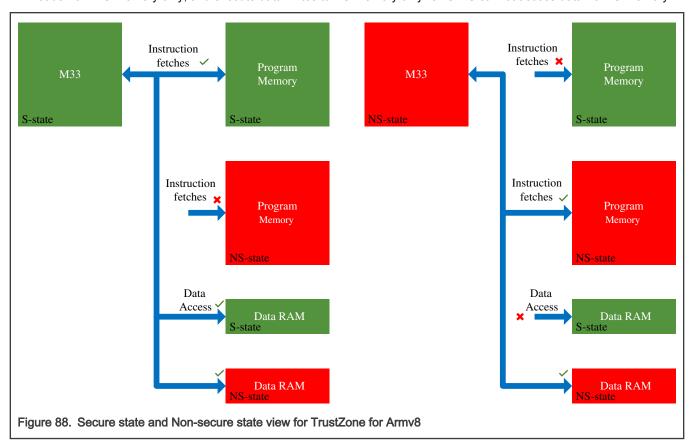

#### 3.9 Secure isolation

Arm TrustZone enables Secure Isolation during run-time by providing four distinct levels of privilege: secure-privilege, secure-user, non-secure-privilege, non-secure-user. Every peripheral is equipped with Peripheral Protection Checker (PPC) that can be programmed to control access to that peripheral, following the Arm TrustZone philosophy. Every memory is equipped with Memory Protection Checker (MPC) that can also be programmed in the same way as the PPC. Secure AHB Controller is in charge of programming all PPC and MPC blocks and only the highest level of privilege, which is secure-privilege, is allowed to do that.

As highlighted by the mechanisms we use for IP Protection, PRINCE-based memory encryption also ensures Secure Isolation between multiple IP vendors. Initial Vector (IV) is derived by secure-privilege and a different value is used for every independent memory region, ensuring the isolation between each other.

#### 3.10 Secure attestation

Secure Attestation is a set of mechanisms used to provide evidence to a remote party on the device's genuine identity, its software and firmware versions, as well as its integrity and lifecycle state. Device Identity Composition Engine (DICE), as defined by Trusted Computing Group, uses Immutable RoT during boot time to create a unique Device Identity which takes into account Unique Device Secret (UDS), hardware state of the device and its firmware. The DICE feature is implemented using the ELS Runtime Fingerprint (RTF) in this device. RTF is the NXP-proprietary attestation mechanism, which measures the device's state during boot-time and run-time as well.

# 3.11 Secure storage

Immutable RoT, including PUF as the source of device-unique master key, is in charge of key derivation and key management. RFC3394 using device-unique key wrapping key is used as a method for securely storing keys. AES GCM using device-unique keys is used for securely storing valuable data. PRINCE memory encryption using device-unique key is used for storing valuable code in internal and external FLASH.

# 3.12 Trust provisioning

Trust provisioning is a process used for creation of initial Device Identity keys. Its major objective is to provide a cryptographic proof of the device's origin and to offer a set of tools to OEM for secure provisioning of their own assets. In a nutshell, a device-unique private-public key pair is created on every device, the public portion of which is collected and signed by NXP. That signed public key is installed back onto every device in a form of device-unique certificate, which serves as the actual proof of the device's origin. The corresponding private key, together with other pre-installed key material, is then used for authentication and secure connection to the device, enabling secure provisioning of OEM assets even in a manufacturing environment OEM may not fully trust.

# 3.13 Secure key management

Secure key management is a process of securing valuable keys and various key material which are essential in maintaining security of the end-user, OEM and NXP assets. The process strongly relies on the Immutable RoT consisting of PUF, hardware logic and ROM. A device-unique master key is provided by PUF and only used for further key derivation. Part of the derivation data is supplied by the Immutable RoT, accurately reflecting the device's state, making sure different keys are derived in different states. For example, different life-cycle state will often yield a different derived key. Similarly, when the debug port is open a different key will be derived than when the debug port is closed. All the platform keys reside within a security subsystem, hidden from the application core at all times.

Refer Overview chapter for details.

# 3.14 Anomaly Detection and Reaction

Anomaly Detection and Reaction describes the processes or algorithms that analyze the device input and output such as sensor data, as well as the software integrity and application operation for abnormal events and, if required, trigger and execute an action. Typically these actions encompass logging the anomaly, issuing a message to the cloud backend, resetting the device, and/or changing a life cycle state.

# Chapter 4 Core Overview

#### 4.1 Introduction

This section covers the core modules included in this chip.

|   | NOTE                                                                                                                                                                                          |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| • | repeated in the MCX Nx4x Reference Manual, with differences only in the Peripheral Bridge in Peripheral Bridge (PBRG). The sections in the Reference Manual does not show the security in it. |

|   | NOTE  IFR and PFR refer to "Protected Flash Regions" in this document.                                                                                                                        |

# 4.2 CPU0 and CPU1 Cortex-M33 Code and System buses

CPU0 is the primary Cortex-M33 (ver r0p4-00rel0) processor, which supports TrustZone-M, Floating Point Unit (FPU), and Memory Protection Unit (MPU).

The MCX Nx4x device also includes a second instance of Cortex-M33, CPU1, which is the secondary Mirco-CM33 intended to offload the main processor to support special dedicated applications. The configuration of this instance does not include MPU, FPU, DSP, ETM, Trustzone-M, Secure Attribution Unit (SAU) or co-processor interface. SYSTICK is supported on both cores.

Cortex-M33 implements a modified Harvard memory architecture using two 32-bit bus interfaces: the Code and System buses. The bus interfaces are activated by address range and can include both instruction fetches and operand data references on a given bus port. (A traditional Harvard architecture strictly separates instruction fetches and operand data references onto specific bus ports regardless of access address.) The Code bus is typically used for instruction fetching and data accesses of PC-relative data, while the system bus is typically used for operand data references to the on-chip and off-chip memories and peripheral accesses. The bus structure fully supports concurrent instruction fetch and data accesses, but the Cortex-M33 implementations can generate both types of references on each bus.

#### 4.2.1 Code Bus access

CPU0 and CPU1 code bus can access memory as shown in the "Bus matrix block diagram", shown in the MCX Nx4x Reference Manual. CPU0 code bus access is routed to Low Power Cache (LPCAC) controller. This controller then processes the cacheable accesses as needed, while bypassing the non-cacheable accesses or forwarding the cache write-through and cache miss accesses to the downstream memories through the master port of this cache controller.

#### 4.2.2 System bus access

All System bus accesses are routed to the target address in destination memories through multilayer AHB matrix slave port. See "Bus matrix block diagram" in the MCX Nx4x Reference Manual.

#### 4.2.3 Access control

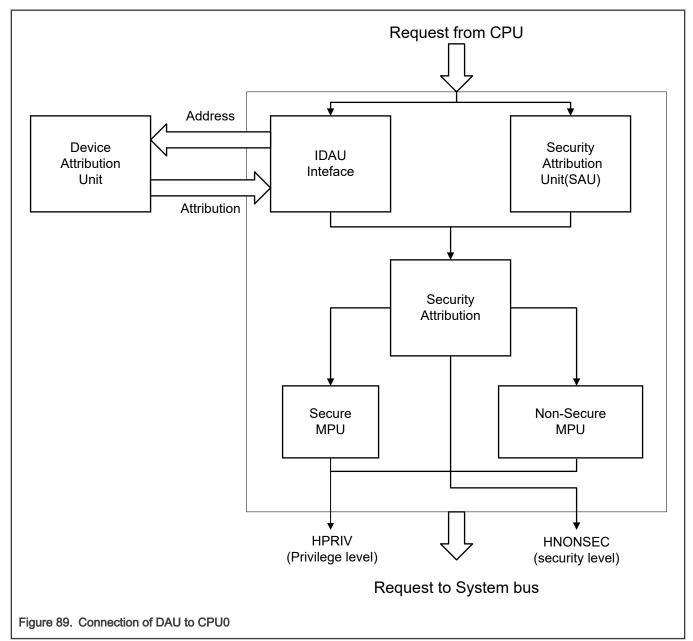

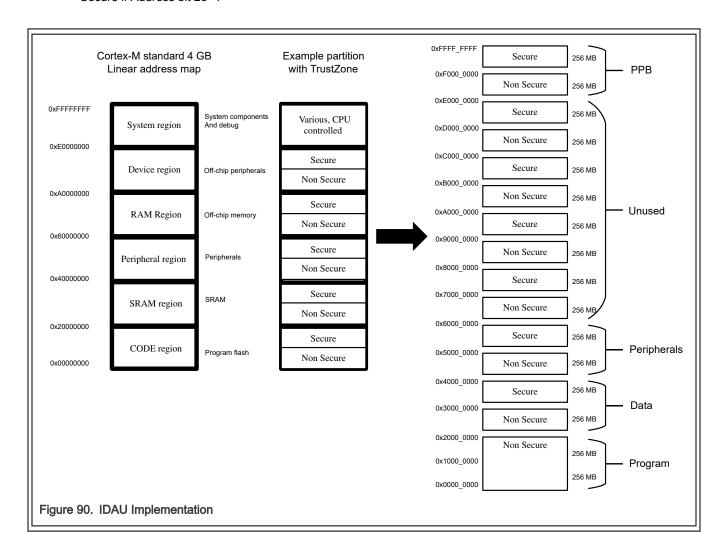

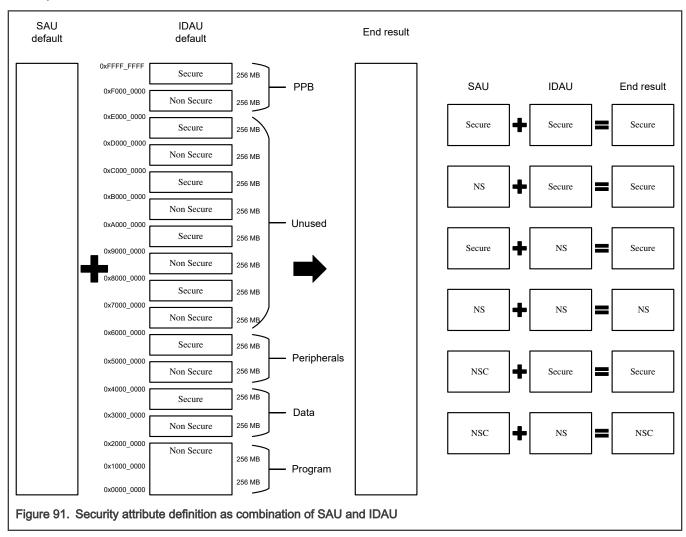

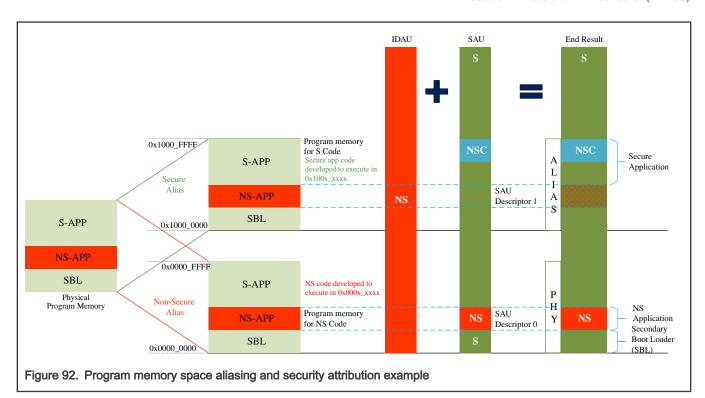

CPU0 Code and System Bus accesses are checked by the core access control logic, that is, IDAU/SAU and MPU. All requests that miss or bypass the cache are checked by downstream secure AHB bus logic. The caches include protection control signals (HPROT[3:0], which is defined in Arm AHB protocol) and processing domain bits as part of the tags. If a fetch address hits the cache but the protection control and/or domain bits are different, the cache controller forces a miss with the allocate location the

Reference Manual 19 / 1409

same as the address hit location in the cache. This policy allows all the downstream checks to take place, and this new miss is loaded in the cache with the updated protection control and domain bits overwriting the line with the same address. This keeps the cache coherent while always checking accesses that need to see the downstream checks.

CPU1 access is controlled by secure AHB control.

Read, write, and execute access control to on-chip flash is controlled by Memory Block Checker (MBC). See MBC chapter in MCX Nx4x Security Reference Manual.

# 4.3 Nested Vectored Interrupt Controller (NVIC)

### 4.3.1 Interrupt priority levels

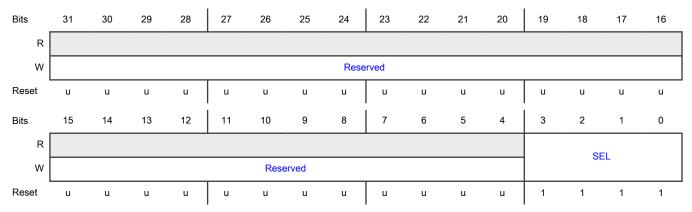

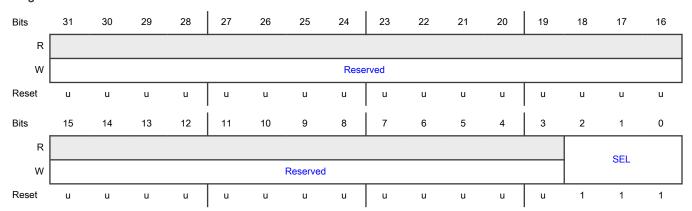

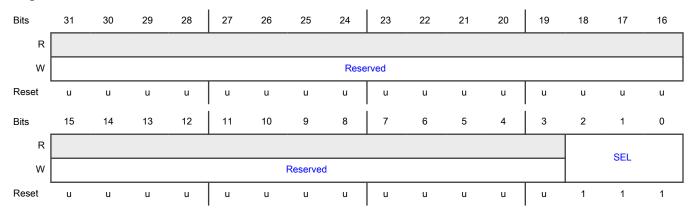

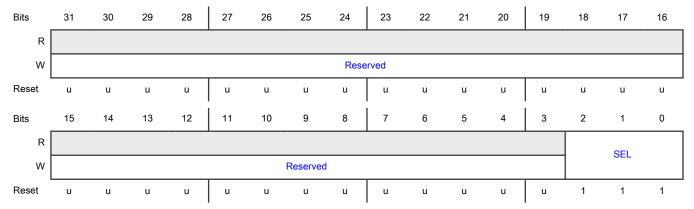

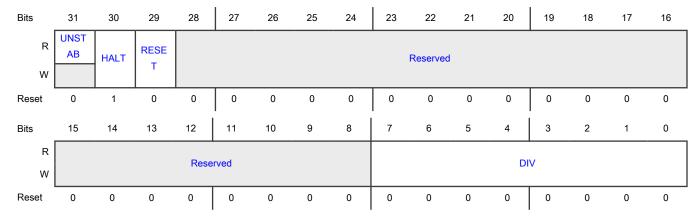

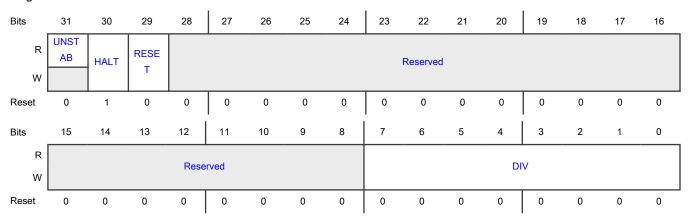

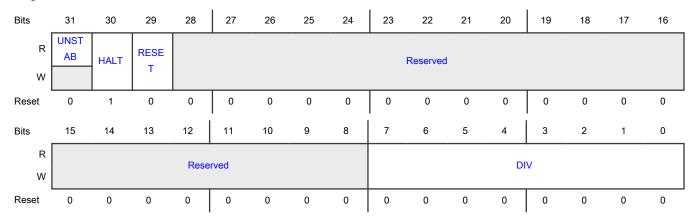

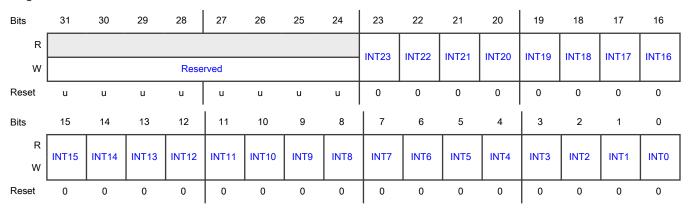

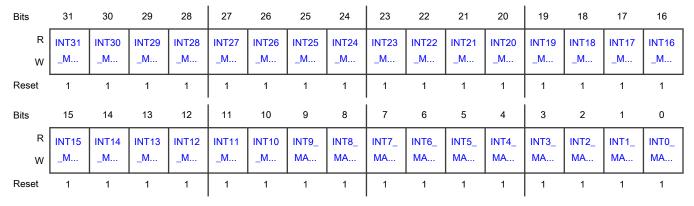

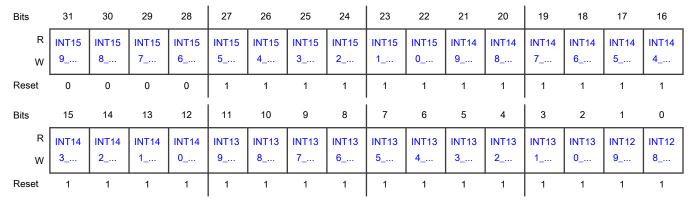

This device supports 8 priority levels for interrupts. Therefore, in the NVIC each source in the IPR registers contains 3 bits. For example, IPR0 is shown below:

## 4.3.2 Non-Maskable Interrupt (NMI) configuration

The Non-Maskable Interrupt (NMI) enable bit and source selection bits are implemented for each core in SYSCON NMI Source Select register.

### 4.3.3 Interrupt channel assignments

The interrupt source assignments are defined in the following table.

- Vector number the value stored on the stack when an interrupt is serviced.

- IRQ number non-core interrupt source count, which is the vector number minus 16.

The IRQ number is used within Arm's NVIC documentation.

Table 4. Interrupt Vector Assignments

| Address   | Vector | IRQ | NVIC<br>non-IPR<br>register<br>number | NVIC IPR<br>register<br>number | Alias      | Source Description           |

|-----------|--------|-----|---------------------------------------|--------------------------------|------------|------------------------------|

| 0000_0000 | 0      | -   | -                                     | -                              | Cortex-M33 | Initial Stack Pointer        |

| 0000_0004 | 1      | -   | -                                     | -                              | Cortex-M33 | Initial Program Counter      |

| 0000_0008 | 2      | -   | -                                     | -                              | Cortex-M33 | Non-Maskable Interrupt (NMI) |

| 0000_000C | 3      | -   | -                                     | -                              | Cortex-M33 | Hard Fault                   |

| 0000_0010 | 4      | -   | -                                     | -                              | Cortex-M33 | MemManage Fault              |

| 0000_0014 | 5      | -   | -                                     | -                              | Cortex-M33 | Bus Fault                    |

| 0000_0018 | 6      | -   | -                                     | -                              | Cortex-M33 | Usage Fault                  |

| 0000_001C | 7      | -   | -                                     | -                              | Cortex-M33 | Secure fault                 |

Table continues on the next page...

Reference Manual 20 / 1409

Table 4. Interrupt Vector Assignments (continued)

| Address   | Vector | IRQ | NVIC<br>non-IPR<br>register<br>number | NVIC IPR<br>register<br>number | Alias      | Source Description                                    |

|-----------|--------|-----|---------------------------------------|--------------------------------|------------|-------------------------------------------------------|

| 0000_0020 | 8      | -   | -                                     | -                              | Reserved   |                                                       |

| 0000_0024 | 9      | -   | -                                     | -                              | Reserved   |                                                       |

| 0000_0028 | 10     | -   | -                                     | -                              | Reserved   |                                                       |

| 0000_002C | 11     | -   | -                                     | -                              | Cortex-M33 | Supervisor Call (SVCall)                              |

| 0000_0030 | 12     | -   | -                                     | -                              | Cortex-M33 | Debug Monitor                                         |

| 0000_0034 | 13     | -   | -                                     | -                              | Reserved   |                                                       |

| 0000_0038 | 14     | -   | -                                     | -                              | Cortex-M33 | Pendable request for system service (Pendable SrvReq) |

| 0000_003C | 15     | -   | -                                     | -                              | Cortex-M33 | System Tick Timer                                     |

| 0000_0040 | 16     | 0   | 0                                     | 0                              |            | ORs IRQs 1 - 155 (OR IRQ[155:1])                      |

| 0000_0044 | 17     | 1   | 0                                     | 0                              | eDMA_0     | eDMA_0_CH0 error or transfer complete                 |

| 0000_0048 | 18     | 2   | 0                                     | 0                              | eDMA_0     | eDMA_0_CH1 error or transfer complete                 |

| 0000_004C | 19     | 3   | 0                                     | 0                              | eDMA_0     | eDMA_0_CH2 error or transfer complete                 |

| 0000_0050 | 20     | 4   | 0                                     | 1                              | eDMA_0     | eDMA_0_CH3 error or transfer complete                 |

| 0000_0054 | 21     | 5   | 0                                     | 1                              | eDMA_0     | eDMA_0_CH4 error or transfer complete                 |

| 0000_0058 | 22     | 6   | 0                                     | 1                              | eDMA_0     | eDMA_0_CH5 error or transfer complete                 |

| 0000_005C | 23     | 7   | 0                                     | 1                              | eDMA_0     | eDMA_0_CH6 error or transfer complete                 |

| 0000_0060 | 24     | 8   | 0                                     | 2                              | eDMA_0     | eDMA_0_CH7 error or transfer complete                 |

| 0000_0064 | 25     | 9   | 0                                     | 2                              | eDMA_0     | eDMA_0_CH8 error or transfer complete                 |

| 0000_0068 | 26     | 10  | 0                                     | 2                              | eDMA_0     | eDMA_0_CH9 error or transfer complete                 |

| 0000_006C | 27     | 11  | 0                                     | 2                              | eDMA_0     | eDMA_0_CH10 error or transfer complete                |

| 0000_0070 | 28     | 12  | 0                                     | 3                              | eDMA_0     | eDMA_0_CH11 error or transfer complete                |

| 0000_0074 | 29     | 13  | 0                                     | 3                              | eDMA_0     | eDMA_0_CH12 error or transfer complete                |

| 0000_0078 | 30     | 14  | 0                                     | 3                              | eDMA_0     | eDMA_0_CH13 error or transfer complete                |

| 0000_007C | 31     | 15  | 0                                     | 3                              | eDMA_0     | eDMA_0_CH14 error or transfer complete                |

| 0000_0080 | 32     | 16  | 0                                     | 4                              | eDMA_0     | eDMA_0_CH15 error or transfer complete                |

| 0000_0084 | 33     | 17  | 0                                     | 4                              | GPIO0      | GPIO0 interrupt 0                                     |

| 0000_0088 | 34     | 18  | 0                                     | 4                              | GPIO0      | GPIO0 interrupt 1                                     |

| 0000_008C | 35     | 19  | 0                                     | 4                              | GPIO1      | GPIO1 interrupt 0                                     |

| 0000_0090 | 36     | 20  | 0                                     | 5                              | GPIO1      | GPIO1 interrupt 1                                     |

| 0000_0094 | 37     | 21  | 0                                     | 5                              | GPIO2      | GPIO2 interrupt 0                                     |

Table 4. Interrupt Vector Assignments (continued)

| Address   | Vector | IRQ | NVIC<br>non-IPR<br>register<br>number | NVIC IPR<br>register<br>number | Alias            | Source Description                                                                     |

|-----------|--------|-----|---------------------------------------|--------------------------------|------------------|----------------------------------------------------------------------------------------|

| 0000_0098 | 38     | 22  | 0                                     | 5                              | GPIO2            | GPIO2 interrupt 1                                                                      |

| 0000_009C | 39     | 23  | 0                                     | 5                              | GPIO3            | GPIO3 interrupt 0                                                                      |

| 0000_00A0 | 40     | 24  | 0                                     | 6                              | GPIO3            | GPIO3 interrupt 1                                                                      |

| 0000_00A4 | 41     | 25  | 0                                     | 6                              | GPIO4            | GPIO4 interrupt 0                                                                      |

| 8A00_0000 | 42     | 26  | 0                                     | 6                              | GPIO4            | GPIO4 interrupt 1                                                                      |

| 0000_00AC | 43     | 27  | 0                                     | 6                              | GPIO5            | GPIO5 interrupt 0                                                                      |

| 0000_00B0 | 44     | 28  | 0                                     | 7                              | GPIO5            | GPIO5 interrupt 1                                                                      |

| 0000_00B4 | 45     | 29  | 0                                     | 7                              | UTICK0           | Micro-Tick Timer interrupt                                                             |

| 0000_00B8 | 46     | 30  | 0                                     | 7                              | MRT0             | Multi-Rate Timer interrupt                                                             |

| 0000_00BC | 47     | 31  | 0                                     | 7                              | CTIMER0          | Standard counter/timer 0 interrupt                                                     |

| 0000_00C0 | 48     | 32  | 1                                     | 8                              | CTIMER1          | Standard counter/timer 1 interrupt                                                     |

| 0000_00C4 | 49     | 33  | 1                                     | 8                              | SCT0             | SCTIMER/PWM interrupt                                                                  |

| 0000_00C8 | 50     | 34  | 1                                     | 8                              | CTIMER2          | Standard counter/timer 2 interrupt                                                     |

| 0000_00CC | 51     | 35  | 1                                     | 8                              | LP_FLEXCO<br>MM0 | LP_FLEXCOMM0 (LPSPI interrupt or LPI2C interrupt or LPUART Receive/Transmit interrupt) |

| 0000_00D0 | 52     | 36  | 1                                     | 9                              | LP_FLEXCO<br>MM1 | LP_FLEXCOMM1 (LPSPI interrupt or LPI2C interrupt or LPUART Receive/Transmit interrupt) |

| 0000_00D4 | 53     | 37  | 1                                     | 9                              | LP_FLEXCO<br>MM2 | LP_FLEXCOMM2 (LPSPI interrupt or LPI2C interrupt or LPUART Receive/Transmit interrupt) |

| 0000_00D8 | 54     | 38  | 1                                     | 9                              | LP_FLEXCO<br>MM3 | LP_FLEXCOMM3 (LPSPI interrupt or LPI2C interrupt or LPUART Receive/Transmit interrupt) |

| 0000_00DC | 55     | 39  | 1                                     | 9                              | LP_FLEXCO<br>MM4 | LP_FLEXCOMM4 (LPSPI interrupt or LPI2C interrupt or LPUART Receive/Transmit interrupt) |

| 0000_00E0 | 56     | 40  | 1                                     | 10                             | LP_FLEXCO<br>MM5 | LP_FLEXCOMM5 (LPSPI interrupt or LPI2C interrupt or LPUART Receive/Transmit interrupt) |

| 0000_00E4 | 57     | 41  | 1                                     | 10                             | LP_FLEXCO<br>MM6 | LP_FLEXCOMM6 (LPSPI interrupt or LPI2C interrupt or LPUART Receive/Transmit interrupt) |

| 0000_00E8 | 58     | 42  | 1                                     | 10                             | LP_FLEXCO<br>MM7 | LP_FLEXCOMM7 (LPSPI interrupt or LPI2C interrupt or LPUART Receive/Transmit interrupt) |

| 0000_00EC | 59     | 43  | 1                                     | 10                             | LP_FLEXCO<br>MM8 | LP_FLEXCOMM8 (LPSPI interrupt or LPI2C interrupt or LPUART Receive/Transmit interrupt) |

| 0000_00F0 | 60     | 44  | 1                                     | 11                             | LP_FLEXCO<br>MM9 | LP_FLEXCOMM8 (LPSPI interrupt or LPI2C interrupt or LPUART Receive/Transmit interrupt) |

Table 4. Interrupt Vector Assignments (continued)

| Address   | Vector | IRQ | NVIC<br>non-IPR<br>register<br>number | NVIC IPR<br>register<br>number | Alias                   | Source Description                                                          |

|-----------|--------|-----|---------------------------------------|--------------------------------|-------------------------|-----------------------------------------------------------------------------|

| 0000_00F4 | 61     | 45  | 1                                     | 11                             | ADC0                    | Analog-to-Digital Converter 0 - General<br>Purpose interrupt                |

| 0000_00F8 | 62     | 46  | 1                                     | 11                             | ADC1                    | Analog-to-Digital Converter 1 - General<br>Purpose interrupt                |

| 0000_00FC | 63     | 47  | 1                                     | 11                             | PINT0                   | Pin Interrupt Pattern Match Interrupt                                       |

| 0000_0100 | 64     | 48  | 1                                     | 12                             | MICFIL0                 | Microphone Interface interrupt                                              |

| 0000_0104 | 65     | 49  | 1                                     | 12                             | Reserved                | Reserved                                                                    |

| 0000_0108 | 66     | 50  | 1                                     | 12                             | USBFS0                  | Universal Serial Bus - Full Speed interrupt                                 |

| 0000_010C | 67     | 51  | 1                                     | 12                             | USBDCD0                 | Universal Serial Bus - Device Charge<br>Detect interrupt                    |

| 0000_0110 | 68     | 52  | 1                                     | 13                             | RTC0                    | RTC Subsystem interrupt (RTC interrupt or Wake timer interrupt)             |

| 0000_0114 | 69     | 53  | 1                                     | 13                             | SmartDMA                | SmartDMA_IRQ                                                                |

| 0000_0118 | 70     | 54  | 1                                     | 13                             | MAILBOX0                | Inter-CPU Mailbox interrupt0 for CPU0 Inter-CPU Mailbox interrupt1 for CPU1 |

| 0000_011C | 71     | 55  | 1                                     | 13                             | CTIMER3                 | Standard counter/timer 3 interrupt                                          |

| 0000_0120 | 72     | 56  | 1                                     | 14                             | CTIMER4                 | Standard counter/timer 4 interrupt                                          |

| 0000_0124 | 73     | 57  | 1                                     | 14                             | OSTIMER0                | OS event timer interrupt                                                    |

| 0000_0128 | 74     | 58  | 1                                     | 14                             | FlexSPI0                | Flexible Serial Peripheral Interface interrupt                              |

| 0000_012C | 75     | 59  | 1                                     | 14                             | SAI0                    | Serial Audio Interface 0 interrupt                                          |

| 0000_0130 | 76     | 60  | 1                                     | 15                             | SAI1                    | Serial Audio Interface 1 interrupt                                          |

| 0000_0134 | 77     | 61  | 1                                     | 15                             | uSDHC0                  | Ultra Secured Digital Host Controller interrupt                             |

| 0000_0138 | 78     | 62  | 1                                     | 15                             | CAN0                    | Controller Area Network 0 interrupt                                         |

| 0000_013C | 79     | 63  | 1                                     | 15                             | CAN1                    | Controller Area Network 1 interrupt                                         |

| 0000_0140 | 80     | 64  | 2                                     | 16                             | Reserved                | _                                                                           |

| 0000_0144 | 81     | 65  | 2                                     | 16                             | Reserved                | _                                                                           |

| 0000_0148 | 82     | 66  | 2                                     | 16                             | USBHS1_PH<br>Y          | USBHS DCD or USBHS Phy interrupt                                            |

| 0000_014C | 83     | 67  | 2                                     | 16                             | USBHS1                  | USB High Speed OTG Controller interrupt                                     |

| 0000_0150 | 84     | 68  | 2                                     | 17                             | SEC_HYPER<br>VISOR_CALL | AHB Secure Controller hypervisor call interrupt                             |

| 0000_0154 | 85     | 69  | 2                                     | 17                             | Reserved                | _                                                                           |

| 0000_0158 | 86     | 70  | 2                                     | 17                             | PLU0                    | Programmable Logic Unit interrupt                                           |

Table 4. Interrupt Vector Assignments (continued)

| Address   | Vector | IRQ | NVIC<br>non-IPR<br>register<br>number | NVIC IPR register number | Alias             | Source Description                                                                                                                        |

|-----------|--------|-----|---------------------------------------|--------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 0000_015C | 87     | 71  | 2                                     | 17                       | FREQME0           | Frequency Measurement interrupt                                                                                                           |

| 0000_0160 | 88     | 72  | 2                                     | 18                       | SEC_Violatio<br>n | Secure violation interrupt (Memory Block Checker (MBC) interrupt or Secure AHB Bus and AHB Controller (AHBSC) matrix violation interrupt) |

| 0000_0164 | 89     | 73  | 2                                     | 18                       | ELS               | ELS interrupt                                                                                                                             |

| 0000_0168 | 90     | 74  | 2                                     | 18                       | PKC               | PKC interrupt                                                                                                                             |

| 0000_016C | 91     | 75  | 2                                     | 18                       | PUF               | Physical Unclonable Function interrupt                                                                                                    |

| 0000_0170 | 92     | 76  | 2                                     | 19                       | POWERQUA<br>D0    | PowerQuad interrupt                                                                                                                       |

| 0000_0174 | 93     | 77  | 2                                     | 19                       | eDMA_1            | eDMA_1_CH0 error or transfer complete                                                                                                     |

| 0000_0178 | 94     | 78  | 2                                     | 19                       | eDMA_1            | eDMA_1_CH1 error or transfer complete                                                                                                     |

| 0000_017C | 95     | 79  | 2                                     | 19                       | eDMA_1            | eDMA_1_CH2 error or transfer complete                                                                                                     |

| 0000_0180 | 96     | 80  | 2                                     | 20                       | eDMA_1            | eDMA_1_CH3 error or transfer complete                                                                                                     |

| 0000_0184 | 97     | 81  | 2                                     | 20                       | eDMA_1            | eDMA_1_CH4 error or transfer complete                                                                                                     |

| 0000_0188 | 98     | 82  | 2                                     | 20                       | eDMA_1            | eDMA_1_CH5 error or transfer complete                                                                                                     |

| 0000_018C | 99     | 83  | 2                                     | 20                       | eDMA_1            | eDMA_1_CH6 error or transfer complete                                                                                                     |

| 0000_0190 | 100    | 84  | 2                                     | 21                       | eDMA_1            | eDMA_1_CH7 error or transfer complete                                                                                                     |

| 0000_0194 | 101    | 85  | 2                                     | 21                       | eDMA_1            | eDMA_1_CH8 error or transfer complete                                                                                                     |

| 0000_0198 | 102    | 86  | 2                                     | 21                       | eDMA_1            | eDMA_1_CH9 error or transfer complete                                                                                                     |

| 0000_019C | 103    | 87  | 2                                     | 21                       | eDMA_1            | eDMA_1_CH10 error or transfer complete                                                                                                    |

| 0000_01A0 | 104    | 88  | 2                                     | 22                       | eDMA_1            | eDMA_1_CH11 error or transfer complete                                                                                                    |

| 0000_01A4 | 105    | 89  | 2                                     | 22                       | eDMA_1            | eDMA_1_CH12 error or transfer complete                                                                                                    |

| 0000_01A8 | 106    | 90  | 2                                     | 22                       | eDMA_1            | eDMA_1_CH13 error or transfer complete                                                                                                    |

| 0000_01AC | 107    | 91  | 2                                     | 22                       | eDMA_1            | eDMA_1_CH14 error or transfer complete                                                                                                    |

| 0000_01B0 | 108    | 92  | 2                                     | 23                       | eDMA_1            | eDMA_1_CH15 error or transfer complete                                                                                                    |

| 0000_01B4 | 109    | 93  | 2                                     | 23                       | CDOG0             | Code Watchdog Timer 0 interrupt                                                                                                           |

| 0000_01B8 | 110    | 94  | 2                                     | 23                       | CDOG1             | Code Watchdog Timer 1 interrupt                                                                                                           |

| 0000_01BC | 111    | 95  | 2                                     | 23                       | I3C0              | Improved Inter Integrated Circuit interrupt 0                                                                                             |

| 0000_01C0 | 112    | 96  | 3                                     | 24                       | I3C1              | Improved Inter Integrated Circuit interrupt 1                                                                                             |

| 0000_01C4 | 113    | 97  | 3                                     | 24                       | NPU               | NPU interrupt                                                                                                                             |

| 0000_01C8 | 114    | 98  | 3                                     | 24                       | GDET0 &<br>GDET1  | Digital Glitch Detect 0 interrupt or Digital Glitch Detect 1 interrupt                                                                    |

Reference Manual 24 / 1409

Table 4. Interrupt Vector Assignments (continued)

| Address   | Vector | IRQ | NVIC<br>non-IPR<br>register<br>number | NVIC IPR<br>register<br>number | Alias   | Source Description                                                                           |

|-----------|--------|-----|---------------------------------------|--------------------------------|---------|----------------------------------------------------------------------------------------------|

|           |        |     |                                       |                                |         | NOTE The SYSCON module has the fields that are used to enable and clear the GDET interrupts. |

| 0000_01CC | 115    | 99  | 3                                     | 24                             | VBAT0   | VBAT interrupt (VBAT interrupt or digital tamper interrupt)                                  |

| 0000_01D0 | 116    | 100 | 3                                     | 25                             | EWM0    | External Watchdog Monitor interrupt                                                          |

| 0000_01D4 | 117    | 101 | 3                                     | 25                             | TSI0    | TSI End of Scan interrupt                                                                    |

| 0000_01D8 | 118    | 102 | 3                                     | 25                             | TSI0    | TSI End of Scan interrupt                                                                    |

| 0000_01DC | 119    | 103 | 3                                     | 25                             | EMVSIM0 | EMVSIM0 interrupt                                                                            |

| 0000_01E0 | 120    | 104 | 3                                     | 26                             | EMVSIM1 | EMVSIM1 interrupt                                                                            |

| 0000_01E4 | 121    | 105 | 3                                     | 26                             | FlexIO0 | Flexible Input/Output interrupt                                                              |

| 0000_01E8 | 122    | 106 | 3                                     | 26                             | DAC0    | 12-bit Digital-to-Analog Converter 0 - General Purpose interrupt                             |

| 0000_01EC | 123    | 107 | 3                                     | 26                             | DAC1    | 12-bit Digital-to-Analog Converter 1 - General Purpose interrupt                             |

| 0000_01F0 | 124    | 108 | 3                                     | 27                             | DAC2    | 14-bit Digital-to-Analog Converter interrupt                                                 |

| 0000_01F4 | 125    | 109 | 3                                     | 27                             | CMP0    | Comparator0 interrupt                                                                        |

| 0000_01F8 | 126    | 110 | 3                                     | 27                             | CMP1    | Comparator1 interrupt                                                                        |

| 0000_01FC | 127    | 111 | 3                                     | 27                             | CMP2    | Comparator2 interrupt                                                                        |

| 0000_0200 | 128    | 112 | 3                                     | 28                             | PWM0    | FlexPWM0_reload_error interrupt                                                              |

| 0000_0204 | 129    | 113 | 3                                     | 28                             | PWM0    | FlexPWM0_fault interrupt                                                                     |

| 0000_0208 | 130    | 114 | 3                                     | 28                             | PWM0    | FlexPWM0 Submodule 0 capture/compare/ reload interrupt                                       |

| 0000_020C | 131    | 115 | 3                                     | 28                             | PWM0    | FlexPWM0 Submodule 1 capture/compare/ reload interrupt                                       |

| 0000_0210 | 132    | 116 | 3                                     | 29                             | PWM0    | FlexPWM0 Submodule 2 capture/compare/ reload interrupt                                       |

| 0000_0214 | 133    | 117 | 3                                     | 29                             | PWM0    | FlexPWM0 Submodule 3 capture/compare/ reload interrupt                                       |

| 0000_0218 | 134    | 118 | 3                                     | 29                             | PWM1    | FlexPWM1_reload_error interrupt                                                              |

| 0000_021C | 135    | 119 | 3                                     | 29                             | PWM1    | FlexPWM1_fault interrupt                                                                     |

Table 4. Interrupt Vector Assignments (continued)

| Address   | Vector | IRQ | NVIC<br>non-IPR<br>register<br>number | NVIC IPR<br>register<br>number | Alias  | Source Description                                     |

|-----------|--------|-----|---------------------------------------|--------------------------------|--------|--------------------------------------------------------|

| 0000_0220 | 136    | 120 | 3                                     | 30                             | PWM1   | FlexPWM1 Submodule 0 capture/compare/ reload interrupt |

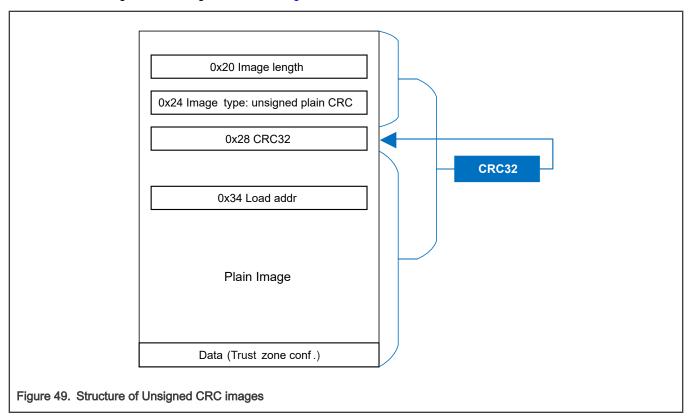

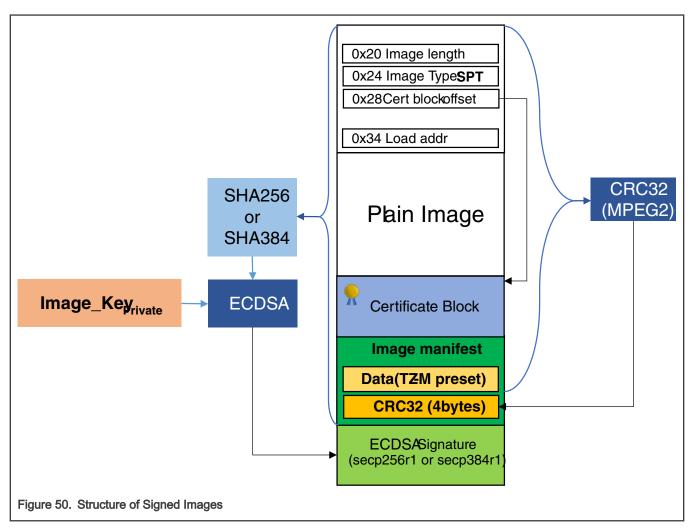

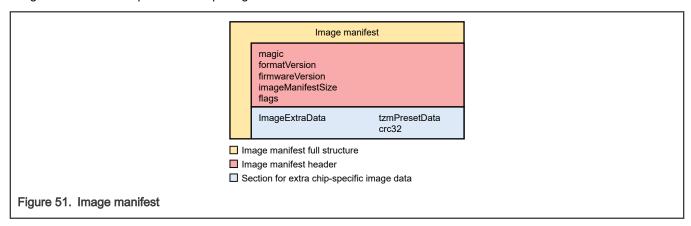

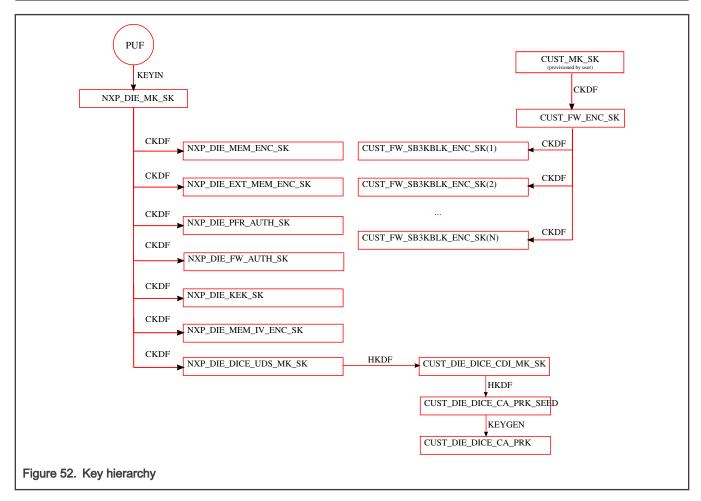

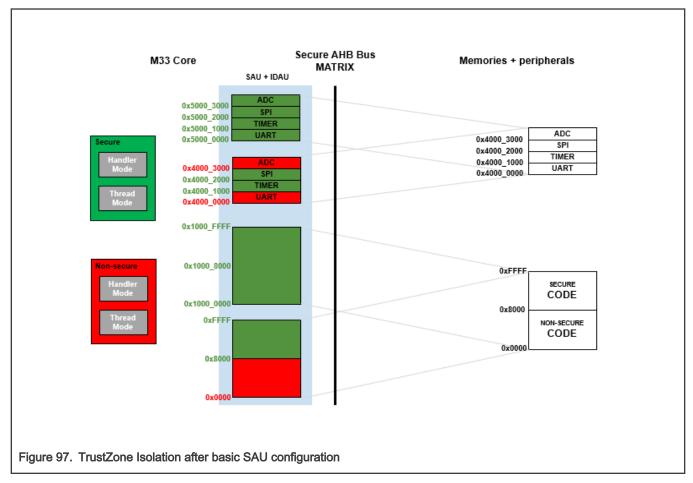

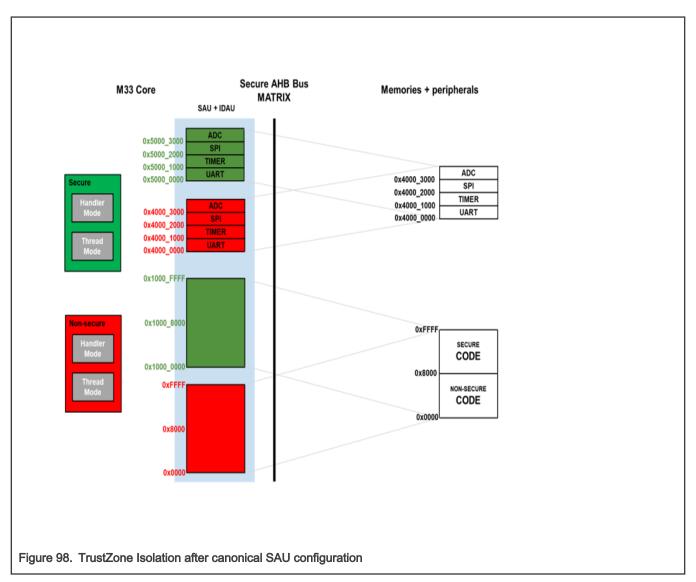

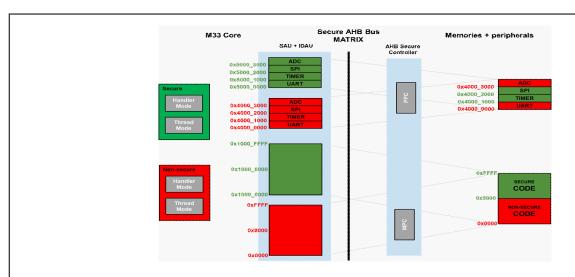

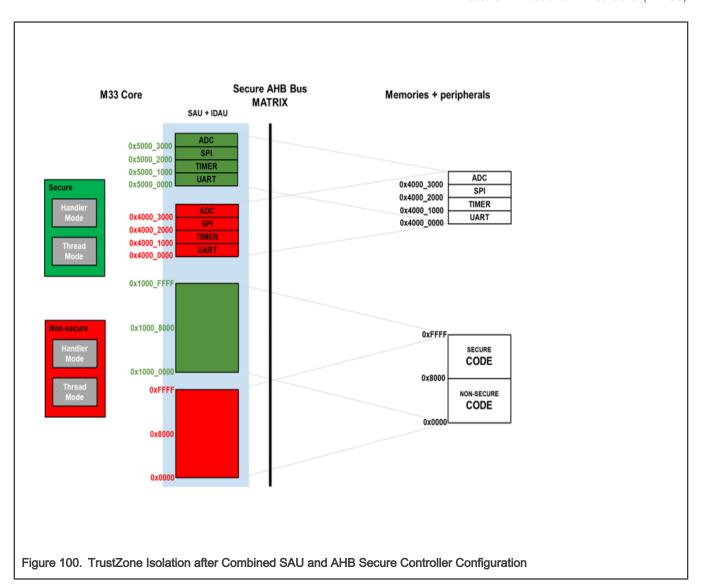

| 0000_0224 | 137    | 121 | 3                                     | 30                             | PWM1   | FlexPWM1 Submodule 1 capture/compare/ reload interrupt |