# 7-Cell to 16-Cell, High-Accuracy Battery Monitor and Protector with Coulomb Counting

## **DESCRIPTION**

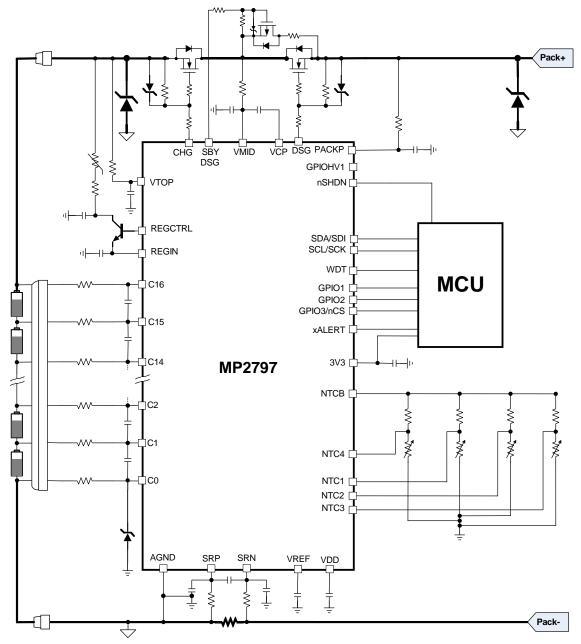

The MP2797 is a robust battery management device, providing a complete analog front-end (AFE) monitoring and protection solution. It is designed for multiple-cell series battery management systems (BMS). The device can support I<sup>2</sup>C or SPI communication. It supports connections for 7-cell to 16-cell series battery packs, with an absolute voltage exceeding 80V on particular pins.

The MP2797 integrates two separate analog-to-digital converters (ADCs). The first ADC measures each channel's differential cell voltages (up to 16 channels), die temperature, and 4-channel temperatures via external NTC thermistors. The second ADC measures the charge/discharge current via an external current-sense resistor. The dual ADC architecture enables synchronous voltage and current measurements for cell and pack impedance monitoring.

When paired with an MPF4279x fuel gauge, the MP2797 can achieve a state-of-charge (SOC) error to within 2%.

The MP2797 includes high-side MOSFET (HSFET) drivers for charge and discharge control. The discharge (DSG) MOSFET driver includes a configurable soft start (SS) that provides a controlled turn-on, eliminating the need for an external pre-charge circuit. The MOSFET drivers also incorporate over-current protection (OCP), short-circuit protection (SCP), battery undervoltage protection (UVP), battery over-voltage protection (OVP), and high-/low-temperature protection. All of these protections have configurable thresholds.

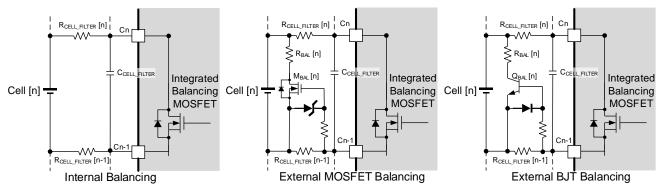

Internal passive balancing MOSFETs can be used to equalize mismatched cells, supporting up to 58mA. There is also the option to drive external balancing transistors (MOSFET or BJT).

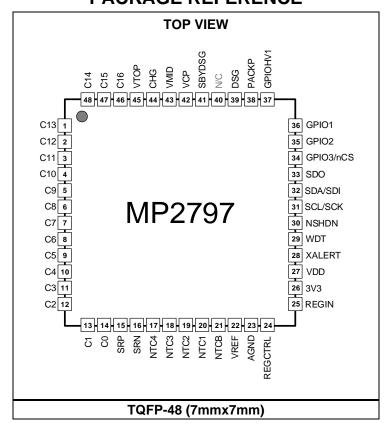

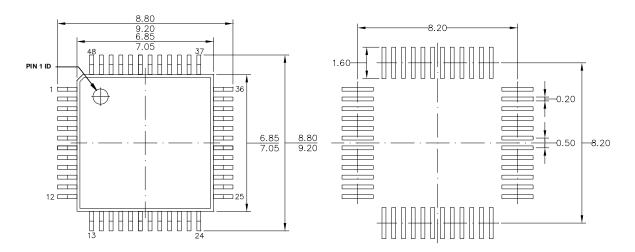

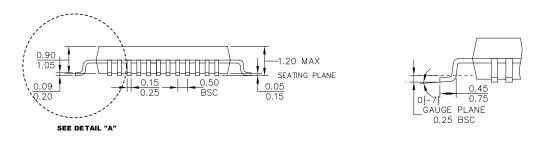

The MP2797 is available in a TQFP-48 (7mmx7mm) package.

#### **FEATURES**

- Incorporates Dual ADC Architecture:

- <±2% State-of-Charge (SOC) Error with MPF4279x Fuel Gauge

- Cell Voltage Measurement Error <5mV</li>

- Current/Coulomb Counter Error <±0.5%

- Strictly Synchronized Current/Voltage Measurement for Impedance Sensing

- Includes High-Side N-Channel MOSFET Drivers for Charge and Discharge Control:

- Supports MOSFET Soft-Start Discharge Control to Eliminate Pre-Charge Circuit

- Drives Up to 100A DC with Parallel N-Channel MOSFETs

- Hardware Configurable Protections:

- Charge/Discharge OCP and SCP

- Cell UVP and OVP

- Pack UVP and OVP

- o Cell Low-/High-Temperature Protection

- Die High-Temperature Protection

- Passive Cell Balancing up to 58mA per Cell:

- Can Drive External Balancing Transistors

- Automatic or Manual Control

- Additional Features:

- o Integrated 3.3V and 5V LDOs

- Reduced Current Standby Mode

- Load and Charger Plug-In Detection

- High-Voltage and Low-Voltage GPIOs

- Dedicated Thermistor Inputs

- Open Wire Detection

- Persistent Dead Battery Flag

- Lockable Multiple-Time Programmable (MTP) Memory for Key Thresholds

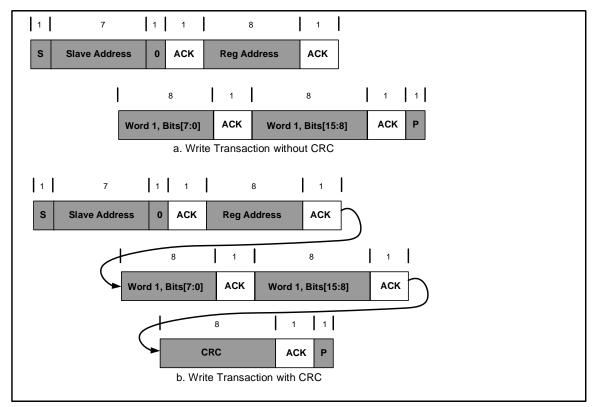

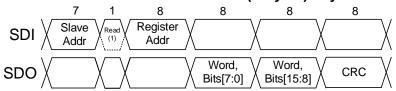

- I2C or SPI Interface with 8-Bit CRC

- Random Cell Connection Tolerant

- Available in a TQFP-48 (7mmx7mm) Package

#### **APPLICATIONS**

- Energy Storage System (ESS)

- E-Bikes, E-Scooters

- Light Electric Vehicles (LEVs)

- Power and Gardening Tools

- Battery Backups and UPS

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

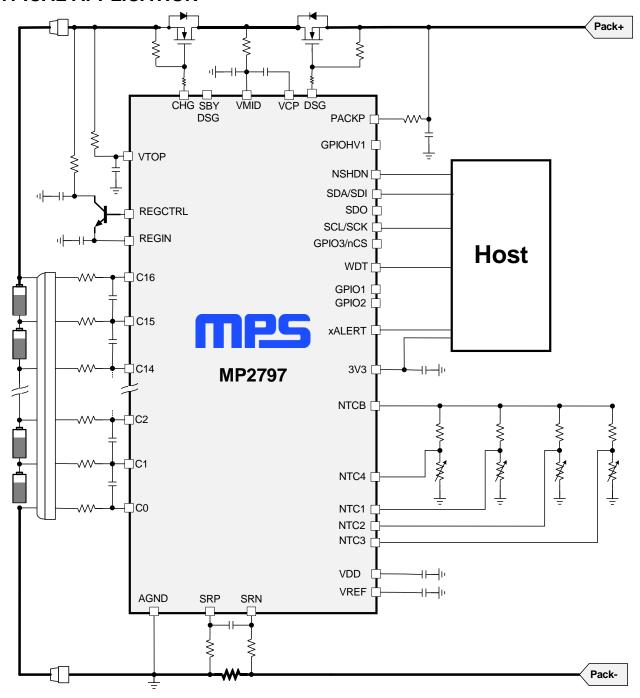

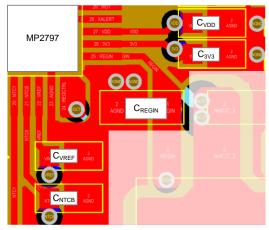

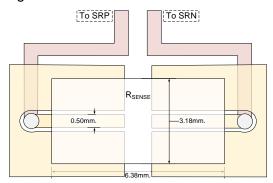

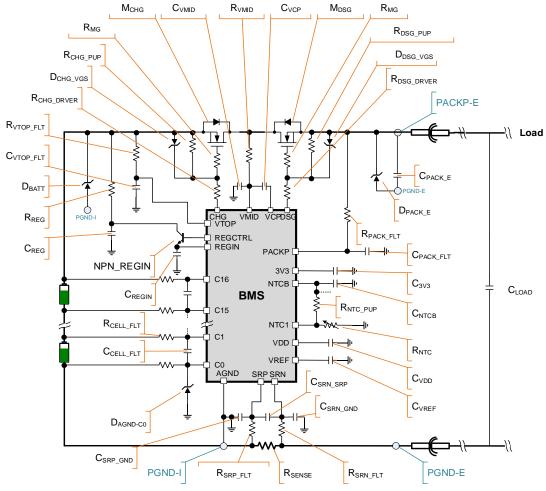

# **TYPICAL APPLICATION**

## ORDERING INFORMATION

| Part Number*     | Package           | Top Marking | MSL Rating | Communication                  |

|------------------|-------------------|-------------|------------|--------------------------------|

| MP2797DFP-xxxx** | TQFP-48 (7mmx7mm) | See Below   | 3          | -                              |

| MP2797DFP-0000   | TQFP-48 (7mmx7mm) | See Below   | 3          | I <sup>2</sup> C, CRC disabled |

| MP2797DFP-0001   | TQFP-48 (7mmx7mm) | See Below   | 3          | I <sup>2</sup> C, CRC enabled  |

| MP2797DFP-0002   | TQFP-48 (7mmx7mm) | See Below   | 3          | SPI, CRC disabled              |

| EVKT-MP2797-0000 | Evaluation kit    | N/A         | N/A        | N/A                            |

| EVKT-MP2797-0002 | Evaluation kit    | N/A         | N/A        | N/A                            |

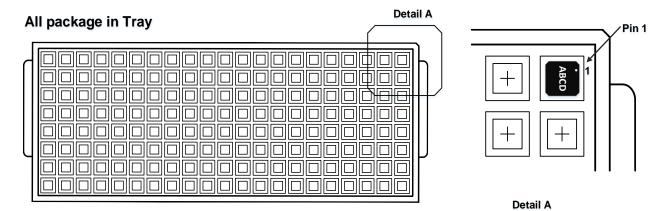

<sup>\*</sup> For Tray, add suffix -T (e.g. MP2797DFP-xxxx-T).

# **TOP MARKING (MP2797)**

# M<u>PSYYWW</u> MP2797 LLLLLLLLL

MPS: MPS prefix YY: Year code WW: Week code MP: MPS prefix 2797: Part number LLLLLLLL: Lot number

<sup>\*\* &</sup>quot;xxxx" is the configuration code identifier for the register settings. Each "x" can be a hexadecimal value between 0 and F. The default codes are "0000", "0001", and "0002". Contact an MPS FAE to create this unique number.

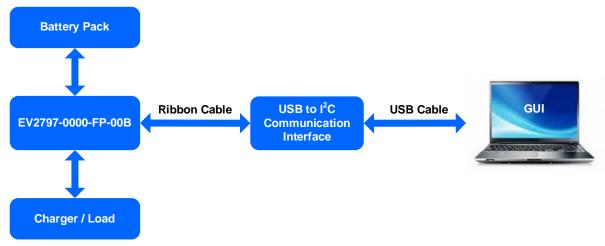

### **EVALUATION KIT EVKT-MP2797-0000**

EVKT-MP2797-0000 kit contents (items below can be ordered separately):

| # | Part Number        | Item                                                                                              | Quantity |

|---|--------------------|---------------------------------------------------------------------------------------------------|----------|

| 1 | EV2797-0000-FP-00B | MP2797DFP-0000 I <sup>2</sup> C evaluation board                                                  | 1        |

| 2 | EVKT-USBI2C-02     | Includes one USB to I <sup>2</sup> C communication interface, one USB cable, and one ribbon cable | 1        |

| 3 | Online resources   | Include datasheet, user guide, product brief, and GUI                                             | 1        |

## Order directly from MonolithicPower.com or our distributors.

Figure 1: EV2797-0000-FP-00B Evaluation Kit Set-Up

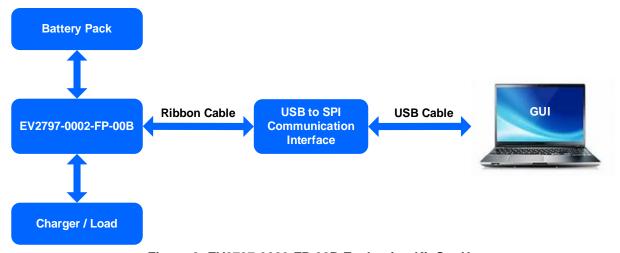

### **EVALUATION KIT EVKT-MP2797-0002**

EVKT-MP2797-0002 kit contents (items below can be ordered separately):

| # | Part Number        | Item                                                                                 | Quantity |

|---|--------------------|--------------------------------------------------------------------------------------|----------|

| 1 | EV2797-0002-FP-00B | MP2797DFP-0002 SPI evaluation board                                                  | 1        |

| 2 | EVKT-USBSPI-00     | Includes one USB to SPI communication interface, one USB cable, and one ribbon cable | 1        |

| 3 | Online resources   | Include datasheet, user guide, product brief, and GUI                                | 1        |

#### Order directly from MonolithicPower.com or our distributors.

Figure 2: EV2797-0002-FP-00B Evaluation Kit Set-Up

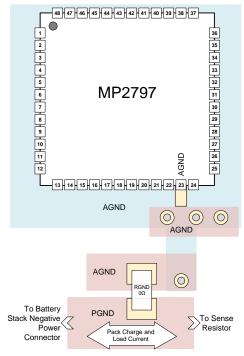

# **PACKAGE REFERENCE**

# **PIN FUNCTIONS**

| Pin# | Name    | Type     | Description                                                                      |

|------|---------|----------|----------------------------------------------------------------------------------|

| 26   | 3V3     | Р        | <b>3.3V voltage output to drive external peripherals.</b> Bypass 3V3 with an     |

| 20   | 373     | Г        | external 1µF capacitor.                                                          |

| 23   | AGND    | Р        | <b>Ground.</b> Connect AGND near the positive connection (SRP) of the low-side   |

| 23   | AGND    | Г        | sense resistor.                                                                  |

|      |         |          | Battery-side pack-sensing voltage and low-current positive supply pin.           |

| 45   | VTOP    | Р        | VTOP must be connected to the top of the battery stack, which is the highest     |

|      |         |          | positive voltage in the battery pack.                                            |

| 46   | C16     | I        | Connect to the positive pin of cell 16.                                          |

| 47   | C15     | I        | Connect to the positive pin of cell 15.                                          |

| 48   | C14     | I        | Connect to the positive pin of cell 14.                                          |

| 1    | C13     | I        | Connect to the positive pin of cell 13.                                          |

| 2    | C12     | ı        | Connect to the positive pin of cell 12.                                          |

| 3    | C11     | ı        | Connect to the positive pin of cell 11.                                          |

| 4    | C10     |          | Connect to the positive pin of cell 10.                                          |

| 5    | C9      |          | Connect to the positive pin of cell 9.                                           |

| 6    | C8      | i        | Connect to the positive pin of cell 8.                                           |

| 7    | C7      | i        | Connect to the positive pin of cell 7.                                           |

| 8    | C6      | i        | Connect to the positive pin of cell 6.                                           |

| 9    | C5      | i        | Connect to the positive pin of cell 5.                                           |

| 10   | C4      | i        | Connect to the positive pin of cell 4.                                           |

| 11   | C3      | i        | Connect to the positive pin of cell 3.                                           |

| 12   | C2      | i        | Connect to the positive pin of cell 2.                                           |

| 13   | C1      | i        | Connect to the positive pin of cell 1.                                           |

| 14   | C0      | i        | Connect to the negative pin of cell 1.                                           |

| 44   | CHG     | 0        | Charge MOSFET driver.                                                            |

| 39   | DSG     | 0        | Discharge MOSFET driver.                                                         |

| 36   | GPIO1   | I/O      | General-purpose pin 1.                                                           |

| 35   | GPIO2   | I/O      | General-purpose pin 2.                                                           |

| 37   | GPIOHV1 | I/O      | General-purpose, high-voltage pin 1.                                             |

| 30   | NSHDN   | 1/0      | Active-low shutdown input signal.                                                |

| 20   | NTC1    | i        | Thermistor 1 terminal.                                                           |

| 19   | NTC2    | i        | Thermistor 2 terminal.                                                           |

| 18   | NTC3    | <u> </u> | Thermistor 3 terminal.                                                           |

| 17   | NTC4    | <u>'</u> | Thermistor 4 terminal.                                                           |

| 21   | NTCB    | 0        | NTC bias.                                                                        |

| 40   | N/C     |          | Not connected.                                                                   |

| 38   | PACKP   | I/O      | Pack sensing voltage (load side).                                                |

| 24   | REGCTRL | P        | Turn-on control for the external BJT low-dropout (LDO) regulator.                |

| 24   | REGUIRE | Г        | Internal regulator input. Connect an external 3.3µF bypass capacitor from        |

| 25   | REGIN   | Р        | REGIN to AGND.                                                                   |

| 41   | SBYDSG  | 0        | Discharge bypass P-channel MOSFET driver.                                        |

| 29   | WDT     | 1/0      | Watchdog timer pin.                                                              |

|      |         |          |                                                                                  |

| 28   | XALERT  | 0        | Interrupt alert output.                                                          |

| 16   | SRN     |          | Negative sense pin.                                                              |

| 15   | SRP     |          | Positive sense pin.                                                              |

| 40   | VCD     |          | Charge pump regulated voltage. Connect a 47nF capacitor from VCP to              |

| 42   | VCP     | Р        | VMID, then adjust the value based on the number of parallel DSG and CHG MOSFETs. |

|      |         |          | 1.8V rail for internal use. Connect a 1µF bypass capacitor from VDD to           |

| 27   | VDD     | Р        | AGND.                                                                            |

| 43   | VMID    | Р        | Protection MOSFET middle point.                                                  |

| 40   | VIVIID  |          | Frotection MOSFET illiquie politi.                                               |

# PIN FUNCTIONS (continued)

| Pin # | Name      | Type | Description                                                                                                         |

|-------|-----------|------|---------------------------------------------------------------------------------------------------------------------|

| 22    | VREF      | Р    | ADC reference voltage.                                                                                              |

| 34    | GPIO3/nCS | I/O  | <b>Multi-function pin.</b> This pin can be set as GPIO3, or it can be set for SPI cable selection.                  |

| 31    | SCL/SCK   | I    | <b>Multi-function pin.</b> This pin can be set as the I <sup>2</sup> C interface clock or the SPI interface clock.  |

| 32    | SDA/SDI   | I/O  | <b>Multi-function pin.</b> This pin can be set as the I <sup>2</sup> C interface data or the SPI serial data input. |

| 33    | SDO       | 0    | SPI serial data output.                                                                                             |

## **ABSOLUTE MAXIMUM RATINGS** (1)

| CHG, DSG, VCP to AGND . SBYDSG to AGND GPIOHV1 to AGND GPIOHV1 to VTOP VTOP to AGND PACKP to AGND VMID to AGND Cx - C (x - 1) (x: 1 to 16) C16 to AGND Cx to AGND (x: 1 to 15) | 0.3V to +86V<br>0.3V to +86V<br>0.3V to +86V<br>0.5V to +86V<br>0.3V to +86V<br>0.3V to +10V<br>0.3V to +86V |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| 0.3V to                                                                                                                                                                        |                                                                                                              |

| C0 to AGND                                                                                                                                                                     |                                                                                                              |

| SRP, SRN to AGND                                                                                                                                                               | 0.5V to +6V                                                                                                  |

| VCP to VMID                                                                                                                                                                    |                                                                                                              |

| REGCTRL to AGND                                                                                                                                                                | 0.3V to +15V                                                                                                 |

| NSHDN to AGND                                                                                                                                                                  |                                                                                                              |

| VDD to AGND                                                                                                                                                                    |                                                                                                              |

| All other pins to AGND                                                                                                                                                         |                                                                                                              |

| Junction temperature                                                                                                                                                           | 150°C                                                                                                        |

| Lead temperature                                                                                                                                                               | 260°C                                                                                                        |

| Storage temperature                                                                                                                                                            | CEOC 10 14E00C                                                                                               |

# **ESD Ratings**

| Human body model (HE | 3M) <sup>(2)</sup> | 1.5kV |

|----------------------|--------------------|-------|

| Charged device model | (CDM) (3)          | 500V  |

## Recommended Operating Conditions (4)

| VTOP voltage                            | 18V to 75.2V    |

|-----------------------------------------|-----------------|

| Cx - C (x - 1) (x: 1 to 16) (5)         | 1V to 5V        |

| C0 to AGND                              | 0.25V to +0.3V  |

| REGIN voltage                           | 4.5V to 5.5V    |

| Operating temperature (T <sub>J</sub> ) | 40°C to +85°C   |

| SRP to SRN                              | 100mV to +100mV |

### Thermal Resistance (6)

| Junction-to-ambient (R <sub>0JA</sub> )          | 46.6°C/W |

|--------------------------------------------------|----------|

| Junction-to-case (top) (R <sub>0JC(TOP)</sub> )  | 14.5°C/W |

| Junction-to-board (top) (R <sub>0JB(TOP)</sub> ) | 27.1°C/W |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) Tested per ANSI/ESDA/JEDEC JS-001.

- 3) Tested per ANSI/ESDA/JEDEC JS-002.

- The device is not guaranteed to function outside of its operating conditions.

- 5) The stack voltage should exceed 18V.

- Metrics provided using set-up conditions compliant with EIA/JESD51-2, 7, and 8.

# **ELECTRICAL CHARACTERISTICS**

Connected cells = 16, each cell voltage = 3.75V,  $V_{TOP}$  = 60V,  $T_A$  = 25°C, unless otherwise noted.

| Parameter Name                                                   | Symbol                 | Condition                                                                                                                                                                                      | Min  | Тур  | Max  | Units |  |

|------------------------------------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|--|

| Supply Current and Leakage                                       |                        |                                                                                                                                                                                                |      |      |      |       |  |

|                                                                  |                        | VTOP + REGIN current, NSHDN pin low, 3.3V off, T <sub>A</sub> = 25°C                                                                                                                           |      | 1    |      | μΑ    |  |

| Tatalah dibanasan                                                | I <sub>VTOP_SHDN</sub> | VTOP + REGIN current, NSHDN pin low, 3.3V off, $T_A = -40$ °C to +85°C                                                                                                                         |      |      | 2.5  | μΑ    |  |

| Total shutdown current                                           | TVTOP_SHDN             | VTOP + REGIN current, 3.3V on, NSHDN pin low, $T_A = 25$ °C                                                                                                                                    |      | 13.5 |      | μΑ    |  |

|                                                                  |                        | VTOP + REGIN current, 3.3V on, NSHDN pin low, $T_A = -40^{\circ}$ C to +85°C                                                                                                                   |      |      | 20   | μΑ    |  |

| Total safe state                                                 | Ivtop_safe             | VTOP + REGIN current, communication interface enabled, safe state (all MOSFETs off), hardware monitoring off, plug-in detection disabled, $T_A = 25^{\circ}C$                                  |      | 23   |      | μΑ    |  |

| current                                                          | IVTOP_SAFE             | VTOP + REGIN current, communication interface enabled, safe state (all MOSFETs off), hardware monitoring off, plug-in detection disabled, $T_A = -40^{\circ}\text{C}$ to $+85^{\circ}\text{C}$ |      |      | 30   | μΑ    |  |

| Cell leakage                                                     | la                     | T <sub>A</sub> = 25°C                                                                                                                                                                          | -200 |      | +200 | nA    |  |

| Cell leakage I <sub>Cx_LEAK</sub>                                |                        | $T_A = -40$ °C to +85°C                                                                                                                                                                        | -600 |      | +600 | nA    |  |

| Supported Series Cell                                            | s                      |                                                                                                                                                                                                |      |      |      |       |  |

| Supported cell number (7)                                        | N <sub>CELL</sub>      |                                                                                                                                                                                                | 7    |      | 16   |       |  |

| VTOP supply voltage range                                        | VVTOP_SUPPLY           | $T_A = -40$ °C to +85°C                                                                                                                                                                        | 18   |      | 75.2 | ٧     |  |

| VTOP under-voltage lockout (UVLO) threshold                      | Vvtop_uvlo             | Falling edge, T <sub>A</sub> = -40°C to +85°C                                                                                                                                                  | 14.6 | 15.8 | 17   | V     |  |

| VTOP under-voltage                                               | Vvtop_uvlo_hyst        | T <sub>A</sub> = 25°C                                                                                                                                                                          |      | 1.15 |      | V     |  |

| (UV) hysteresis                                                  | V V TOP_UVLO_HYST      | $T_A = -40$ °C to +85°C                                                                                                                                                                        | 0.78 |      | 1.5  | V     |  |

| Current Sense                                                    |                        | ,                                                                                                                                                                                              |      | T    |      |       |  |

| Current analog-to-<br>digital converter (ADC)<br>conversion time | tiadc                  | 16 bits (15 bits + sign)                                                                                                                                                                       |      | 2    |      | ms    |  |

| Current ADC measurement range                                    | V <sub>SRPN</sub>      | $T_A = -40$ °C to +85°C                                                                                                                                                                        | -100 |      | +100 | mV    |  |

| Current ADC                                                      |                        | 16-bit conversion, FSR = 100mV, SRP-N common mode: +300mV to -125mV from GND, T <sub>A</sub> = 25°C                                                                                            | -0.5 |      | +0.5 | %     |  |

| measurement gain error                                           | Iadc_gain_err          | 16-bit conversion, FSR = 100mV, SRP-N common mode: +300mV to -125mV from GND, T <sub>A</sub> = -40°C to 85°C                                                                                   | -1   |      | +1   | %     |  |

#### Note:

7) Guaranteed by design.

Connected cells = 16, each cell voltage = 3.75V,  $V_{TOP}$  = 60V,  $T_A$  = 25°C, unless otherwise noted.

| Parameter Name                                  | Symbol                 | Condition                                                                                                                          | Min   | Тур | Max   | Units |

|-------------------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|-------|

| Current-sense offset (8)                        | VIADC_ACC_<br>OFFSET   | SRP - SRN = 0V, SRP-N common mode: $+300$ mV to $-125$ mV from GND, $T_A = -40$ °C to $+85$ °C                                     | -12   |     | +12   | μV    |

| SRP and SRN leakage                             | I <sub>SRPN_LEAK</sub> | IADC not running, $T_A = -40$ °C to +85°C                                                                                          | -500  |     | +500  | nA    |

| SRP and SRN<br>differential input               | lannu niss             | IADC running, $ SPR - SRN  = 100$ mV, absolute value, $T_A = -40$ °C to $+85$ °C                                                   |       | 0.5 |       | μΑ    |

| current                                         | ISRPN_DIFF             | IADC running,  SPR - SRN  < 5mV,<br>T <sub>A</sub> = -40°C to +85°C                                                                |       | 50  |       | nA    |

| ADC Sigma Delta Volta                           | age                    |                                                                                                                                    |       |     |       |       |

| Voltage ADC conversion time                     | tvadc                  | 15 bits, T <sub>A</sub> = 25°C                                                                                                     |       | 2   |       | ms    |

| Cell Voltage Measuren                           | nent                   |                                                                                                                                    |       |     |       |       |

| Cell ADC measurement range                      | $V_{CELL}$             | $T_A = -40$ °C to +85°C                                                                                                            | 1     |     | 5     | V     |

|                                                 |                        | V <sub>CELL</sub> = 2V to 4.5V, T <sub>A</sub> = 25°C                                                                              | -5    |     | +5    | mV    |

| Total cell                                      | Vcell_err              | $V_{CELL} = 2V \text{ to } 4.5V,$<br>$T_A = -20^{\circ}\text{C to } +65^{\circ}\text{C}$                                           | -7.5  |     | +7.5  | mV    |

| measurement error (9)                           |                        | $V_{CELL} = 2V \text{ to } 4.5V,$<br>$T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$                                           | -12.5 |     | +12.5 | mV    |

|                                                 |                        | V <sub>CELL</sub> = 1V to 5V, T <sub>A</sub> = -40°C to +85°C                                                                      | -15   |     | +15   | mV    |

| C0 to AGND voltage                              | Vc0_to_agnd            | C0 to AGND voltage drop resulting in less than 15mV error on cell 1, T <sub>A</sub> = -40°C to +85°C                               | -0.25 |     |       | V     |

| Cell ADC input current                          | In_cell_conv           | Input current during ADC conversion when V <sub>CELL</sub> = 5V, T <sub>A</sub> = 25°C, cell 1 is measured by the C1 to C0 voltage |       | 1.2 |       | μΑ    |

| Die Temperature                                 |                        |                                                                                                                                    |       |     |       |       |

| Die temperature operating range                 | T <sub>DIE</sub>       |                                                                                                                                    | -40   |     | +85   | °C    |

| Over-temperature (OT) analog shutdown threshold | $T_{DIE\_OTSD}$        |                                                                                                                                    |       | 140 | 155   | °C    |

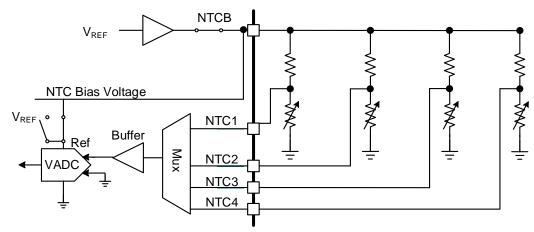

| Negative Temperature                            | Coefficient (          | NTC) Temperature Measurement                                                                                                       |       |     |       |       |

| NTC voltage measurement range                   | V <sub>NTC</sub>       | Nominal NTC range within a percentage of NTCB, $T_A = 25$ °C                                                                       | 0     |     | 100   | %     |

| NTC total measurement error                     | V <sub>NTC_ERR</sub>   | 15-bit conversion, NTCB = $3.3V$ , T <sub>A</sub> = $-40$ °C to $85$ °C                                                            | -55   |     | +55   | LSB   |

#### Notes:

<sup>8)</sup> The current measurement offset error is specified after completion of post-PCB assembly calibration. Contact an MPS FAE for the related application note.

<sup>9)</sup> No calibration required. The error can be further reduced by post-PCB assembly calibration. Contact an MPS FAE for the related application note.

| Parameter Name                        | Symbol                    | Condition                                                                              | Min   | Тур  | Max   | Units |

|---------------------------------------|---------------------------|----------------------------------------------------------------------------------------|-------|------|-------|-------|

| NTCx input leakage                    | Intc_in_leak              | ADC off, on each NTC pin,<br>T <sub>A</sub> = -40°C to +85°C                           |       |      | 250   | nA    |

| NTCx input leakage<br>ADC on          | INTC_LEAK_CONV            | ADC converting NTCx, on each NTC pin, $T_A = 25^{\circ}C$                              |       |      | 250   | nA    |

| VTOP Measurement                      |                           |                                                                                        |       |      |       |       |

| VTOP measurement range                | $V_{VTOP}$                | $T_A = -40$ °C to +85°C                                                                | 18    |      | 75.2  | V     |

| VTOP total measurement error          | V <sub>VTOP_ERR</sub>     | 15-bit conversion (positive range),<br>T <sub>A</sub> = -40°C to +85°C                 | -250  |      | +250  | mV    |

| PACKP Measurement                     |                           |                                                                                        |       |      |       |       |

| Pack measurement range                | VPACKP                    | $T_A = -40$ °C to $+85$ °C                                                             | 2.5   |      | 75.2  | ٧     |

| Pack total measurement error          | V <sub>PACKP_ERR</sub>    | 15-bit conversion (positive range),<br>T <sub>A</sub> = -40°C to +85°C                 | -250  |      | +250  | mV    |

| <b>GPIO Measurement</b>               |                           |                                                                                        |       |      |       |       |

| GPIO measurement range                | V <sub>GPIO</sub>         | T <sub>A</sub> = 25°C                                                                  | 0     |      | 3.3   | V     |

| CDIO total                            |                           | 15-bit ADC reading, T <sub>A</sub> = 25°C                                              | -15   |      | +15   | mV    |

| GPIO total measurement error          | Vgpio_err                 | 15-bit ADC reading,<br>T <sub>A</sub> = -40°C to +85°C                                 | -25   |      | +25   | mV    |

| GPIO input current during ADC reading | IGPIO_CONV_IN             | GPIO pins input current during ADC conversion, T <sub>A</sub> = -40°C to 85°C          |       | 1    |       | μA    |

| Regulators Measureme                  | ents                      |                                                                                        |       |      |       |       |

| REGIN measurement                     |                           | 15-bit ADC reading, T <sub>A</sub> = 25°C                                              | -15   |      | +15   | mV    |

| error                                 | V <sub>REGIN_ERR</sub>    | 15-bit ADC reading, T <sub>A</sub> = -40°C to +85°C                                    | -25   |      | +25   | mV    |

| 2\/2 total magazirament               |                           | 15-bit ADC reading, T <sub>A</sub> = 25°C                                              | -15   |      | +15   | mV    |

| 3V3 total measurement error           | $V_{3V3\_ERR}$            | 15-bit ADC reading,<br>T <sub>A</sub> = -40°C to +85°C                                 | -25   |      | +25   | mV    |

| VDD total                             |                           | 15-bit ADC reading, T <sub>A</sub> = 25°C                                              | -15   |      | +15   | mV    |

| VDD total measurement error           | V <sub>VDD_ERR</sub>      | 15-bit ADC reading,<br>T <sub>A</sub> = -40°C to +85°C                                 | -25   |      | +25   | mV    |

| Hardware Protection                   |                           |                                                                                        |       |      |       |       |

| Cell over-voltage (OV) and UV steps   | V <sub>CELL_TH_STEP</sub> |                                                                                        |       | 19.5 |       | mV    |

| Cell OV/UV step                       |                           | V <sub>CELL</sub> = 2V to 4.5V, T <sub>A</sub> = 0°C to 60°C                           | -19.5 |      | +19.5 | mV    |

| accuracy                              | Vcell_th_acc              | $V_{CELL} = 1V \text{ to } 5V,$<br>$T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$ | -40   |      | +40   | mV    |

| Parameter Name                    | Symbol                      | Condition                                                                                    | Min   | Тур  | Max   | Units |

|-----------------------------------|-----------------------------|----------------------------------------------------------------------------------------------|-------|------|-------|-------|

| Pack OV/UV steps                  | VPACK_TH_STEP               |                                                                                              |       | 19.5 |       | mV    |

| Deep discharge steps              | V <sub>DEEPTH_STEP</sub>    |                                                                                              |       | 19.5 |       | mV    |

| Deep discharge step               | Vdeepth_step_acc            | $V_{CELL} = 2V \text{ to } 4.5V,$<br>$T_A = 0^{\circ}\text{C to } 60^{\circ}\text{C}$        | -19.5 |      | +19.5 | mV    |

| accuracy                          | V DEEPTH_STEP_ACC           | $V_{CELL} = 1V \text{ to } 5V,$<br>$T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$       | -40   |      | +40   | mV    |

| SC fastest detection time         | t <sub>SC_DGL_MIN</sub>     | Fastest deglitch setting and latency, T <sub>A</sub> = -40°C to +85°C                        |       |      | 120   | μs    |

| OC1 discharge FSR value           | Voc1_dsg_fsr_1x             | Range and LSB selector = 0 (1x), FSR (max setting), T <sub>A</sub> = 25°C                    |       | 80   |       | mV    |

| OC1 discharge full scale accuracy | Voc1_dsg_fsr_1x_acc         | Range and LSB selector = 0 (1x),<br>FSR (max setting),<br>$T_A = -40$ °C to +85°C            | -15   |      | +15   | %     |

| OC1 discharge offset              | Voc1_dsg_fsr_1x_off         | Range and LSB selector = 0 (1x), offset on LSB, $T_A = -40$ °C to +85°C                      | -1.5  |      | +1.5  | mV    |

| OC1 discharge FSR value           | V <sub>OC1_DSG_FSR_3X</sub> | Range and LSB selector = 1 (3x), FSR (max setting), T <sub>A</sub> = 25°C                    |       | 240  |       | mV    |

| OC1 discharge full scale accuracy | Voc1_dsg_fsr_3x_acc         | Range and LSB selector = 1 (3x),<br>FSR (max setting),<br>T <sub>A</sub> = -40°C to +85°C    | -15   |      | +15   | %     |

| OC1 discharge offset              | Voc1_dsg_fsr_3x_off         | Range and LSB selector = 1 (3x), offset on smallest setting, T <sub>A</sub> = -40°C to +85°C | -1.5  |      | +1.5  | mV    |

| OC2 discharge FSR value           | Voc2_dsg_fsr_1x             | Range and LSB selector = 0 (1x),<br>FSR (max setting), $T_A = 25$ °C                         |       | 80   |       | mV    |

| OC2 discharge full scale accuracy | Voc2_dsg_fsr_1x_acc         | Range and LSB selector = 0 (1x),<br>FSR (max setting),<br>$T_A = -40$ °C to +85°C            | -15   |      | +15   | %     |

| OC2 discharge offset              | Voc2_dsg_fsr_1x_off         | Range and LSB selector = 0 (1x), offset on smallest setting, T <sub>A</sub> = -40°C to 85°C  | -1.5  |      | +1.5  | mV    |

| OC2 discharge FSR value           | Voc2_dsg_fsr_3x             | Range and LSB selector = 1 (3x), FSR (max setting), T <sub>A</sub> = 25°C                    |       | 240  |       | mV    |

| OC2 discharge full scale accuracy | Voc2_dsg_fsr_3x_acc         | Range and LSB selector = 1 (3x),<br>FSR (max setting),<br>T <sub>A</sub> = -40°C to 85°C     | -15   |      | +15   | %     |

| OC2 discharge offset              | Voc2_dsg_fsr_3x_off         | Range and LSB selector = 1 (3x), offset on smallest setting, $T_A = -40$ °C to +85°C         | -1.5  |      | +1.5  | mV    |

| OC charge FSR value               | Voc_chg_fsr_1x              | Range and LSB selector = 0 (1x), FSR (max setting), T <sub>A</sub> = 25°C                    |       | 51.2 |       | mV    |

| Parameter Name                   | Symbol             | Condition                                                                                    | Min  | Тур | Max  | Units |

|----------------------------------|--------------------|----------------------------------------------------------------------------------------------|------|-----|------|-------|

| OC charge full scale accuracy    | Voc_chg_fsr_1x_acc | Range and LSB selector = 0 (1x),<br>FSR (max setting),<br>T <sub>A</sub> = -40°C to +85°C    | -15  |     | +15  | %     |

| OC charge offset                 | Voc_chg_fsr_1x_off | Range and LSB selector = 0 (1x), offset on smallest setting, $T_A = -40$ °C to +85°C         | -1.5 |     | +1.5 | mV    |

| OC charge FSR<br>value           | Voc_chg_fsr_3x     | Range and LSB selector = 1 (3x),<br>FSR (max setting),<br>T <sub>A</sub> = 25°C              |      | 153 |      | mV    |

| OC charge full scale accuracy    | Voc_chg_fsr_3x_acc | Range and LSB selector = 1 (3x),<br>FSR (max setting),<br>T <sub>A</sub> = -40°C to +85°C    | -15  |     | +15  | %     |

| OC charge offset                 | Voc_chg_fsr_3x_off | Range and LSB selector = 1 (3x), offset on smallest setting, $T_A = -40$ °C to +85°C         | -1.5 |     | +1.5 | mV    |

| SC discharge FSR value           | Vsc_dsg_fsr_1x     | Range and LSB selector = 0 (1x),<br>FSR (max setting),<br>T <sub>A</sub> = 25°C              |      | 176 |      | mV    |

| SC discharge full scale accuracy | Vsc_dsg_fsr_1x_acc | Range and LSB selector = 0 (1x),<br>FSR (max setting),<br>T <sub>A</sub> = -40°C to +85°C    | -15  |     | +15  | %     |

| SC discharge offset              | Vsc_dsg_fsr_1x_off | Range and LSB selector = 0 (1x), offset on smallest setting, $T_A = -40$ °C to +85°C         | -1.5 |     | +1.5 | mV    |

| SC discharge FSR<br>value        | Vsc_dsg_fsr_3x     | Range and LSB selector = 1 (3x),<br>FSR (max setting),<br>T <sub>A</sub> = 25°C              |      | 528 |      | mV    |

| SC discharge full scale accuracy | Vsc_dsg_fsr_3x_acc | Range and LSB selector = 1 (3x),<br>FSR (max setting),<br>T <sub>A</sub> = -40°C to +85°C    | -15  |     | +15  | %     |

| SC discharge offset              | Vsc_dsg_fsr_3x_off | Range and LSB selector = 1 (3x), offset on smallest setting, $T_A = -40$ °C to +85°C         | -2   |     | +2   | mV    |

| SC charge FSR<br>value           | Vsc_chg_fsr_1x     | Range and LSB selector = 0 (1x),<br>FSR (max setting),<br>T <sub>A</sub> = 25°C              |      | 80  |      | mV    |

| SC charge full scale accuracy    | Vsc_chg_fsr_1x_acc | Range and LSB selector = 0 (1x),<br>FSR (max setting),<br>T <sub>A</sub> = -40°C to +85°C    | -15  |     | +15  | %     |

| SC charge offset                 | Vsc_chg_fsr_1x_off | Range and LSB selector = 0 (1x), offset on smallest setting, T <sub>A</sub> = -40°C to +85°C | -1.5 |     | +1.5 | mV    |

| SC charge FSR value              | Vsc_chg_fsr_3x     | Range and LSB selector = 1 (3x),<br>FSR (max setting),<br>T <sub>A</sub> = 25°C              |      | 240 |      | mV    |

| SC charge full scale accuracy    | Vsc_chg_fsr_3x_acc | Range and LSB selector = 1 (3x),<br>FSR (max setting),<br>T <sub>A</sub> = -40°C to +85°C    | -15  |     | +15  | %     |

Connected cells = 16, each cell voltage = 3.75V,  $V_{TOP}$  = 60V,  $T_A$  = 25°C, unless otherwise noted.

| Parameter Name                                          | Symbol                             | Condition                                                                                                                                 | Min                     | Тур  | Max                     | Units |

|---------------------------------------------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------|-------------------------|-------|

| SC charge offset                                        | Vsc_chg_fsr_3x_off                 | Range and LSB selector = 1 (3x), offset on smallest setting, T <sub>A</sub> = -40°C to +85°C                                              | -1.5                    | 7.5  | +1.5                    | mV    |

| Cell-Balancing                                          | <b>,</b>                           |                                                                                                                                           |                         |      |                         |       |

| On- resistance (R <sub>DS(ON)</sub> ) for the balancing | R <sub>DS(ON)_BAL_FET</sub>        | T <sub>A</sub> = 25°C                                                                                                                     |                         | 28   |                         | Ω     |

| MOSFET                                                  | 1 100(ON)_DAL_1 E1                 | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                                                                                             | 15                      |      | 50                      | Ω     |

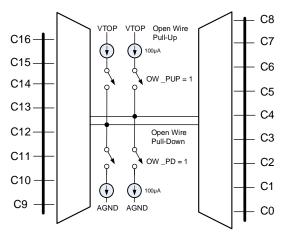

| Open Wire                                               | 1                                  |                                                                                                                                           |                         | 1    |                         | ı     |

| Open-wire pull-up current                               | low_pup                            | $T_A = 25$ °C                                                                                                                             |                         | 100  |                         | μA    |

| Open-wire pull-down current                             | low_pd                             | T <sub>A</sub> = 25°C                                                                                                                     |                         | 100  |                         | μA    |

| Low-Dropout Regulator                                   | (LDO) Supply and                   | References                                                                                                                                |                         |      |                         |       |

| REGCTRL output voltage                                  | Vregetrl                           | $V_{TOP} = 18V$ to $75.2V$ , with REGCTRL load current = 0mA and 1mA, $T_A = -40^{\circ}C$ to $+85^{\circ}C$                              | 5.45                    | 5.6  | 5.75                    | V     |

| REGIN voltage (10)                                      | Vregin                             | With external REGIN BJT $\_FZT853TA$ , $V_{TOP} = 18V$ to 75.2V, with load current = 1mA and 50mA, $T_A = -40^{\circ}C$ to $+85^{\circ}C$ | 4.65                    | 5.1  | 5.4                     | V     |

| REGIN analog UV                                         | Vregin_uv                          | External power to REGIN, falling edge, $V_{TOP} = 18V$ to $75.2V$ , $T_A = -40$ °C to $+85$ °C                                            | 4.16                    | 4.3  | 4.44                    | V     |

| 3V3 nominal voltage                                     | $V_{3V3}$                          | T <sub>A</sub> = 25°C                                                                                                                     |                         | 3.3  |                         | V     |

| 3V3 output accuracy                                     | V <sub>3</sub> V <sub>3</sub> _ACC | $T_A = -40$ °C to +85°C                                                                                                                   | -5                      |      | +5                      | %     |

| 3V3 short-circuit current                               | I <sub>3V3_EFET</sub>              | External power to REGIN,<br>T <sub>A</sub> = -40°C to +85°C                                                                               | 55                      | 68   | 80                      | mA    |

| VDD output voltage                                      | $V_{DD}$                           | T <sub>A</sub> = 25°C                                                                                                                     |                         | 1.8  |                         | V     |

| Reference voltage                                       | $V_{REF}$                          | T <sub>A</sub> = 25°C                                                                                                                     |                         | 3.3  |                         | V     |

| NTCB pull-up voltage                                    | V <sub>NTCB</sub>                  | NTCB enabled, no load,<br>T <sub>A</sub> = 25°C                                                                                           |                         | 3.3  |                         | V     |

| NTOR                                                    |                                    | NTCB enabled, max load,<br>T <sub>A</sub> = 25°C                                                                                          |                         | 4    |                         | mA    |

| NTCB load                                               | INTCB_MAXLOAD                      | NTCB enabled, max load,<br>T <sub>A</sub> = -40°C to +85°C                                                                                | 3.2                     |      | 4.8                     | mA    |

| 3V3 analog UV                                           | V <sub>3</sub> V <sub>3</sub> _UV  | Falling edge                                                                                                                              |                         | 2.85 |                         | V     |

| GPIO                                                    |                                    |                                                                                                                                           |                         |      |                         | -     |

| GPIO input voltage (high)                               | VIH_GPIO                           | Voltage high ( $V_H$ ) = 3.3V or 5V,<br>$T_A$ = -40°C to +85°C                                                                            | 0.8 x<br>V <sub>H</sub> |      | Vн                      | V     |

| GPIO input voltage (low)                                | VIL_GPIO                           | V <sub>H</sub> = 3.3V or 5V,<br>T <sub>A</sub> = -40°C to +85°C                                                                           | 0                       |      | 0.2 x<br>V <sub>H</sub> | V     |

| GPIO output voltage (high)                              | V <sub>OH_GPIO</sub>               | V <sub>H</sub> = 3.3V or 5V,<br>I <sub>SOURCE</sub> = 1.5mA,<br>T <sub>A</sub> = -40°C to +85°C                                           | V <sub>H</sub> - 0.5    |      | V <sub>H</sub>          | V     |

#### Note:

10) Guaranteed by design. The REGIN voltage is limited by the V<sub>REGCTRL</sub> and is equal to V<sub>REGCTRL</sub> - V<sub>BE\_ON</sub>.

| Parameter Name                    | Symbol                  | Condition                                                                                                                                                                                                              | Min | Тур  | Max  | Units |

|-----------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|-------|

| GPIO output voltage (low)         | Vol_gpio                | V <sub>H</sub> = 3.3V or 5V, I <sub>SINK</sub> = 1.5mA,<br>T <sub>A</sub> = -40°C to +85°C                                                                                                                             | 0   |      | 0.4  | V     |

| GPIO push-pull resistor (up)      | R <sub>GPIO_PUP</sub>   | GPIO high voltage = 3.3V, external power to REGIN                                                                                                                                                                      |     | 430  |      | Ω     |

| GPIO push-pull resistor (down)    | R <sub>GPIO_PDOWN</sub> | GPIO low voltage = 0V                                                                                                                                                                                                  |     | 110  | 200  | Ω     |

| GPIO pull-up mode                 | RGPIO_WEAK_PUP          |                                                                                                                                                                                                                        |     | 17   |      | kΩ    |

| GPIO HV                           |                         |                                                                                                                                                                                                                        |     |      |      |       |

| GPIO HV input voltage high level  | V <sub>IH_GPIOHV</sub>  | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$                                                                                                                                                                    | 2.4 |      |      | V     |

| GPIO HV input voltage low level   | VIL_GPIOHV              | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$                                                                                                                                                                    |     |      | 0.7  | ٧     |

| GPIOHV max pull-up current        | IGPIOHV_PUP             |                                                                                                                                                                                                                        |     | 11   |      | mA    |

| GPIOHV max pull-down current      | Igpiohv_pdown           |                                                                                                                                                                                                                        |     | 8    |      | mA    |

| NSHDN Pin                         |                         |                                                                                                                                                                                                                        |     |      |      |       |

| NSHDN internal pull down          | R <sub>SHDN_PD</sub>    | NSHDN 0V to 5V                                                                                                                                                                                                         |     | 5    |      | МΩ    |

| NSHDN configuring voltage         | Vnshdn_prog             |                                                                                                                                                                                                                        | 7.5 | 7.6  | 7.7  | V     |

| NSHDN deglitch to enter shutdown  | tnshdn_dgl_enter        | T <sub>A</sub> = 25°C, IC stays in safe mode for longer than thishiddle.                                                                                                                                               |     | 8    |      | ms    |

| NSHDN deglitch active time        | tnshdn_dgl_active       | T <sub>A</sub> = 25°C                                                                                                                                                                                                  |     | 4    |      | ms    |

| NSHDN falling threshold           | V <sub>NSHDN_FALL</sub> |                                                                                                                                                                                                                        |     | 1    |      | V     |

|                                   |                         | 3V3 enabled at shutdown mode                                                                                                                                                                                           |     | 2.65 |      | V     |

| NSHDN rising threshold            | Vnshdn_rise             | 3V3 disabled at shutdown mode                                                                                                                                                                                          |     | 2    |      | V     |

| WDT Pin                           |                         |                                                                                                                                                                                                                        |     |      |      |       |

| Reset pulse length                | twdt_rstpulse_len       |                                                                                                                                                                                                                        |     | 10   |      | ms    |

| High-Side MOSFET (HS-             | FET) Drive              |                                                                                                                                                                                                                        |     | _    |      |       |

| CHG gate drive voltage            | Vснg                    | $C_{LOAD} = 80 nF$ , static value at transition completed, $V_{TOP} = 18 V$ to 75.2V, $V_{GS} = 10 V$ , $T_A = 25 ^{\circ}C$                                                                                           |     | 10   |      | ٧     |

| CHG gate drive voltage accuracy   | Vchg_acc                | $C_{\text{LOAD}} = 80 \text{nF}$ , static value at transition completed, $V_{\text{TOP}} = 18 \text{V}$ to $75.2 \text{V}$ , $10 \text{V}$ selected, $T_{\text{A}} = -40 ^{\circ} \text{C}$ to $+85 ^{\circ} \text{C}$ | 9.3 |      | 10.7 | V     |

| CHG gate drive turn-on resistance | R <sub>CHG_ON</sub>     | MOSFET drive turned on,<br>PACKP = V <sub>TOP</sub> , T <sub>A</sub> = 25°C                                                                                                                                            |     | 2600 |      | Ω     |

| Parameter Name                             | Symbol                   | Condition                                                                                                                                                               | Min  | Тур   | Max  | Units |

|--------------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|-------|

| CHG gate driver turn-off resistance        | Rchg_off                 | MOSFET driver turned off,<br>PACKP = V <sub>TOP</sub> , T <sub>A</sub> = 25°C                                                                                           |      | 840   |      | Ω     |

| DSG gate drive voltage                     | Vdsg                     | $C_{LOAD} = 80$ nF, static value at transition completed, $V_{TOP} = 18$ V to 75.2V, $V_{GS} = 10$ V, $T_{A} = 25$ °C                                                   |      | 10    |      | V     |

| DSG gate driver voltage accuracy           | Vdsg_acc                 | $C_{LOAD}$ = 80nF, static value at completed transition, $V_{TOP}$ = 18V to 75.2V, 10V selected, $T_A$ = -40°C to +85°C                                                 | 9.3  |       | 10.7 | ٧     |

| DSG gate driver turn-on resistance         | R <sub>DSG_ON</sub>      | MOSFET driver turned on, PACKP = V <sub>TOP</sub> , T <sub>A</sub> = 25°C                                                                                               |      | 2600  |      | Ω     |

| DSG gate driver turn-off resistance        | Rdsg_off                 | MOSFET driver turned off,<br>PACKP = $V_{TOP}$ ,<br>DSG = PACKP + 5V, $T_A$ = 25°C                                                                                      |      | 600   |      | Ω     |

| SBYDSG gate driver voltage                 | Vsbydsg                  | $C_{LOAD}$ = 10nF, static value at transition completed, $V_{TOP}$ = 18V to 75.2V, $V_{GS}$ = -10V, $T_A$ = -40°C to +85°C                                              | -12  | -10   | -9   | ٧     |

| SBYDSG gate driver on resistance           | R <sub>SBYDSG_ON</sub>   | MOSFET driver turned on,<br>T <sub>A</sub> = -40°C to +85°C                                                                                                             |      | 14.3  |      | kΩ    |

| SBYDSG gate driver off resistance          | Rsbydsg_off              | MOSFET driver turned off,<br>T <sub>A</sub> = -40°C to +85°C                                                                                                            |      | 2.7   |      | kΩ    |

| Charge Pump                                |                          |                                                                                                                                                                         |      |       |      |       |

| Charge pump output voltage                 | V <sub>CP</sub>          | Gate driver voltage = 10V, regular control mode, T <sub>A</sub> = 25°C                                                                                                  |      | 14.7  |      | V     |

| Charge pump output voltage accuracy        | V <sub>CP_ACC</sub>      | Accuracy of select VCP average value, T <sub>A</sub> = -40°C to +85°C                                                                                                   | -1   |       | +1   | ٧     |

| Charge pump turn-on time                   | t <sub>CP_TON</sub>      | VCP - AGND transition from $V_{TOP}$ to $V_{TOP}$ + VCP, 10nF capacitor on VCP, $V_{TOP}$ = 21V, for both low-power mode and regular control mode, $T_A$ = -40 to +85°C |      |       | 2    | ms    |

| Pull-Up Comparators                        |                          |                                                                                                                                                                         |      |       | •    |       |

| PACKP charge                               | PACKP_PUP                | $V_{TOP} = 18V \text{ to } 75.2V, T_A = 25^{\circ}C$                                                                                                                    |      | 250   |      | μΑ    |

| PACKP discharge                            | I <sub>PACKP_PDOWN</sub> | $V_{TOP} = 18V \text{ to } 75.2V, T_A = 25^{\circ}C$                                                                                                                    |      | 250   |      | μΑ    |

| PACKP exceeds V <sub>TOP</sub>             | VPACKP_HGR_VTOP          | V <sub>TOP</sub> = 18V to 75.2V, T <sub>A</sub> = 25°C                                                                                                                  |      | 280   |      | mV    |

| PACKP is below V <sub>TOP</sub>            | VPACKP_LWR_VTOP          | V <sub>TOP</sub> = 18V to 75.2V, T <sub>A</sub> = 25°C                                                                                                                  |      | -1.77 |      | V     |

| Standby comparator accuracy                | Vsby_comp_accu           | Offset on the smallest setting,<br>$T_A = 25$ °C                                                                                                                        | -125 |       | +125 | μV    |

| PACKP short recovery threshold             | VPACKP_SCOC_REC_TH       | T <sub>A</sub> = 25°C                                                                                                                                                   |      | 110   |      | mV    |

| Short recovery current-<br>source accuracy | I <sub>SCOC_PUP</sub>    | Offset on the smallest setting, $T_A = 25$ °C                                                                                                                           | -50  |       | +50  | μΑ    |

| Parameter Name                      | Symbol                   | Condition                                                           | Min          | Тур          | Max           | Units |

|-------------------------------------|--------------------------|---------------------------------------------------------------------|--------------|--------------|---------------|-------|

| Internal Clock                      |                          |                                                                     |              |              |               |       |

|                                     |                          | $V_{TOP} = 18V \text{ to } 75.2V, T_A = 25^{\circ}C$                |              | 2            |               | MHz   |

| Internal clock frequency            | f <sub>2M_CLOCK</sub>    | V <sub>TOP</sub> = 18V to 75.2V,<br>T <sub>A</sub> = -40°C to +85°C | 1.85         | 2            | 2.15          | MHz   |

| Low fraguency internal              |                          | $V_{TOP} = 18V \text{ to } 75.2V, T_A = 25^{\circ}C$                | 31.2         | 32           | 32.8          | kHz   |

| Low-frequency internal clock        | f <sub>32</sub> k_clock  | V <sub>TOP</sub> = 18V to 75.2V,<br>T <sub>A</sub> = -40°C to +85°C | 30.7         |              | 33.3          | kHz   |

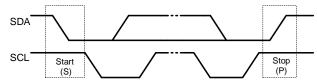

| I <sup>2</sup> C Communication Inte | rface                    |                                                                     |              |              |               |       |

| I <sup>2</sup> C clock frequency    | f <sub>I2C</sub>         | T <sub>A</sub> = 25°C                                               |              |              | 400           | kHz   |

| SCL, SDA low input voltage          | VILOW                    | T <sub>A</sub> = -40°C to +85°C                                     |              |              | 0.25 x<br>3V3 | V     |

| SCL, SDA high input voltage         | Vihigh                   | $T_A = -40$ °C to +85°C                                             | 0.7 x<br>3V3 |              |               | V     |

| SCL, SDA input<br>hysteresis        | VIHYST                   | $T_A = -40$ °C to +85°C                                             |              | 0.2 x<br>3V3 |               | V     |

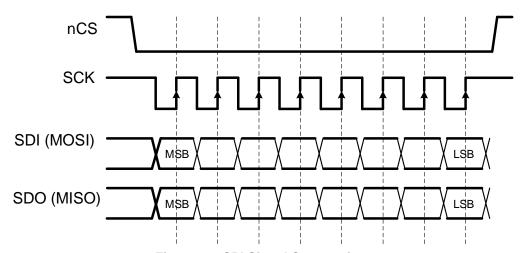

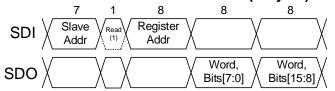

| SPI Communication Inte              | erface                   |                                                                     |              |              |               |       |

| SPI clock frequency                 | f <sub>SPI</sub>         | T <sub>A</sub> = 25°C                                               |              |              | 1.0           | MHz   |

| SPI input low                       | V <sub>SPI_IN_LOW</sub>  | SDI, CLK, T <sub>A</sub> = -40°C to +85°C                           |              |              | 0.25 x<br>3V3 | V     |

| SPI input high                      | V <sub>SPI_IN_HIGH</sub> | SDI, CLK, T <sub>A</sub> = -40°C to +85°C                           | 0.7 x<br>3V3 |              |               | V     |

| SDO high-side (HS) on resistance    | R <sub>SDO_DRV_HI</sub>  | Isource = 1.5mA,<br>T <sub>A</sub> = -40°C to +85°C                 | 75           | 100          | 125           | Ω     |

| SDO low-side (LS) on resistance     | R <sub>SDO_DRV_LOW</sub> | Isink = 1.5mA,<br>T <sub>A</sub> = -40°C to +85°C                   | 38           | 52           | 66            | Ω     |

## TYPICAL PERFORMANCE CHARACTERISTICS

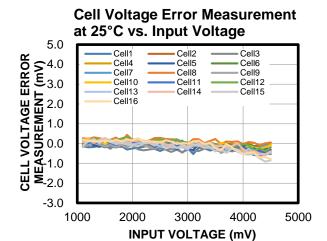

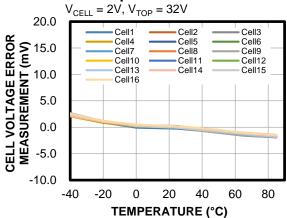

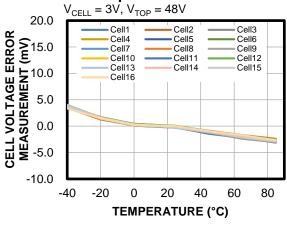

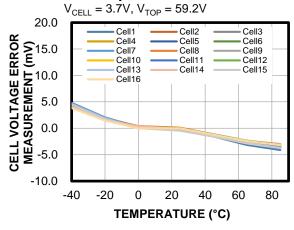

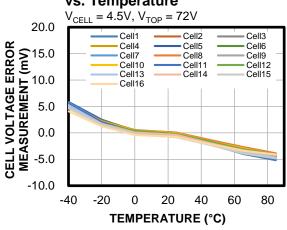

# Cell Voltage Error Measurement vs. Temperature

# **Cell Voltage Error Measurement vs. Temperature**

# Cell Voltage Error Measurement vs. Temperature

# Cell Voltage Error Measurement vs. Temperature

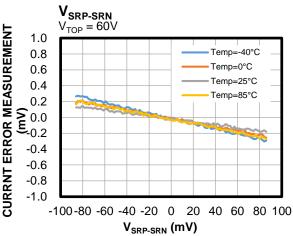

#### **Current Error Measurement vs.**

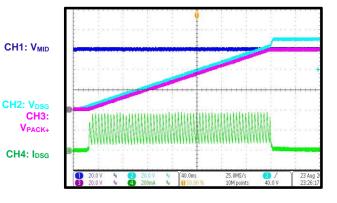

CH1: V<sub>MID</sub>

CH4: I<sub>DSG</sub>

CH3: V<sub>PACK+</sub> CH2:

## TYPICAL PERFORMANCE CHARACTERISTICS

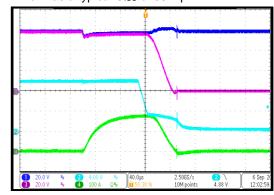

Performance curves and waveforms are tested on the evaluation board.  $V_{TOP} = 60V$ ,  $T_A = 25$ °C, unless otherwise noted.

#### **DSG Soft Start**

PACK+ is connected to a 1mF capacitor, the DSG slope is 0.2V/ms

### **DSG Fast-Off in Short-Circuit**

$R_{SRP-SRN} = 1m\Omega$ , short-circuit threshold is 99mV, deglitch off, 4 paralleled AM90N08-04BA devices act as the DSG N-channel MOSFETs, which has a typical  $C_{ISS}$  of 9924pF

18

## TYPICAL PERFORMANCE WHEN PAIRED WITH MPF4279X FUEL GAUGE

The MP2797 battery monitor includes strictly synchronized cell and pack voltage and current measurements, for the purpose of maximizing state-of-charge (SOC) determination. MPS' MPF4279x family of fuel gauges are designed to take advantage of this feature. This section illustrates the SOC accuracy of the MP2797 battery monitor when combined with MPS' MPF4279x fuel gauge family.

## Constant-Current/Constant-Voltage (CC/CV) Charge and Dynamic Discharge Cycle

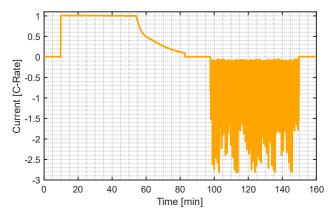

The next scenarios consist of charging a 10S1P (11) battery using the typical CC/CV method, followed by a highly dynamic discharge at different ambient temperatures. The charge constant current rate is 1C, while the charge termination current in this example is 0.1C. The highly dynamic discharge corresponds to a typical e-bike's current profile, with an average current of 1C and maximum peak currents up to 2.8C. Figure 3 shows the current profile of the complete cycle at 25°C.

Figure 3: CC/CV Charge and Dynamic Discharge Current Profile

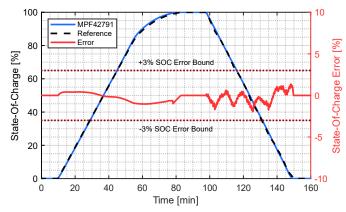

Figure 4 shows the performance of the combined MP2797 and MPF42791 for the CC/CV charge and dynamic discharge cycle at an ambient temperature of 25°C. During charge, the root-mean-squared (RMS) (12) and maximum pack SOC error are 0.61% and 1.03%, respectively. During discharge, the rootmean-squared and pack SOC error are 0.78% and 1.94%, respectively.

#### Notes:

- 11) 10S1P refers to the battery configuration. There are 10 groups of 1 parallel cell connected in series.

- 12) The RMS error is equal to  $\int_{-\infty}^{\infty} \frac{\sum_{n=1}^{N} (\theta_n \hat{\theta}_n)^2}{12}$ where  $\theta$  is the actual SOC,  $\hat{\theta}$  is the estimated SOC, and N is the number of samples.

Figure 4: Combined MP2797 + MPF42791 Performance for a CC/CV Charge and Dynamic Discharge (Ambient Temperature = 25°C)

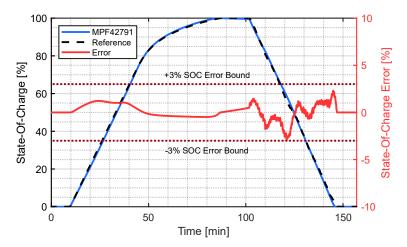

Figure 5 shows the performance of the combined MP2797 and MPF42791 for the CC/CV charge and dynamic discharge cycle at an ambient temperature of 0°C. During charge, the root-mean-squared and maximum pack SOC error are 0.68% and 1.22%, respectively. During discharge, the root-mean-squared and pack SOC error are 1.15% and 2.97%, respectively.

Figure 5: Combined MP2797+MPF42791 Performance for a CC/CV Charge and Dynamic Discharge (Ambient Temperature = 0°C)

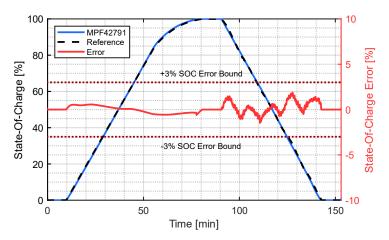

Figure 6 shows the performance of the combined MP2797 and MPF42791 for the CC/CV charge and dynamic discharge cycle at an ambient temperature of 40°C. During charge, the root-mean-squared and maximum pack SOC error are 0.40% and 0.60%, respectively. During discharge, the root-mean-squared and pack SOC error are 0.77% and 1.89%, respectively.

Figure 6: Combined MP2797+MPF42791 Performance for a CC/CV Charge and Dynamic Discharge (Ambient Temperature = 40°C)

#### **Performance Summary**

This section provides a summary the combined MP2797 and MPF42791 real-world performance. Table 1 shows a summary of the pack SOC performance metrics for a 10S1P battery.

Table 1: MPF42791 SOC Root-Mean-Squared (and Maximum) Error

| Test Case         | 0°C           | 25°C          | 40°C          |

|-------------------|---------------|---------------|---------------|

| CC/CV charge      | 0.68% (1.22%) | 0.61% (1.03%) | 0.40% (0.60%) |

| Dynamic discharge | 1.15% (2.97%) | 0.78% (1.94%) | 0.77% (1.89%) |

MP2797 Rev. 1.0 MonolithicPower.com

6/28/2023 MPS Proprietary Information, Patent Protected, Unauthorized Photocopy and Duplication Prohibited

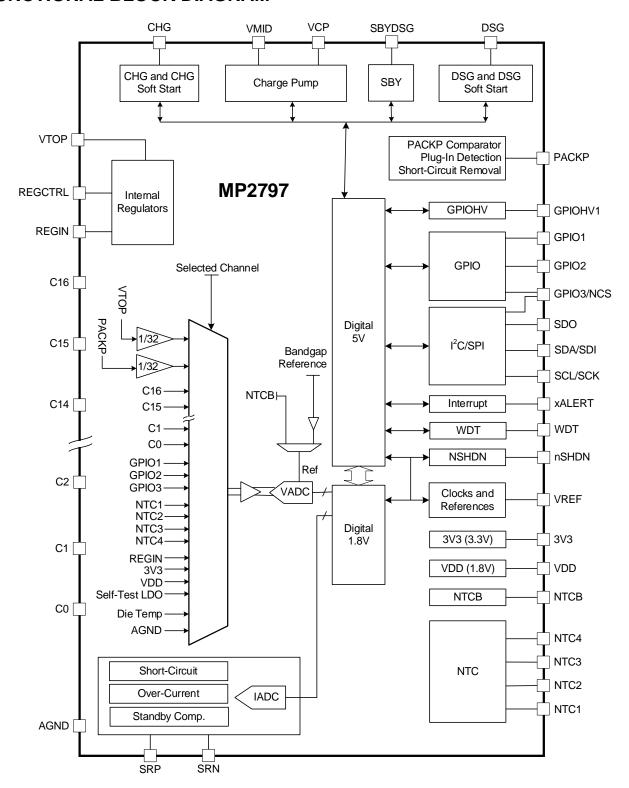

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 7: Functional Block Diagram

#### **OPERATION**

#### **Main Modes**

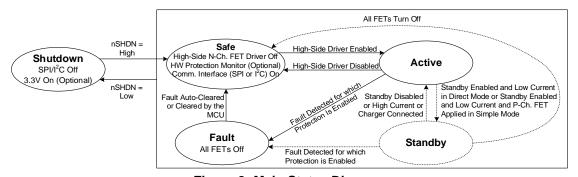

The MP2797's main operation modes are listed and described below (see Figure 8).

#### Shutdown Mode

It is vital to preserve a battery's capacity. Shutdown mode minimizes the amount of leakage from the battery pack, which extends the battery pack's shelf storage life.

In shutdown mode, the communication interface is unavailable and REGIN is loosely regulated, which means its voltage is below the normal voltage without any load capacity. However, it is possible to keep 3.3V active in shutdown mode with a slight margin for current consumption.

Pull the NSHDN pin to ground to enter shutdown mode.

#### Safe Mode

To enter safe mode from shutdown mode, pull up the NSHDN pin and wait at least 5ms before issuing an I<sup>2</sup>C or SPI command. If any functional commands are required in safe mode (e.g. high-resolution voltage scanning, coulomb counting, MOSFETs turn on, voltage protection monitoring, open wire, cell-balancing), then the I<sup>2</sup>C or SPI bus must be idle for at least 200µs after the functional command in enabled.

Safe mode is characterized by the following conditions:

- The protection MOSFETs turn off.

- The over-voltage (OV) and under-voltage (UV) hardware autonomous protection state machine is disabled, unless it is forcibly enabled.

- The communication interface is enabled.

To leave safe mode, see the Protection MOSFET Enable Control section on page 23.

In safe mode, the analog front-end (AFE) provides a P-channel MOSFET bypass function, which is controlled by GPIOHV1.

In safe mode, it is possible enable protection monitoring (cell OV, cell UV, and current monitoring).

#### **Active Mode**

In active mode, the high-side drivers turn on, and the BMS can be powered or be charged by a downstream system through the CHG and DSG N-channel MOSFETs.

#### Standby Mode

Standby mode reduces current consumption by using a standby P-channel MOSFET to power the system (instead of DSG N-channel MOSFET), and conducts through the CHG N-channel MOSFET's body diode. To enter standby mode, standby mode must be enabled, and the current must be below the standby current threshold.

In standby mode, the time between ADC voltage conversions used for protection monitoring can be independently lengthened via the STBY\_MONITOR\_CFG register. This reduces the average current consumption.

#### Fault Mode

In fault mode, both the CHG and DSG MOSFET drivers turn off in response to a fault event. Protection monitoring is still enabled during a fault.

Fault mode can be cleared manually or through automatic fault recovery, depending on the configuration.

Figure 8: Main States Diagram

#### Registers (Default and Lock)

Most of the configuration settings and options have a configurable default value. Certain registers can be configured independently, or they can be locked in read-only mode. This prevents critical safety features from being changed.

#### **Protection MOSFET Enable Control**

The MP2797 can leave safe mode and enter active mode via pin control or register control, though only one control method can be selected at a time. The FET\_SRC register can be set

using either the register (ACTIVE\_CTRL register) or pin (GPIO1/2) to determine whether the device should remain in safe mode or active mode.

There are two control strategies that can be selected via the FET\_CFG register: simple or direct. Table 2 lists the BMS behavior in simple mode, where a single control is offered for both the charge and the discharge driver. The system internally handles the MOSFETs' turn-on and turn-off sequences.

Table 2: Protection MOSFETs (Simple Mode)

| Configuration: FET_SRC = GPIO, Standby P-Channel MOSFET Disabled |                  |       |              |  |  |