# **MPQ2286**

# 6V, 12A, Programmable High Frequency Synchronous Buck Regulator, AEC1-Q100 Qualified

#### **DESCRIPTION**

The MPQ2286 is a configurable, high-frequency, synchronous buck regulator with integrated internal high-side and low-side power MOSFETs (HS-FET and LS-FET, respectively). The MPQ2286 operates from a 2.7V to 6V input voltage ( $V_{IN}$ ) and provides 12A of highly efficient output current ( $I_{OUT}$ ) with fixed-frequency, zero-delay PWM (ZDP<sup>TM</sup>) control for optimal transient response.

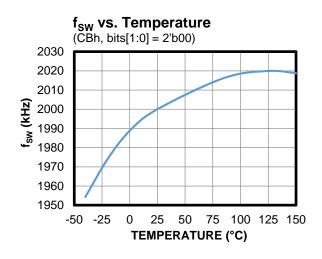

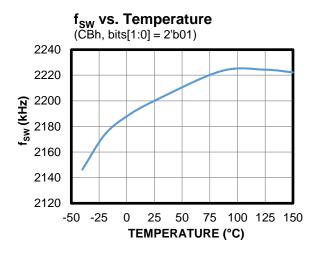

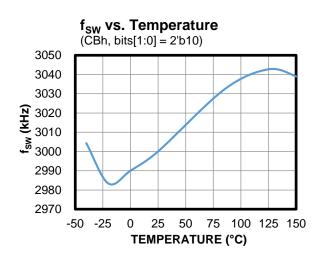

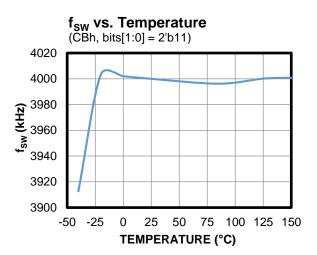

The configurable 2MHz to 4MHz switching frequency (f<sub>SW</sub>) during forced continuous conduction mode (FCCM) greatly reduces the external inductance and capacitance. Internal feedback and compensation minimizes the external component count and improves accuracy.

High power conversion efficiency across the wide load range is achieved by scaling down  $f_{SW}$  under light-load conditions to reduce the switching frequency and gate driving losses. Full protection features include short-circuit protection (SCP), over-current protection (OCP), input over-voltage protection (OVP), output OVP, and thermal shutdown. These protections provide reliable, fault-tolerant operation.

The digital interface features packeting error checking (PEC), and integrated multi-page one-time programmable (OTP) memory allows for a high degree of configurability.

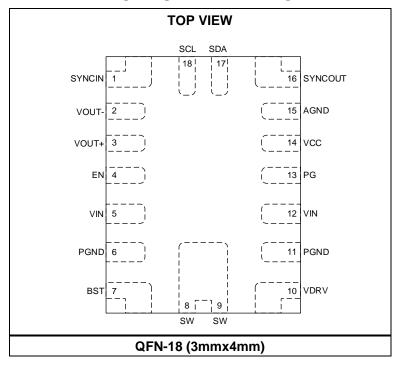

The MPQ2286 is available in a QFN-18 (3mmx4mm) package with wettable flanks. It is available in AEC-Q100 Grade 1.

#### **FEATURES**

10/30/2023

- Designed for Automotive Point-of-Load (PoL) Applications

- 2.7V to 6V Input Voltage (V<sub>IN</sub>)

- 12A Continuous Output Current (I<sub>OUT</sub>)

- 1.0% Output Regulation Accuracy

- Differential Output Voltage (V<sub>OUT</sub>) Sense

- o Internal 6mΩ High-Side MOSFET (HSFET) and 4mΩ Low-Side MOSFET (LSFET)

#### FEATURES (continued)

- Configurable 2MHz to 4MHz Switching Frequency (f<sub>SW</sub>)

- Optimized for EMC/EMI

- Synchronization Input/Output

- Frequency Spread Spectrum (FSS)

- Flexible Application with Digital Interface

- Digital Interface with Cyclic Redundancy Check (CRC)

- Converter On/Off

- V<sub>OUT</sub> Setting Range from 0.20625V to 3.6V

- o Faults Detection

- Factory-Configurable Multi-Page One-Time Programmable (OTP) Memory

- Protections

- Peak and Valley Current Limit

- Over-Current Protection (OCP)

- Short Circuit Protection (SCP)

- Output Over Voltage Protection (OVP)

- Input OVP

- Thermal Warning

- o Over-Temperature Shutdown

- Additional Features

- Soft Start and Soft Stop

- Power Good

- Available in a QFN-18 (3mmx4mm)

Package with Wettable Flanks

- Available in AEC-Q100 Grade 1

- Functional Safety System Design Capable

- MPSafe™ QM Documentation Available

#### **APPLICATIONS**

- Advanced Driver Assistance Systems (ADAS)

- Infotainment

- System-On-Chip (SOC) System Cores

- DDR Memory

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

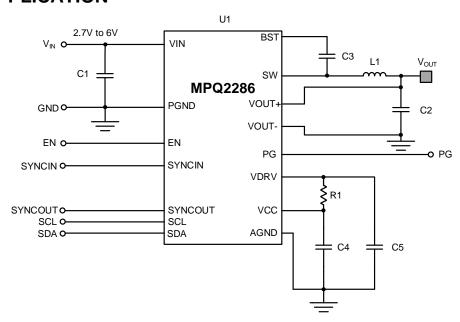

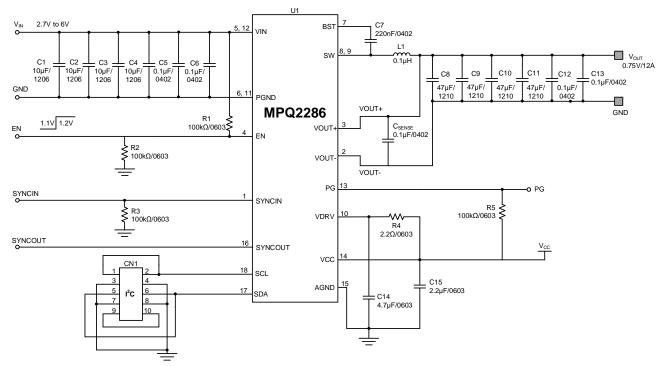

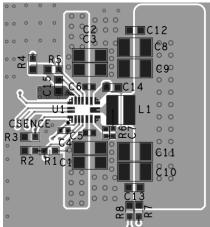

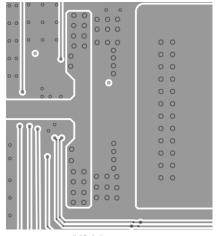

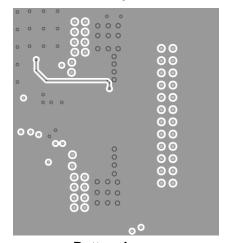

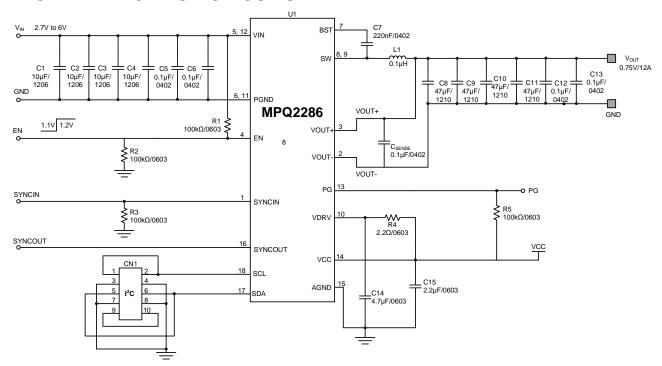

## TYPICAL APPLICATION

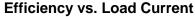

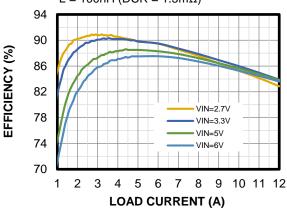

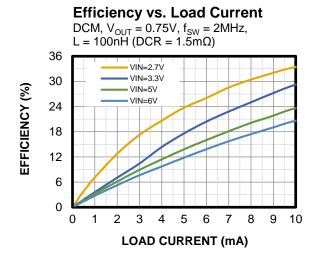

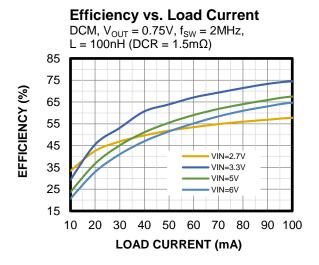

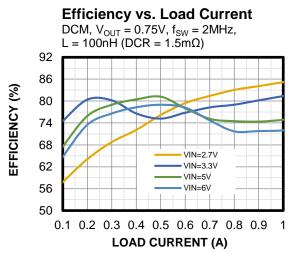

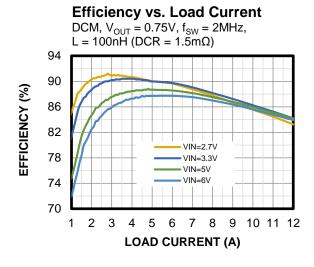

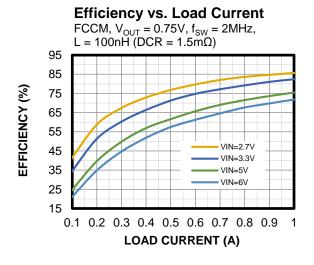

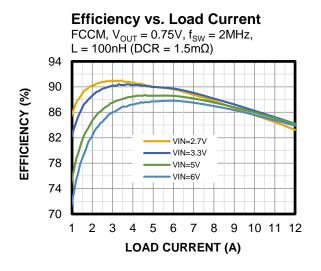

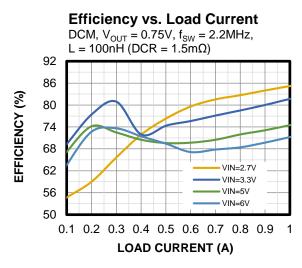

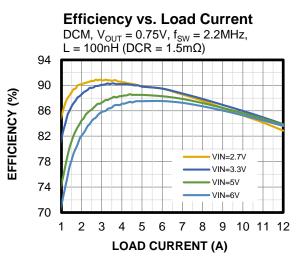

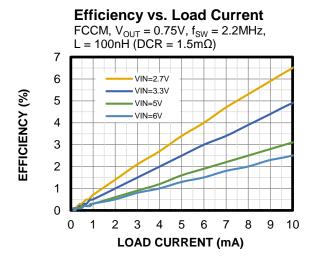

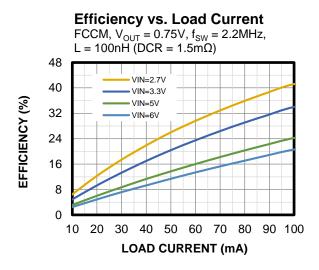

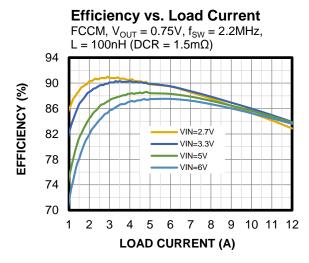

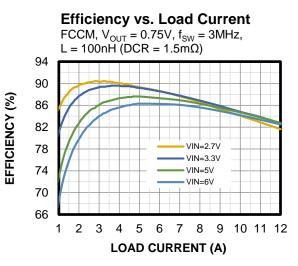

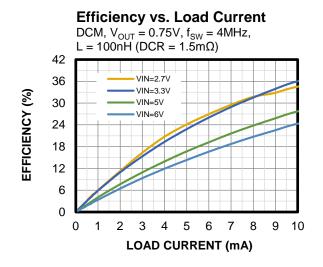

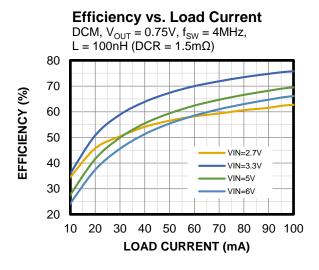

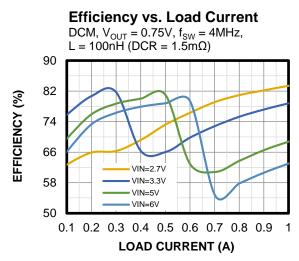

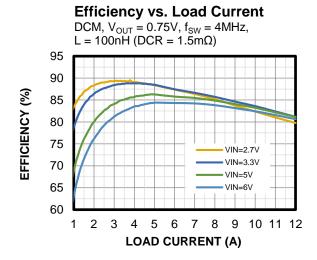

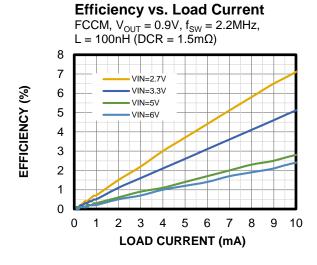

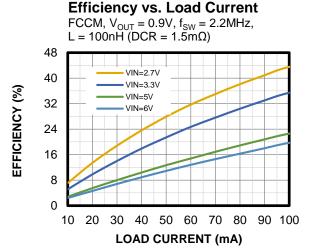

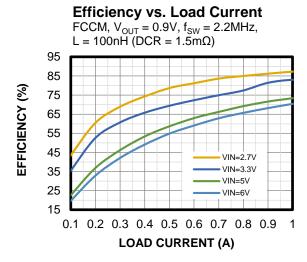

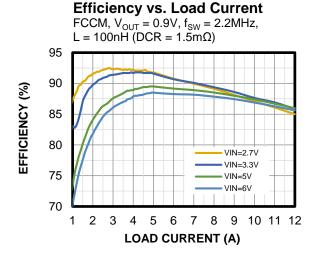

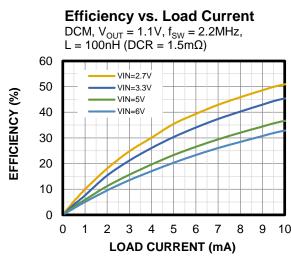

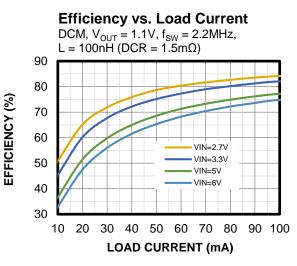

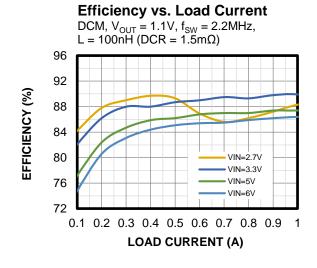

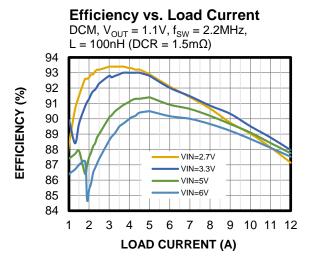

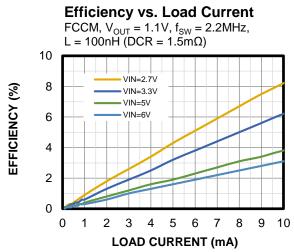

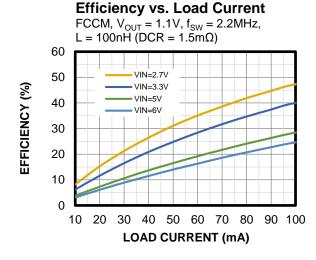

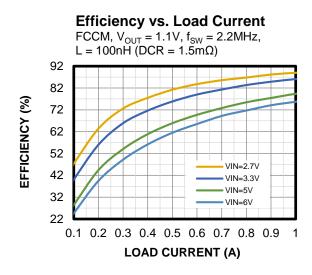

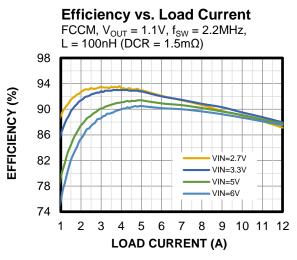

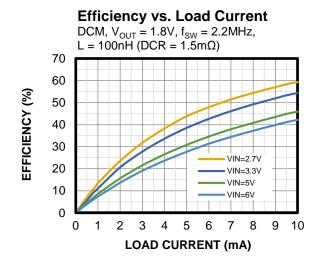

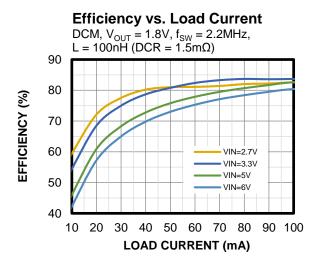

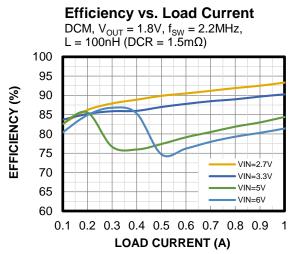

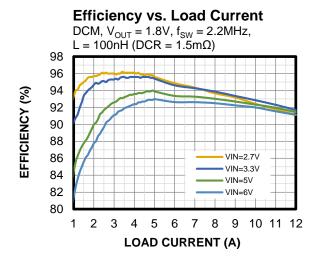

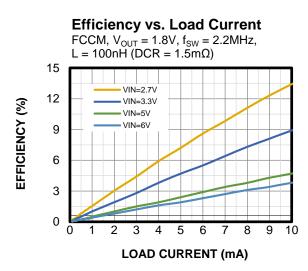

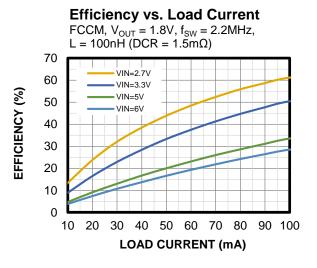

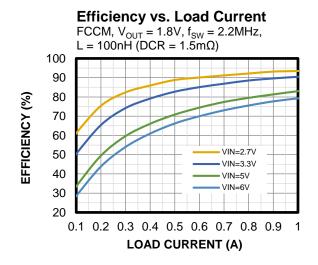

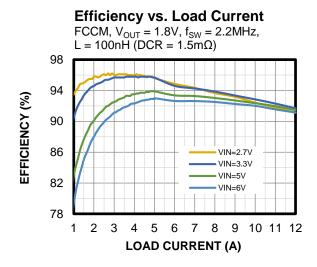

## **Efficiency vs. Load Current**

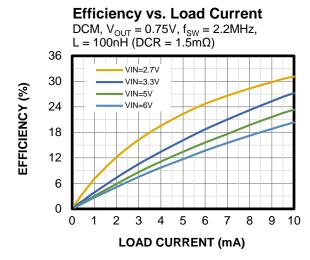

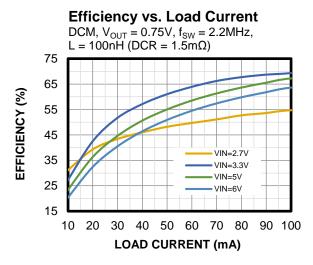

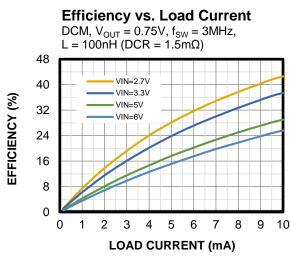

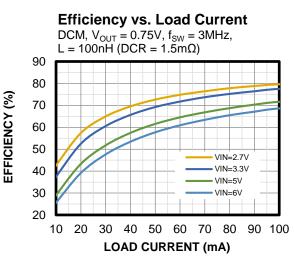

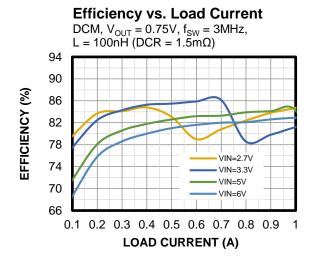

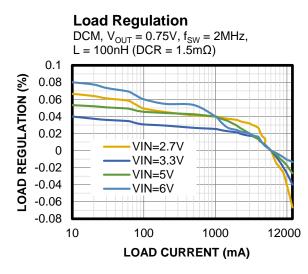

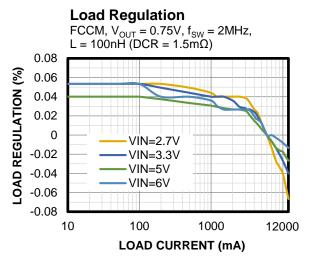

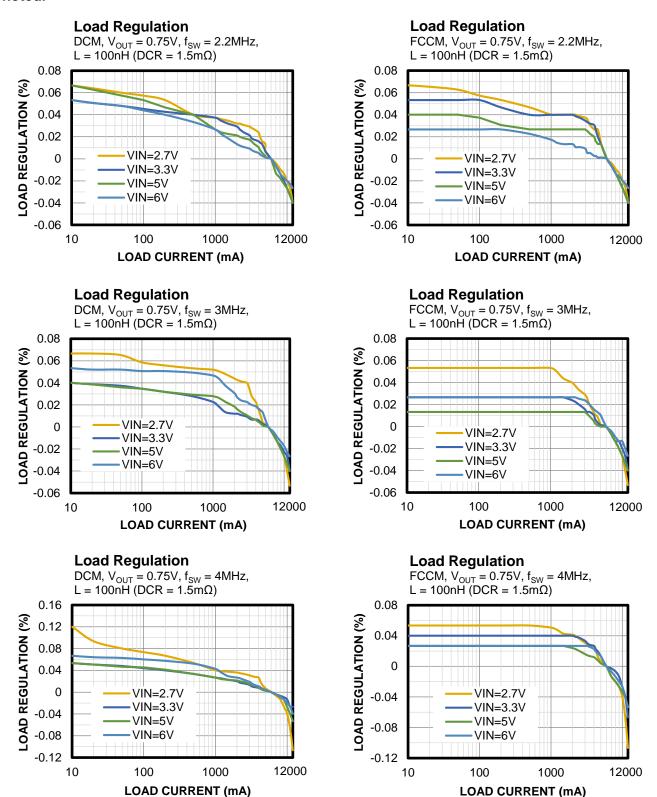

DCM,  $V_{OUT} = 0.75V$ ,  $f_{SW} = 2MHz$ , L = 100nH (DCR =  $1.5m\Omega$ )

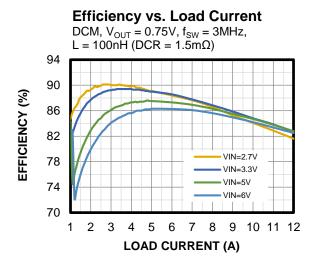

DCM,  $V_{OUT} = 0.75V$ ,  $f_{SW} = 3MHz$ , L = 100nH (DCR = 1.5m $\Omega$ )

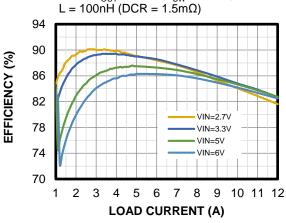

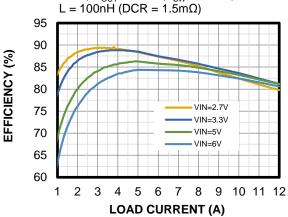

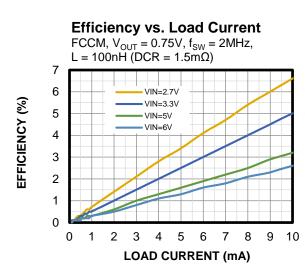

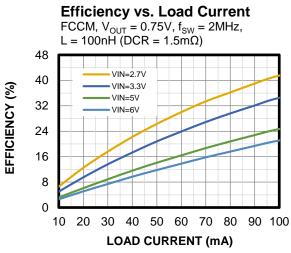

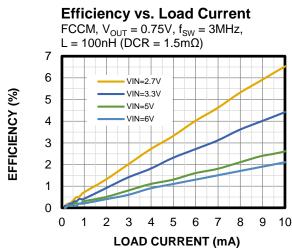

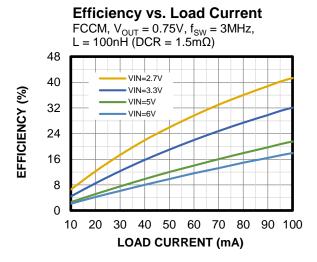

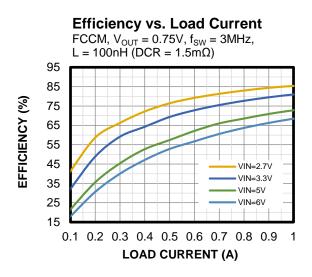

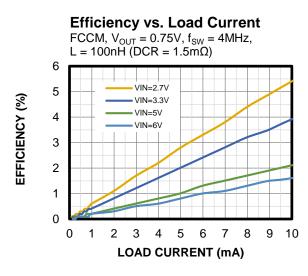

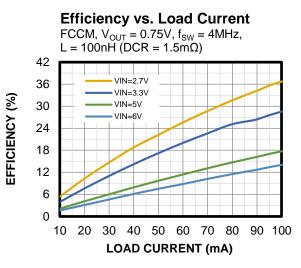

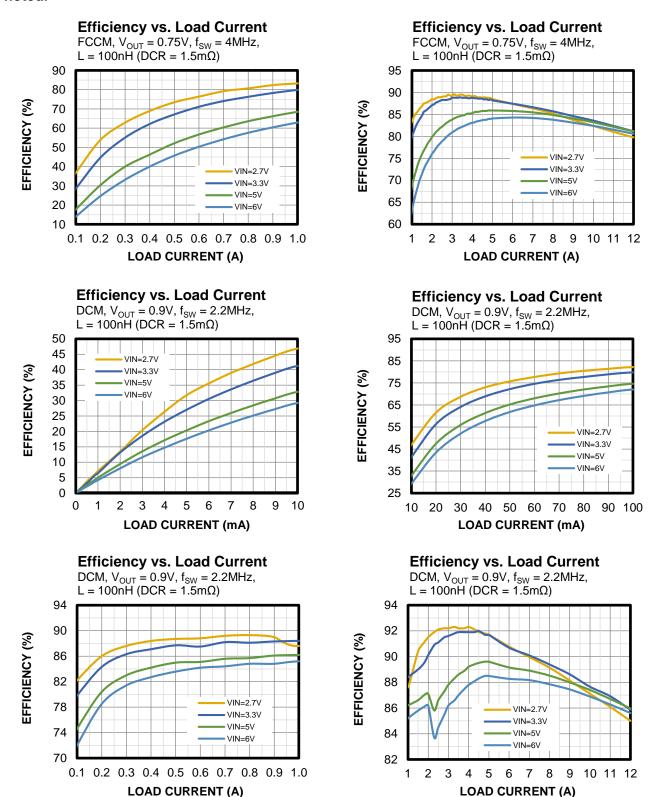

#### **Efficiency vs. Load Current**

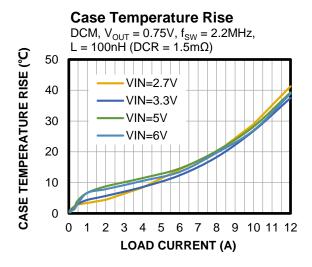

DCM,  $V_{OUT} = 0.75V$ ,  $f_{SW} = 2.2MHz$ , L = 100nH (DCR = 1.5m $\Omega$ )

#### **Efficiency vs. Load Current**

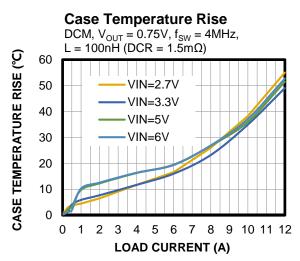

DCM,  $V_{OUT} = 0.75V$ ,  $f_{SW} = 4MHz$ ,

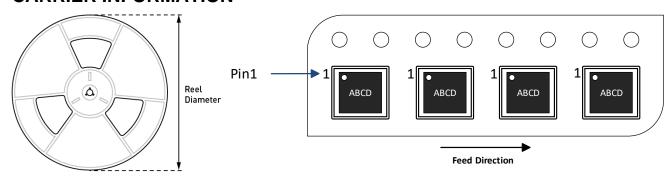

#### ORDERING INFORMATION

| Part Number*                  | Package          | Top Marking | MSL Rating*** |

|-------------------------------|------------------|-------------|---------------|

| MPQ2286GLE-xxxx-AEC1 **, **** | QFN-18 (3mmx4mm) | See Below   | 1             |

<sup>\*</sup> For Tape & Reel, add suffix -Z (e.g. MPQ2286GLE-xxxx-AEC1-Z).

\*\*\*Moisture Sensitivity Level Rating

\*\*\*\* Wettable flank

#### TOP MARKING

MPYW 2286 LLL E

MP: MPS prefix Y: Year code W: Week code 2286: Part number LLL: Lot number E: Wettable Flank

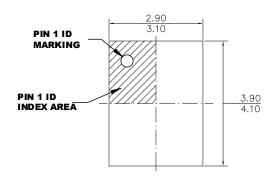

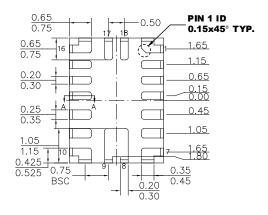

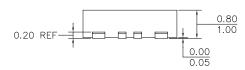

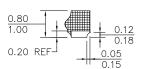

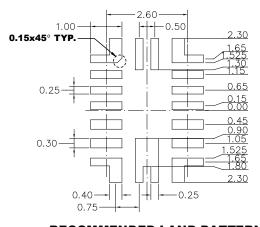

#### **PACKAGE REFERENCE**

<sup>\*\* &</sup>quot;xxxx" is the configuration code identifier for the register settings stored in the OTP register. The first value must be a numerical value (0–9), while the last three values can be a hexadecimal value between 0 and F. The default code is "0000". Contact an MPS FAE to create this unique number.

# **PIN FUNCTIONS**

| Pin#  | Name    | Description                                                                                                                                                                                                                                                                                                                          |

|-------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | SYNCIN  | <b>SYNC input.</b> Apply a clock signal to the SYNCN pin to synchronize the internal oscillator frequency to the external clock. Use an external clock to enter forced continuous conduction mode (FCCM). The MPQ2286 can also be set to FCCM via the digital interface. Connect SYNCIN to GND through a resistor if it is not used. |

| 2     | VOUT-   | Output negative differential sense. Connect VOUT- to the negative side of the output capacitor.                                                                                                                                                                                                                                      |

| 3     | VOUT+   | Output positive differential sense. Connect VOUT+ to the positive side of the output capacitor.                                                                                                                                                                                                                                      |

| 4     | EN      | <b>Enable.</b> Pull the EN pin below the specified threshold (1.1V) to shut down the chip. Pull EN above the specified threshold (1.2V) to enable the chip. There is an internal $200k\Omega$ pull-down resistor.                                                                                                                    |

| 5, 12 | VIN     | <b>Input supply.</b> The VIN pins are connected internally. VIN supplies power to the internal low-dropout (LDO) regulator, control circuitry, and the power switch connected to SW. It is recommended to connect a decoupling capacitor from VIN to ground, and placed close to VIN to minimize switching spikes.                   |

| 6, 11 | PGND    | Power ground. The PGND pins are connected internally.                                                                                                                                                                                                                                                                                |

| 7     | BST     | <b>Bootstrap supply.</b> The BST pin is the positive power supply for the high-side MOSFET driver connected to SW. Connect a 0.22µF bypass capacitor between the BST and SW pins.                                                                                                                                                    |

| 8,9   | SW      | <b>Switch node</b> . SW is the output of the internal power switch. Connect SW to the power inductor.                                                                                                                                                                                                                                |

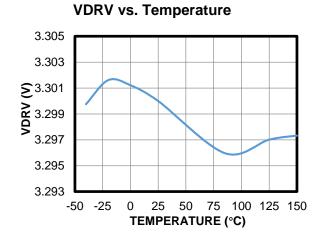

| 10    | VDRV    | Internal LDO decoupling pin and supply input for internal power circuits. Connect a 4.7μF capacitor from VDRV to PGND. Connect a 2.2Ω resistor between VCC and VDRV.                                                                                                                                                                 |

| 13    | PG      | <b>Power good indicator.</b> The PG pin is an open-drain output. PG asserts if the output is not within regulation, or if an error has occurred. This pin can be configured via the digital interface. Connect PG to GND through a resistor if it is not used.                                                                       |

| 14    | VCC     | Supply input for internal analog and digital circuits. Connect a $2.2\mu F$ capacitor from VCC to AGND. Connect a $2.2\Omega$ resistor between VCC and VDRV.                                                                                                                                                                         |

| 15    | AGND    | Analog ground.                                                                                                                                                                                                                                                                                                                       |

| 16    | SYNCOUT | SYNC output. SYNCOUT outputs a 0° or 180° out-of-phase clock to the other devices.                                                                                                                                                                                                                                                   |

| 17    | SDA     | <b>Digital interface serial data.</b> This pin is an open-drain port and cannot be floated. Use an external pull-up resistor to connect this pin to the supply rail of the digital interface. Connect this pin to GND if it is not used.                                                                                             |

| 18    | SCL     | <b>Digital interface serial clock.</b> This pin is an open-drain port and cannot be floated. Use an external pull-up resistor to connect this pin to the supply rail of the digital interface. Connect this pin to GND if it is not used.                                                                                            |

#### **ABSOLUTE MAXIMUM RATINGS** (1)

| V <sub>IN</sub> , V <sub>SW</sub>      | 0.3V to +8.5V                  |

|----------------------------------------|--------------------------------|

| V <sub>BST</sub>                       | 0.3V to 4V + $V_{SW}$          |

| All other pins                         | 0.3V to +4V                    |

| Continuous power dissipation           | $(T_A = 25^{\circ}C)^{(2)(6)}$ |

| QFN-18 (3mmx4mm)                       | 4.59W                          |

| Junction temperature (T <sub>J</sub> ) | 150°C                          |

| Lead temperature                       | 260°C                          |

#### ESD Ratings

| Human body model (HE   | вM)   | Class 2 <sup>(3)</sup> |

|------------------------|-------|------------------------|

| Charged-device model ( | (CDM) | ) Class C2b(4)         |

#### **Recommended Operating Conditions**

| Input voltage (V <sub>IN</sub> ) | 2.7V to 6V                     |

|----------------------------------|--------------------------------|

| Output voltage (Vout)            |                                |

| Operating junction temp (        | T <sub>J</sub> )40°C to +150°C |

#### Thermal Resistance $\theta_{JA}$ $\theta_{JC}$

QFN-18 (3mmx4mm) JESD51-7......44.67....4.2...°C/W <sup>(5)</sup> EVQ2286-L-00A......27.22...2.86..°C/W <sup>(6)</sup>

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature,  $T_J$  (MAX), the junction-to-ambient thermal resistance,  $\theta_{JA}$ , and the ambient temperature,  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) =  $(T_J$  (MAX)  $T_A$ ) /  $\theta_{JA}$ . Exceeding the maximum allowable power dissipation can cause excessive die temperature, and the regulator may go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- Per AEC-Q100-002.

- 4) Per AEC-Q100-011.

- 5) Measured on a JESD51-7, 4-layer PCB. The values given in this table are only valid for comparison with other packages and cannot be used for design purposes. These values were calculated in accordance with JESD51-7, and simulated on a specified JEDEC board. They do not represent the performance obtained in an actual application. The value of  $\theta_{\rm JC}$  shows the thermal resistance from junction-to-case bottom.

- 6) Measured on an MPS standard EVB, 6.35cmx6.35cm, 2oz copper thickness, 4-layer PCB. The value of  $\theta_{JC}$  shows the thermal resistance from junction-to-case top.

## **ELECTRICAL CHARACTERISTICS**

Typical values are  $V_{IN} = 5V$ ,  $V_{EN} = 2V$ ,  $T_J = 25^{\circ}$ C, all voltages with respect to ground, unless otherwise noted. Minimum and maximum values are at  $V_{IN} = 5V$ ,  $V_{EN} = 2V$ ,  $T_J = -40^{\circ}$ C to +150°C, all voltages with respect to ground, guaranteed by characterization, unless otherwise noted.

| Parameter                                                                     | Symbol                | Condition                                                                 | Min         | Тур          | Max | Units |

|-------------------------------------------------------------------------------|-----------------------|---------------------------------------------------------------------------|-------------|--------------|-----|-------|

| Input Supply Voltage                                                          |                       |                                                                           | •           |              | •   | •     |

| Input voltage (V <sub>IN</sub> ) undervoltage lockout (UVLO) rising threshold | V <sub>IN_UVLO</sub>  |                                                                           | 2.4         |              | 2.7 | V     |

| V <sub>IN</sub> UVLO hysteresis                                               | VIN_UVLO_HYS          |                                                                           |             | 150          |     | mV    |

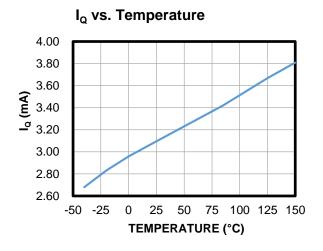

| VIN quiescent current                                                         | I <sub>Q_ON</sub>     | Buck on, no switching                                                     |             |              | 7   | mA    |

| VIN shutdown current                                                          | $I_{Q_OFF}$           | Buck off, enable low                                                      |             |              | 20  | μA    |

| VDRV Regulator                                                                |                       |                                                                           |             |              |     |       |

| VDRV regulation voltage                                                       | V <sub>VDRV</sub>     | $C = 2.2\mu F$ , IVCC = 20mA, $V_{IN} = 5V$                               | 3.1         | 3.3          | 3.5 | ٧     |

| \/DD\/                                                                        |                       | VDRV = 2.7V, V <sub>IN</sub> = 5V                                         |             | 100          |     | mA    |

| VDRV current limit                                                            | Ivdrv                 | VDRV = 0V, V <sub>IN</sub> = 5V                                           |             | 100          |     | mA    |

| Oscillator                                                                    |                       |                                                                           |             |              | •   | •     |

| Switching frequency range                                                     | fsw                   |                                                                           | 2           |              | 4   | MHz   |

| Switching frequency accuracy                                                  | fsw_acc               |                                                                           | -10         |              | +10 | %     |

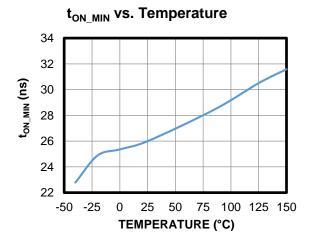

| Minimum on time                                                               | ton_min               | V <sub>IN</sub> = 5V,<br>V <sub>OUTP</sub> = 2 x VOUT_SCALE               |             | 26           | 45  | ns    |

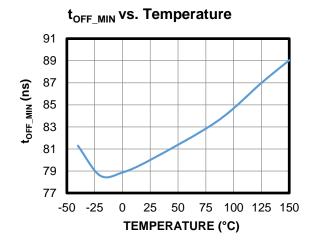

| Minimum off time                                                              | toff_min              |                                                                           |             | 80           |     | ns    |

| Minimum frequency                                                             | f <sub>SW_MIN</sub>   | Ultrasonic mode enabled                                                   | 40          |              | 50  | kHz   |

| Spread spectrum modulation frequency spread                                   | fss_spread            |                                                                           |             | -7.5<br>+6.5 |     | %     |

| Spread spectrum modulation frequency rate                                     | f <sub>SS_RATE</sub>  |                                                                           |             | 9            |     | kHz   |

| Dynamic Output Voltage (                                                      | <b>V</b> оит <b>)</b> |                                                                           |             |              |     |       |

| VOUT output range (9)(10)                                                     | Vоит                  |                                                                           | 0.206<br>25 |              | 3.6 | V     |

|                                                                               |                       | V <sub>OUT</sub> ≥ 0.5V x VOUT_SCALE, as a percentage of V <sub>OUT</sub> | -1          |              | +1  | %     |

| V <sub>OUT</sub> accuracy                                                     | Vout_acc              | VOUT_SCALE = 1,<br>Vout < 0.5V                                            | -5          |              | +5  | mV    |

|                                                                               |                       | VOUT_SCALE = 2, V <sub>OUT</sub> < 1V                                     | -10         |              | +10 | mV    |

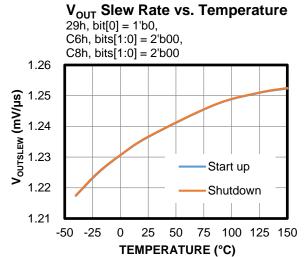

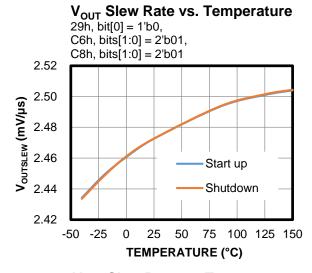

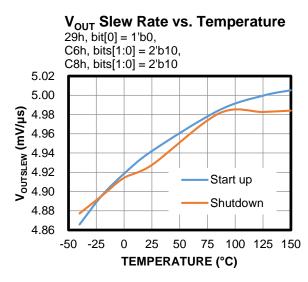

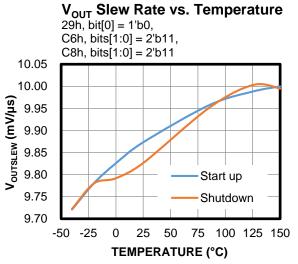

| V <sub>OUT</sub> start-up slew rate range <sup>(9)</sup>                      | Voutslew_st           |                                                                           | 1.25        |              | 10  | mV/µs |

| V <sub>OUT</sub> start-up slew rate accuracy                                  | Voutslew_st_acc       |                                                                           | -15         |              | +15 | %     |

Typical values are  $V_{\text{IN}}$  = 5V,  $V_{\text{EN}}$  = 2V,  $T_{\text{J}}$  = 25°C, all voltages with respect to ground, unless otherwise noted. Minimum and maximum values are at  $V_{IN}$  = 5V,  $V_{EN}$  = 2V,  $T_J$  = -40°C to +150°C, all voltages with respect to ground, guaranteed by characterization, unless otherwise noted.

| Parameter                                                | Symbol                    | Condition            | Min  | Тур | Max | Units |

|----------------------------------------------------------|---------------------------|----------------------|------|-----|-----|-------|

| V <sub>OUT</sub> shutdown slew rate range <sup>(9)</sup> | Voutslew_sp               |                      | 1.25 |     | 10  | mV/µs |

| V <sub>OUT</sub> shutdown slew rate accuracy             | Voutslew_sp_acc           |                      | -15  |     | +15 | %     |

| V <sub>OUT</sub> dynamic slew rate range <sup>(9)</sup>  | Voutslew                  |                      | 2.5  |     | 20  | mV/μs |

| V <sub>OUT</sub> dynamic slew rate accuracy              | Voutslew_acc              |                      | -15  |     | +15 | %     |

| Power Stage                                              |                           |                      |      |     |     |       |

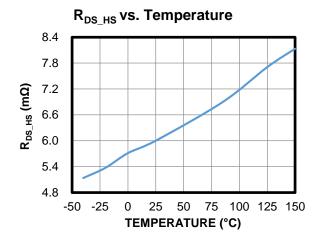

| High-side (HS) switch on resistance                      | R <sub>DS_HS</sub>        |                      |      | 6   | 12  | mΩ    |

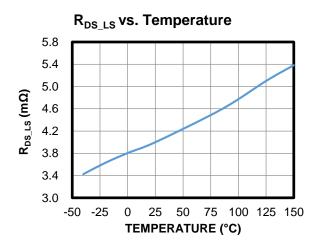

| Low-side (LS) switch on resistance                       | R <sub>DS_LS</sub>        |                      |      | 4   | 8   | mΩ    |

| HS switch leakage current                                | lileak_hs                 | V <sub>DS</sub> = 6V |      |     | 200 | μA    |

| LS switch leakage current                                | IILEAK_LS                 | $V_{DS} = 6V$        |      |     | 200 | μΑ    |

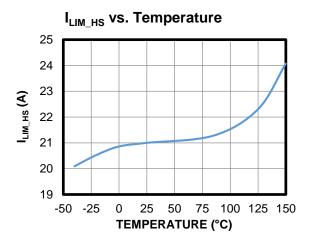

| Peak current limit (9)                                   | I <sub>LIM_HS_BUCK</sub>  | ILIM_SCALE = 100%    | 18   | 21  | 27  | Α     |

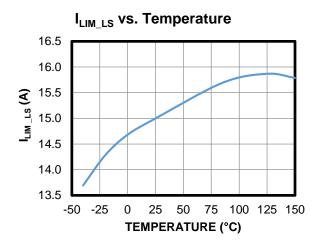

| Valley current limit (9)                                 | ILIM_LS_BUCK              | ILIM_SCALE = 100%    | 12   | 15  | 18  | Α     |

| Zero-current detection (ZCD) current                     | Izcd_buck                 |                      |      |     | 500 | mA    |

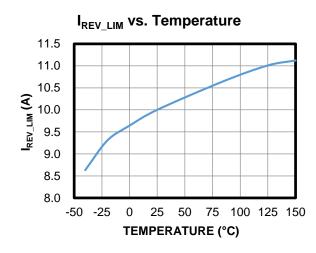

| Reverse current limit                                    | I <sub>REV_BUCK</sub>     |                      |      | 10  |     | Α     |

| Facility of the state of                                 | <b>R</b> ғв1_виск         | VOUT_SCALE = 1       | 20   |     |     | kΩ    |

| Feedback leakage                                         | R <sub>FB2_В</sub> иск    | VOUT_SCALE = 2       | 20   |     |     | kΩ    |

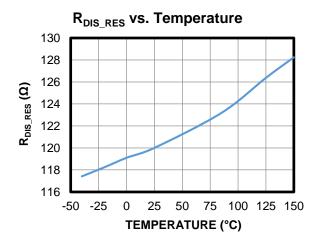

| Output discharge                                         | R <sub>DIS_BUCK</sub>     |                      |      | 120 |     | Ω     |

| <b>Bootstrap Supply</b>                                  |                           |                      | 1    | •   |     |       |

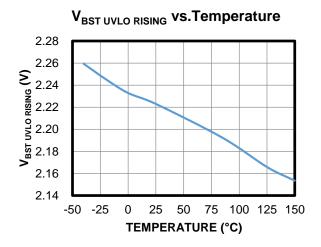

| Bootstrap UVLO rising threshold                          | V <sub>BST_UVLO</sub>     |                      |      |     | 2.5 | V     |

| Bootstrap UVLO<br>Hysteresis                             | V <sub>BST_UVLO_HYS</sub> |                      | 0.2  |     |     | V     |

| Thermal Protection                                       |                           |                      |      |     |     |       |

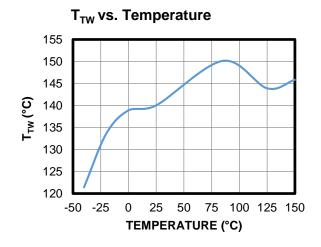

| Thermal warning rising threshold <sup>(7)</sup>          | Ттw                       |                      | 125  | 140 | 155 | °C    |

| Thermal warning hysteresis                               | T <sub>TW_HY</sub> s      |                      |      | 20  |     | °C    |

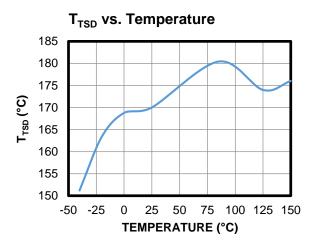

| Thermal shutdown rising threshold <sup>(7)</sup>         | T <sub>TSD</sub>          |                      | 155  | 170 | 185 | °C    |

| Thermal shutdown hysteresis                              | T <sub>TSD_HYS</sub>      | _                    |      | 20  |     | °C    |

Typical values are  $V_{\text{IN}}$  = 5V,  $V_{\text{EN}}$  = 2V,  $T_{\text{J}}$  = 25°C, all voltages with respect to ground, unless otherwise noted. Minimum and maximum values are at  $V_{IN}$  = 5V,  $V_{EN}$  = 2V,  $T_J$  = -40°C to +150°C, all voltages with respect to ground, guaranteed by characterization, unless otherwise noted.

| Parameter                                             | Symbol                     | Condition       | Min  | Тур  | Max  | Units |

|-------------------------------------------------------|----------------------------|-----------------|------|------|------|-------|

| Output Voltage Protection                             |                            |                 |      |      |      |       |

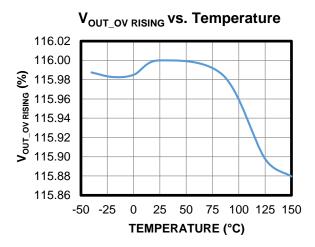

| V <sub>OUT</sub> over-voltage (OV) rising threshold   | Vоит_оv                    |                 | 113  | 116  | 119  | %     |

| Vout OV hysteresis                                    | Vout_ov_hys                |                 |      | 7    |      | %     |

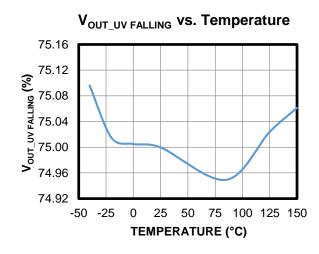

| V <sub>OUT</sub> under-voltage (UV) falling threshold | Vоит_uv                    |                 | 70   | 75   | 80   | %     |

| V <sub>OUT</sub> UV hysteresis                        | Vout_uv_hys                |                 |      | 7    |      | %     |

| Hiccup time range (9)                                 | thick                      |                 | 2    |      | 8    | ms    |

| Input Over-Voltage Protect                            | ion                        |                 |      |      |      |       |

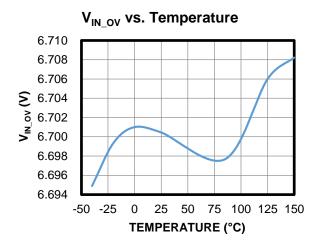

| V <sub>IN</sub> OV rising threshold                   | $V_{IN_{-}OV}$             |                 | 6.5  | 6.7  | 6.85 | V     |

| V <sub>IN</sub> OV hysteresis                         | V <sub>IN_OV_HYS</sub>     |                 |      | 0.7  |      | V     |

| V <sub>IN</sub> OV delay time                         | tvin_ov                    |                 |      | 7    |      | μs    |

| Enable                                                |                            |                 |      |      |      |       |

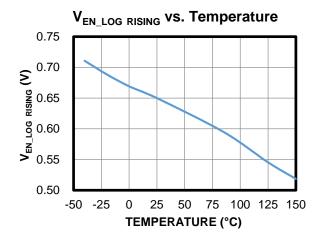

| EN logic on rising threshold                          | $V_{EN\_LOG}$              |                 | 0.25 | 0.65 | 1    | V     |

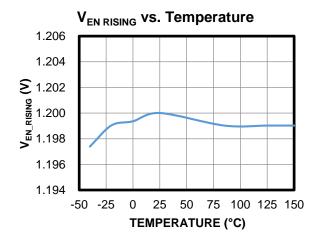

| EN rising threshold                                   | $V_{EN}$                   |                 | 1.1  | 1.2  | 1.3  | V     |

| EN voltage hysteresis                                 | V <sub>EN_HYS</sub>        |                 |      | 100  |      | mV    |

| EN leakage                                            | I <sub>EN</sub>            | $V_{EN} = 3.3V$ |      |      | 10   | μΑ    |

| Power Good (PG)                                       |                            |                 |      |      |      |       |

| PG OV rising threshold (9)                            | PG <sub>ov_th</sub>        | PG_OV_TH = 0    | 103  | 104  | 105  | %     |

| PG OV fishing timeshold V                             | P GOV_IH                   | PG_OV_TH = 1    | 105  | 106  | 107  | %     |

| PG OV threshold hysteresis                            | PG <sub>OV_HYS</sub>       |                 |      | 0.8  |      | %     |

| PG UV falling threshold (9)                           | PG <sub>UV_TH</sub>        | PG_UV_TH = 0    | 95   | 96   | 97   | %     |

| PG OV falling threshold V                             | F GUV_IH                   | PG_UV_TH = 1    | 93   | 94   | 95   | %     |

| PG UV threshold hysteresis                            | PG <sub>UV_HYS</sub>       |                 |      | 0.8  |      | %     |

| PG sink capability                                    | $I_{PG}$                   | $I_{PG} = 1mA$  |      |      | 300  | mV    |

| PG delay range (9)                                    | tpg_delay                  |                 | 0    |      | 10   | ms    |

| PG rising deglitch                                    | tpg_r_deglitch             |                 |      | 20   |      | μs    |

| PG falling deglitch                                   | t <sub>PG_F_DEGLITCH</sub> |                 |      | 20   |      | μs    |

Typical values are  $V_{IN} = 5V$ ,  $V_{EN} = 2V$ ,  $T_J = 25^{\circ}$ C, all voltages with respect to ground, unless otherwise noted. Minimum and maximum values are at  $V_{IN} = 5V$ ,  $V_{EN} = 2V$ ,  $T_J = -40^{\circ}$ C to +150°C, all voltages with respect to ground, guaranteed by characterization, unless otherwise noted.

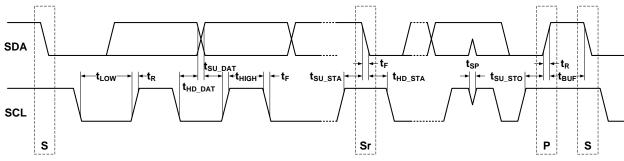

| Parameter                                                       | Symbol              | Condition        | Min                          | Тур | Max  | Units |

|-----------------------------------------------------------------|---------------------|------------------|------------------------------|-----|------|-------|

| SCL/SDA input logic low                                         | VIL                 |                  | 0                            |     | 0.4  | V     |

| SCL/SDA input logic high                                        | VIH                 |                  | 1.2                          |     |      | V     |

| SCL/SDA output logic low                                        | $V_{OL}$            | $I_{LOAD} = 3mA$ |                              |     | 0.4  | V     |

| SCL clock frequency (7)                                         | f <sub>SCL</sub>    |                  |                              |     | 1000 | kHz   |

| SCL high time (7)                                               | tніgн               |                  | 0.26                         |     |      | μs    |

| SCL low time (7)                                                | tLOW                |                  | 0.5                          |     |      | μs    |

| Data set-up time (7)                                            | t <sub>SU_DAT</sub> |                  | 50                           |     |      | ns    |

| Data hold time (7)                                              | thd_dat             |                  | 0                            |     |      | μs    |

| Set-up time for repeated start (7)                              | tsu_sta             |                  | 0.26                         |     |      | μs    |

| Hold time for start (7)                                         | thd_sta             |                  | 0.26                         |     |      | μs    |

| Bus free time between a start and a stop command <sup>(7)</sup> | t <sub>BUF</sub>    |                  | 0.5                          |     |      | μs    |

| Set-up time for stop command (7)                                | tsu_s⊤o             |                  | 0.26                         |     |      | μs    |

| Rising time of SCL/SDA (7)                                      | t <sub>R</sub>      |                  | 20 + 0.1 x<br>C <sub>B</sub> |     | 300  | ns    |

| Falling time of SCL/SDA (7)                                     | t⊧                  |                  | 20 + 0.1 x<br>C <sub>B</sub> |     | 300  | ns    |

| Pulse width of suppressed spike <sup>(7)</sup>                  | t <sub>SP</sub>     |                  | 0                            |     | 50   | ns    |

| Capacitance bus for each bus line (7)                           | Св                  |                  |                              |     | 550  | pF    |

#### Notes:

- 7) Derived from bench characterization. Not tested in production.

- 8) The power good threshold is based on the nominal output voltage.

- 9) Use the write register to set the EC parameters. See the Register Map section starting on page 44 for a detailed description.

- 10) Set VOUT\_SCALE to 1 when Vout is between 0.20625V and 1.8V. If Vout is between 1.8V and 3.6V, set VOUT\_SCALE to 2.

S: Start Command

Sr: Repeated Start Command

P: Stop Command

Figure 1: Digital Compatible Interface Timing Diagram

#### TYPICAL CHARACTERISTICS

#### TYPICAL PERFORMANCE CHARACTERISTICS

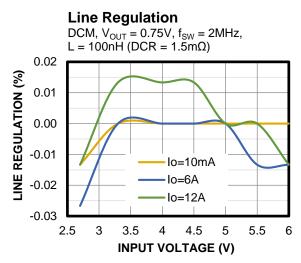

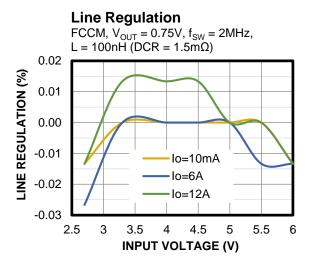

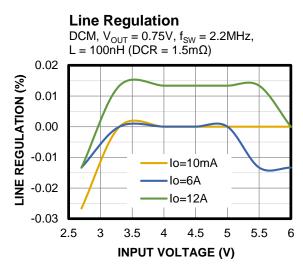

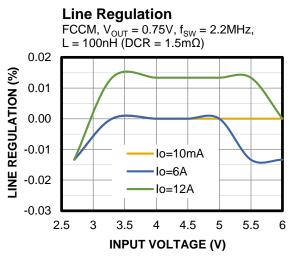

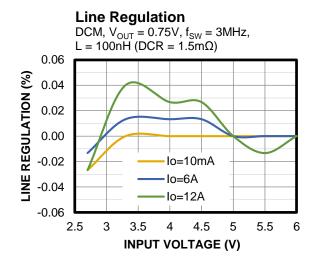

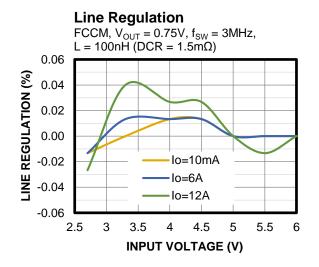

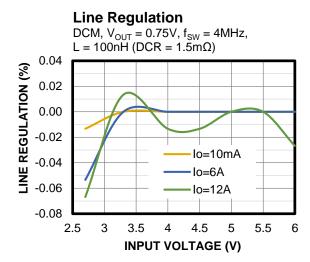

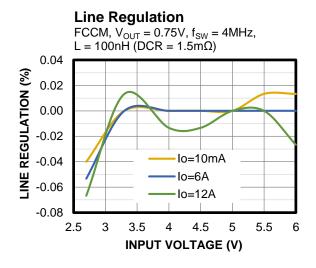

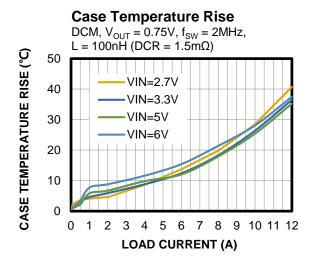

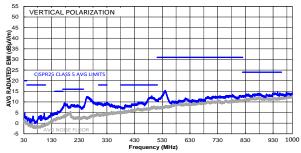

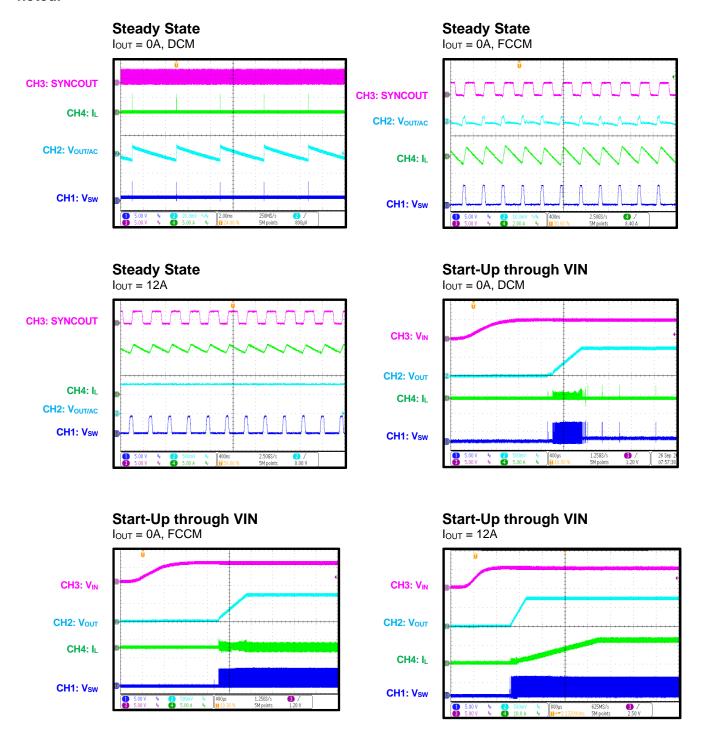

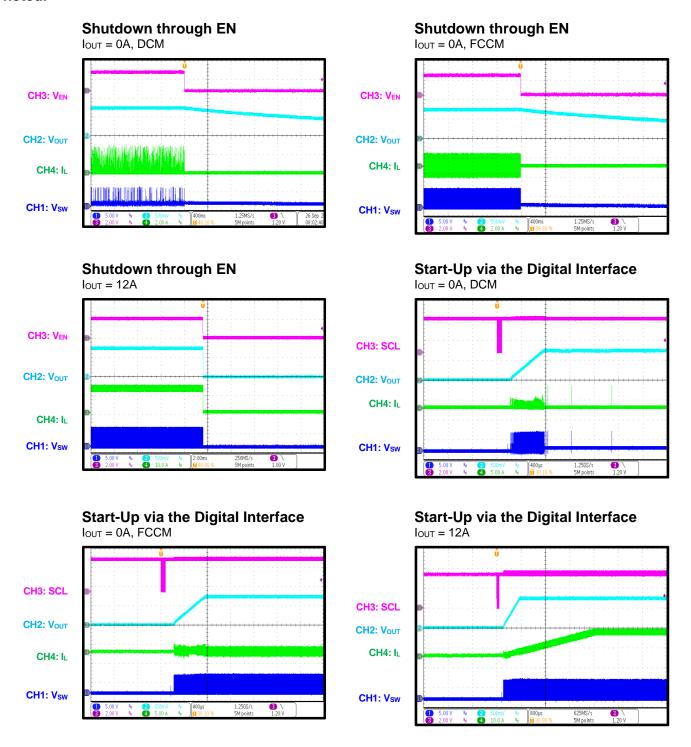

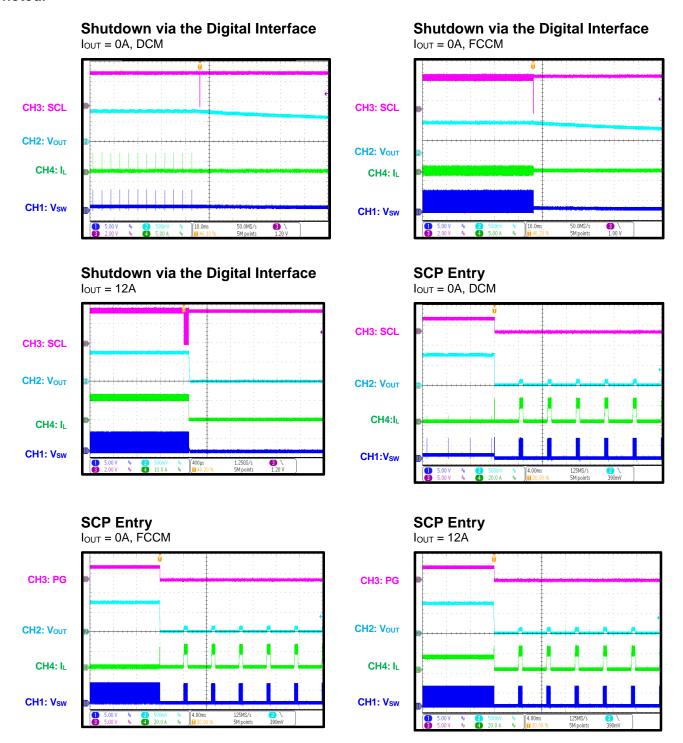

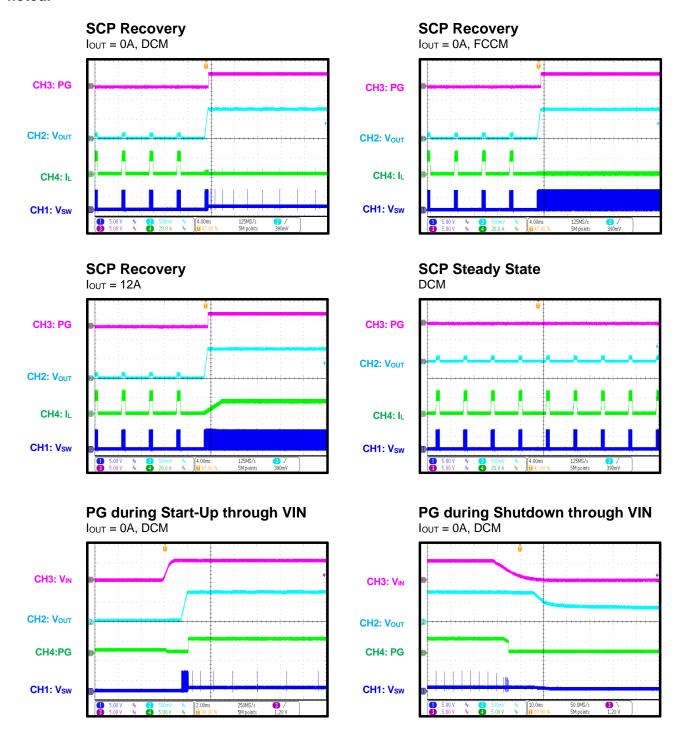

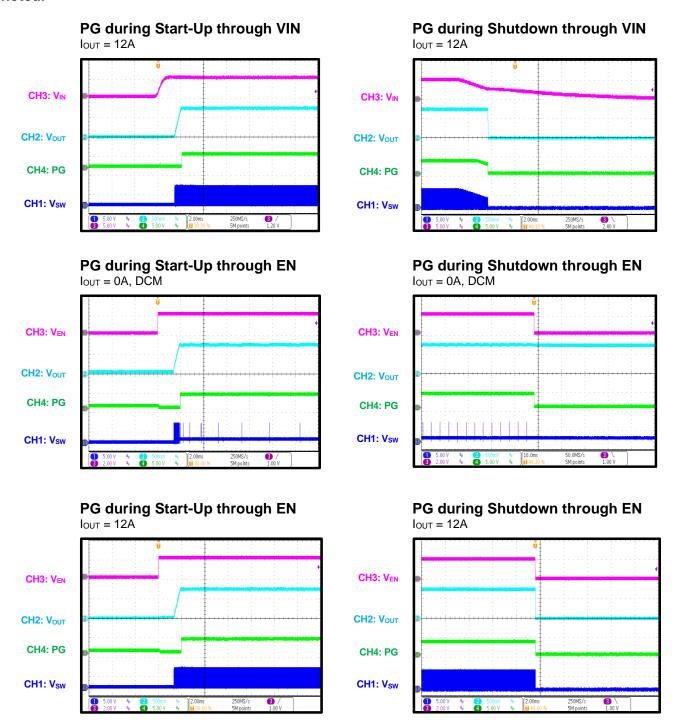

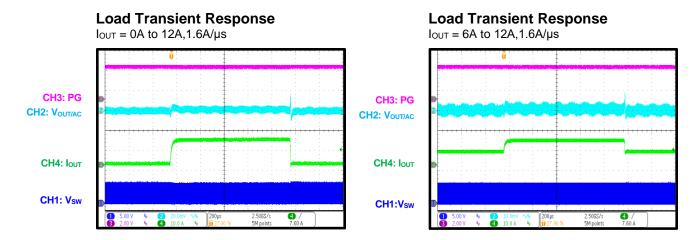

$V_{IN} = 5V$ ,  $V_{OUT} = 0.75V$ , L = 100nH,  $C_{OUT} = 4 \times 47 \mu F$ ,  $f_{SW} = 3 MHz$ , DCM,  $T_A = 25 ^{\circ} C$ , unless otherwise noted.

$V_{IN} = 5V$ ,  $V_{OUT} = 0.75V$ , L = 100nH,  $C_{OUT} = 4 \times 47 \mu F$ ,  $f_{SW} = 3MHz$ , DCM,  $T_A = 25$ °C, unless otherwise noted.

$V_{IN} = 5V$ ,  $V_{OUT} = 0.75V$ , L = 100nH,  $C_{OUT} = 4 \times 47 \mu F$ ,  $f_{SW} = 3 MHz$ , DCM,  $T_A = 25 ^{\circ} C$ , unless otherwise noted.

$V_{IN} = 5V$ ,  $V_{OUT} = 0.75V$ , L = 100nH,  $C_{OUT} = 4 \times 47 \mu F$ ,  $f_{SW} = 3 MHz$ , DCM,  $T_A = 25 ^{\circ} C$ , unless otherwise noted.

© 2023 MPS. All Rights Reserved.

LOAD CURRENT (mA)

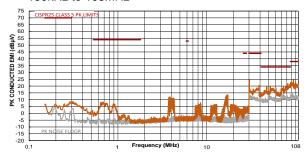

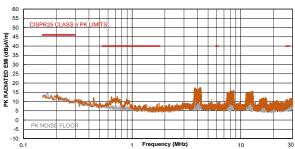

$V_{IN} = 6V$ ,  $V_{OUT} = 1.1V$ , L= 100nH,  $C_{OUT} = 4 \times 47 \mu F$ ,  $f_{SW} = 4MHz$ ,  $I_{OUT} = 12A$ ,  $T_A = 25$ °C, unless otherwise noted.

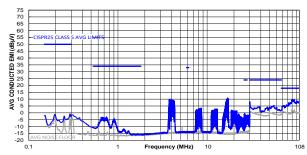

### CISPR25 Class 5 Peak Conducted **Emissions**

150kHz to 108MHz

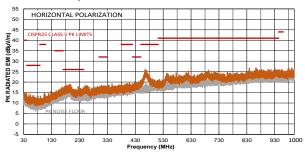

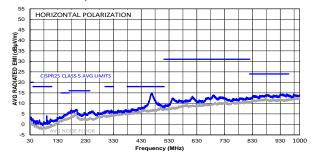

#### CISPR25 Class 5 Peak Radiated **Emissions**

150kHz to 30MHz

#### CISPR25 Class 5 Peak Radiated **Emissions**

Horizontal, 30MHz to 1GHz

#### CISPR25 Class 5 Peak Radiated **Emissions**

Vertical, 30MHz to 1GHz

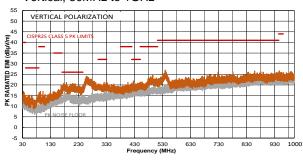

#### CISPR25 Class 5 Average Conducted **Emissions**

150kHz to 108MHz

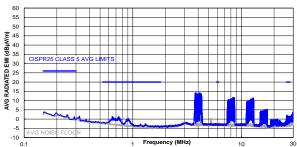

#### CISPR25 Class 5 Average Radiated **Emissions**

150kHz to 30MHz

#### CISPR25 Class 5 Average Radiated **Emissions**

Horizontal, 30MHz to 1GHz

#### **CISPR25 Class 5 Average Radiated Emissions**

Vertical, 30MHz to 1GHz

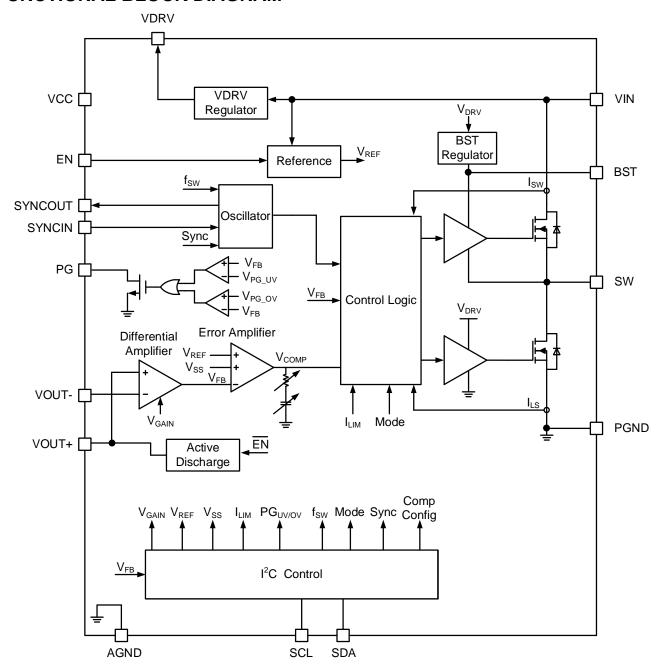

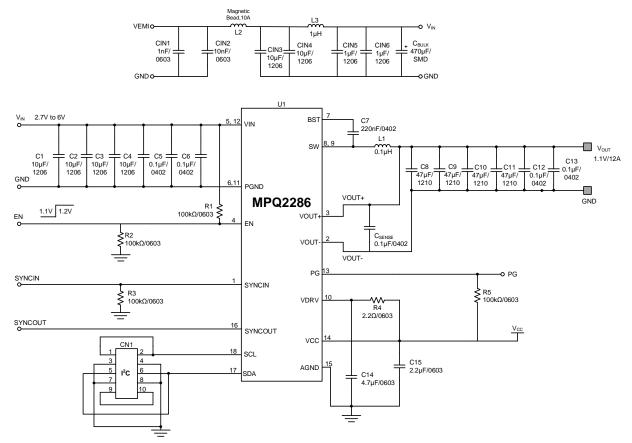

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 2: Functional Block Diagram

#### **OPERATION**

The MPQ2286 is a high-efficiency, high-frequency, synchronous buck regulator with integrated internal high-side and low side-power MOSFETs (HS-FET and LS-FET, respectively). The device provides 12A of highly efficient output current ( $I_{OUT}$ ) with fixed-frequency, zero-delay PWM (ZDP<sup>TM</sup>) control.

The device features a configurable 2MHz to 4MHz switching frequency (f<sub>SW</sub>), soft start, soft stop, and precision current limit. It also features a digital interface with packet error checking (PEC) and integrated multi-page one-time programmable (OTP) memory, which allows for a high degree of configurability.

# Zero-Delay PWM (ZDP™) Control

Automotive applications generally require fixed-frequency operation to reduce EMI concerns, but traditional fixed control topologies have major limitations. Voltage mode control is difficult to compensate in automotive environments, while peak current mode struggles to keep up with stringent modern system-on-chip (SoC) transient requirements with excessive output capacitance. With these requirements in mind, the MPQ2286 implements fixed-frequency, zero-delay PWM (ZDP<sup>TM</sup>) control.

ZDP™ control combines current information with hysteretic-style output voltage control in a clocked system. This provides a near optimal transient response while maintaining a high phase margin across a wide variety of operating conditions and external component values. In addition, it maintains superior EMI performance. The improved transient response decreases output capacitance requirements, which lowers system cost. Trailing edge modulation facilitates a narrow on time for high conversion ratio applications.

At the beginning of the pulse-width modulation (PWM) cycle, the HS-FET turns off and the LS-FET turns on immediately until the control signal reaches the COMP voltage. The HS-FET remains off for at least 80ns at the beginning of the cycle.

#### **Light-Load Operation**

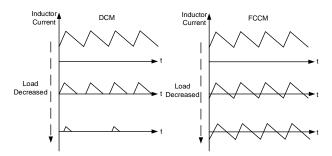

Under light-load conditions, the MPQ2286 can work in two different operation modes by setting the mode via the digital interface. The available

modes are forced continuous conduction mode (FCCM) and discontinuous conduction mode (DCM).

If configured for FCCM, the MPQ2286 works with a fixed frequency across the no-load to full-load range. The advantages of FCCM are the constant frequency and lower output voltage ripple at light loads.

With DCM is enabled, the MPQ2286 initiates non-synchronous operation when the inductor current reaches 0A. As the load is further reduced, the minimum peak inductor current is prevented from going below a fixed peak current value (see Figure 3). When this load condition is reached, f<sub>SW</sub> starts to drop.

Figure 3: DCM and FCCM

#### Internal Regulator VDRV and VCC

The internal 3.3V VDRV regulator powers the gate driver and BST supply. This regulator uses VIN as its input and operates across the full input voltage ( $V_{IN}$ ) range. When  $V_{IN}$  exceeds 3.3V, VDRV is in full regulation. When  $V_{IN}$  is below 3.3V, the VDRV output degrades. Connect a 4.7µF capacitor from VDRV to PGND, and placed as close to the VDRV pin as possible, to decouple the supply.

Connect the VDRV supply to the VCC pin with a  $2.2\Omega$  resistor and decouple the VCC pin with a  $2.2\mu F$  capacitor connected to AGND to provide the power supply to the rest of the MPQ2286.

#### **Dynamic Voltage Scaling**

The output voltage ( $V_{\text{OUT}}$ ) can be adjusted via the digital interface during normal operation. When the voltage changes, the slope is determined by the digital interface's VOUT\_SLEW register.

During the rising transition, the device maintains the previous mode. During the falling transition, the device automatically switches to FCCM.

### **Bootstrap Charging**

The bootstrap capacitor is charged and regulated to about 3.3V by the dedicated internal bootstrap regulator. When the voltage between the BST and SW nodes is below its regulation value, a transistor connected from VDRV to BST turns on to charge the bootstrap capacitor.

When the HS-FET is on, BST exceeds VDRV, so the bootstrap capacitor cannot be charged. Under higher duty cycle conditions, the time available for bootstrap charging is shorter, so the bootstrap capacitor may not be sufficiently charged. In this scenario, the bootstrap refresh circuit turns off the HS-FET and turns on the LS-FET to ensure that the bootstrap capacitor is correctly charged.

## **Enable (EN) Control**

EN is a digital control pin that turns the regulator on and off. Forcing the EN pin above the EN threshold turns on the device. The device turns off when the EN pin is driven below 1.1V.

#### SYNCIN

f<sub>SW</sub> can be synchronized to the rising edge of an external clock signal applied at SYNCIN. The high amplitude of the SYNC clock should exceed 1.8V and have a low amplitude below 0.4V to drive the internal logic. The recommended external SYNC frequency is set to ±15% for the range between 2MHz and 4MHz.

The MPQ2286 operates in FCCM with a fixed frequency when there is a SYNC clock, regardless of  $I_{\text{OUT}}$ . A pulse longer than 200ns is recommended. Connect SYNCIN to GND through a resistor if it is not used.

#### **SYNCOUT**

The MPQ2286 can output the internal clock with a 0° or 180° phase shift. With this function, two devices can operate at the same frequency but 180° out of phase to reduce the total input current ripple. This allows a lower-value input bypass capacitor to be used.

#### Soft Start

The soft-start function is implemented to prevent  $V_{\text{OUT}}$  from overshooting during start-up. When the MPQ2286 starts up, the internal circuitry generates a soft-start voltage that ramps up from 0V. The soft-start period lasts until the voltage on the soft-start capacitor exceeds the reference voltage ( $V_{\text{REF}}$ ). At this point, the error amplifier uses  $V_{\text{REF}}$  as the reference. There are four available soft-start slew rates, which can be configured via the OTP.

#### **Soft Stop**

Four shutdown slew rates are available to set the soft-stop time, which can be enabled via the OTP. The soft stop function is implemented to discharge  $V_{\text{OUT}}$ . When the MPQ2286 starts to turn off,  $V_{\text{REF}}$  ramps down and  $V_{\text{OUT}}$  follows. This causes charge to transfer from the output to the input. During the soft-stop period, the MPQ2286 operates in FCCM, even if the MPQ2866 is set to operate in DCM. The soft-stop slew rates can be configured via the OTP.

#### **Minimum On Time and Minimum Off Time**

When the device triggers the minimum on time (26ns), the MPQ2286's control loop automatically skips some pulses. The part does not decrease the frequency once the minimum off time (80ns) is triggered. This means that for applications with a low  $V_{\text{IN}}$  and a high  $V_{\text{OUT}}$ ,  $V_{\text{OUT}}$  drops once the device reaches the minimum off time.

## **Output Discharge**

An optional 120 $\Omega$  discharge MOSFET is available, which can be configured via the OTP. When enabled, the discharge MOSFET turns on after the part is disabled. This MOSFET continues to operate as long as  $V_{IN} > 2.4V$ .

## Pre-Biased Start-Up

If  $V_{OUT}$  exceeds 0V at start-up, both the HS-FET and LS-FET remain off until the soft-start ramp reaches  $V_{OUT}$ .

#### Power Good (PG) Indicator

The power good (PG) indicator is an open-drain output that indicates whether  $V_{\text{OUT}}$  is within the power good thresholds. The pin asserts (pulls low) if the power is outside of the PG thresholds, the output is off, or if soft start/shutdown occurs. PG can also be configured to indicate thermal

warning or digital interface communication failures via the OTP.

### **Over-Current Protection (OCP)**

The MPQ2286 implements cycle-by-cycle overcurrent protection (OCP) to limit I<sub>OUT</sub>. The peak and valley current limits ensure protection regardless of the duty cycle.

When the inductor current ( $I_L$ ) reaches the highside peak current limit while the HS-FET is on, the HS-FET is forced off immediately to prevent the current from rising further. If the clock is received before  $I_L$  reaches current limit, the HS-FET also turns off due to the clock.

When the LS-FET is on, the next clock's rising edge is held until  $I_{L}$  drops below the low-side valley current limit. Then  $I_{L}$  can drop to a sufficiently low value when the HS-FET turns on again. This current limit scheme prevents current runaway if an overload or short-circuit event occurs.

# Short-Circuit Protection (SCP) and Under-Voltage Protection (UVP)

If V<sub>OUT</sub> is below 75% of the configured output voltage, short-circuit protection and output under-voltage protection (UVP) is triggered. The output shuts off for the hiccup time, and restarts with a full soft-start period. It is possible to enable or disable output under-voltage protection via the OTP. If enabled, the output discharge function operates during the hiccup time.

#### **Output Over-Voltage Protection (OVP)**

If an output exceeds the output over-voltage protection (OVP) threshold, that output shuts off for the hiccup time, and then the normal soft-start process begins again. Enable or disable output OVP via the OTP. If enabled, the output discharge function operates during the hiccup time.

# Input Over-Voltage Protection (OVP)

If  $V_{\text{IN}}$  exceeds 6.7V, input OVP is triggered. The MPQ2286 starts operating once the  $V_{\text{IN}}$  drops below the input OVP threshold (OVP rising threshold - OVP hysteresis).

#### Thermal Warning (TW)

If the die temperature exceeds the thermal warning threshold, the thermal warning register asserts. The power good function can be configured to indicate whether thermal warning has occurred via the PG MAPPING register.

# Thermal Shutdown (TSD)

If the die temperature exceeds the thermal shutdown threshold, the MPQ2286 disables switching and the PG pin asserts.

# Multi-Page One-Time Programmable (OTP) Memory

The MPQ2286 features two user pages of OTP memory to store settings permanently.

For long-term reliability, a differential OTP cell is used instead of a single-ended cell. Data is stored on two floating gate avalanche injection metal oxide semiconductors (FAMOS), and output comparators are used for differential reading.

Only the code MPQ2286-0000 has OTP memory that can be written to twice; all other codes have OTP memory that can be written to once, or not at all. The OTP memory can be written to via the dedicated STORE\_USER\_ALL (15h) command.

#### Cyclic Redundancy Check (CRC)

The OTP memory is protected by a cyclic redundancy check (CRC). If the calculated CRC value does not match the recorded value during the power on process, the device does not start up.

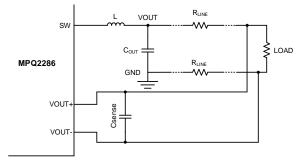

#### **Remote Output Voltage Sensing**

The remote output voltage sensing function is implemented to compensate for the voltage drop in the copper between the MPQ2286 and the load caused by the large output current and the resistance in the transmission line. Figure 4 shows the remote output voltage sensing circuit, connect the VOUT+ and VOUT- pins close to the load with a Kelvin connection to accurately sense the output voltage.

Figure 4: Remote Output Voltage Sensing Circuit

# **DIGITAL INTERFACE**

# **Digital Serial Interface Description**

The digital interface is an open-standard, power-management protocol that defines a means of communication with power conversion and other devices. The digital interface is a two-wire, bidirectional serial interface, consisting of a serial data line (SDA) and a serial clock line (SCL). The lines are externally pulled to a bus voltage when they are idle. Connecting to the line, a master device generates the SCL signal and device address, and arranges the communication sequence.

The MPQ2286 works as a slave-only device, which supports fast-mode plus (1Mbps) bidirectional data transfer, adding flexibility to the power supply solution. The output voltage, transition slew rate, and other converter parameters can be instantaneously controlled via the digital interface.

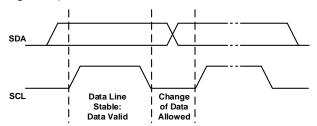

# **Data Validity**

One clock pulse is generated for each data bit transferred. The data on the SDA line must be stable during the high period of the clock. The high or low state of the SDA line can only change when the clock signal on the SCL line is low (see Figure 5).

Figure 5: Bit Transfer on the Digital Interface

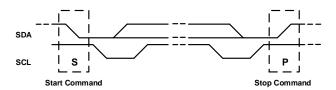

# **Start and Stop Commands**

The start and stop commands are signaled by the master device, which signifies the beginning and the end of the digital interface transfer. The start (S) command is defined as the SDA signal transitioning from high to low while the SCL line is high. The stop (P) command is defined as the SDA signal transitioning from low to high while the SCL is high (see Figure 6).

Figure 6: Start and Stop Command

Start and stop commands are always generated by the master. The bus is considered busy after the start command. The bus is considered free again after a certain time after the stop command. The bus stays busy if a repeated start (Sr) command is generated instead of a stop command. The start and repeated start commands are functionally identical.

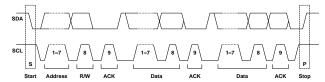

#### **Transfer Data**

Every byte put on the SDA line must be 8 bits long. Each byte must be followed by an acknowledge (ACK) bit. The acknowledge-related clock pulse is generated by the master. The transmitter releases the SDA line (high) during the acknowledge clock pulse. The receiver must pull down the SDA line during the acknowledge clock pulse, so that it remains stable low during the high period of the clock pulse.

Figure 7 shows the data transfer format. After the start command, a slave address is sent. This address is 7 bits long followed by an 8th data direction bit (R/W). A 0 indicates a transmission (write), and a 1 indicates a request for data (read). Data transfer is always terminated by a stop command, which is generated by the master. However, if a master still wishes to communicate on the bus, it can generate a repeated start command and address another slave without first generating a stop command.

Figure 7: A Complete Data Transfer

## Packet Error Checking (PEC)

The PEC mechanism is employed to improve communication reliability and robustness. Whenever applicable, PEC is implemented by appending a packet error code after the data of each message transfer.

The packet error code is a CRC-8 error-checking byte, calculated on all the message bytes, including addresses and read/write (R/W) bits. The code is appended to the message by the device that supplied the last data byte.

If an incorrect code is received, a communications fault is triggered. The power good flag asserts until the fault register is cleared.

#### **Digital Interface Communication Failure**

A data transmission fault occurs when the data is not properly transferred between the devices. There are several data transmission faults, listed below:

- Sending too little data

- Reading too little data

- The host sends too many bytes

- The host reads too many bytes

- Improperly set read bit in the address byte

- Unsupported command code

The communication failure is recorded in the STATUS\_CML register.

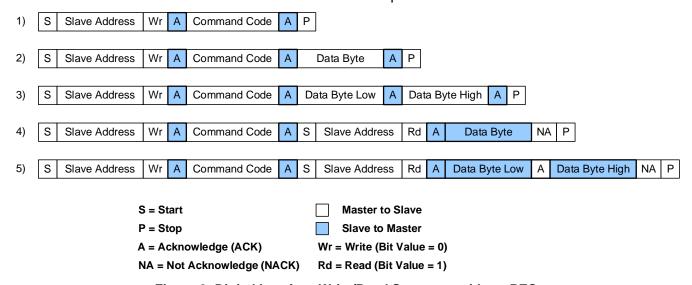

#### Write/Read Sequence

All digital interface commands are supported by the MPQ2286. There are five kinds of commands that can be implemented with or without PEC:

- 1) Send command only

- 2) Write byte

- 3) Write word

- 4) Read byte

- 5) Read word

If the master writes a command to a read-only register, the MPQ2286 performs the same action as it would if the host sent too many bytes. If the master sends a read command from a write-only register, the MPQ2286 performs the same action as it would if the host read too many bytes.

Figure 8 shows the write/read sequence without PEC. Figure 9 on page 42 shows the write/read sequence with PEC.

Figure 8: Digital Interface Write/Read Sequence without PEC

# MPQ2286 – 6V, 12A, SYNC BUCK REGULATOR WITH DIGITAL INTERFACE, AEC-Q100

| 1) | s                           | Slave Address | Wr   | Α   | Command Code | Α                         |                 | PEC Byte                   | Α  | Р    |      |            |     |     |        |          |    |   |

|----|-----------------------------|---------------|------|-----|--------------|---------------------------|-----------------|----------------------------|----|------|------|------------|-----|-----|--------|----------|----|---|

| ,  |                             |               | 1    |     |              |                           |                 | ,                          |    |      |      |            |     |     |        |          |    |   |

| 2) | S                           | Slave Address | Wr   | Α   | Command Code | Α                         |                 | Data Byte                  | Α  | F    | EC   | Byte A     | Р   |     |        |          |    |   |

|    |                             |               |      |     |              |                           |                 |                            |    |      |      |            |     |     |        |          |    |   |

| 3) | S                           | Slave Address | Wr   | Α   | Command Code | Α                         | Da              | ata Byte Low               | Α  | Data | а Ву | rte High A |     | PEC | Byte   | A P      |    |   |

|    |                             |               |      |     |              |                           |                 |                            |    |      |      |            |     |     |        |          |    |   |

| 4) | S                           | Slave Address | Wr   | Α   | Command Code | Α                         | S               | Slave Addre                | ss | Rd   | Α    | Data By    | te  | Α   | PEC    | Byte     | NA | Р |

|    |                             |               |      |     |              |                           |                 |                            |    |      |      |            |     |     |        |          |    |   |

| 5) | S                           | Slave Address | Wr   | Α   | Command Code | Α                         | S               | Slave Addre                | ss | Rd   | Α    | Data Byte  | Low | Α   | Data B | yte High | Α  |   |

|    |                             |               |      |     |              |                           |                 |                            |    |      |      |            |     |     | PEC    | Byte     | NA | Р |

|    | S = Start                   |               |      |     |              |                           | Master to Slave |                            |    |      |      |            |     |     |        |          |    |   |

|    | P = Stop                    |               |      |     |              | Slave to Master           |                 |                            |    |      |      |            |     |     |        |          |    |   |

|    |                             | Α             | = Ac | kno | wledge (ACK) |                           | ,               | Wr = Write (Bit Value = 0) |    |      |      |            |     |     |        |          |    |   |

|    | NA = Not Acknowledge (NACK) |               |      |     |              | Rd = Read (Bit Value = 1) |                 |                            |    |      |      |            |     |     |        |          |    |   |

Figure 9: Digital Interface Write/Read Sequence with PEC

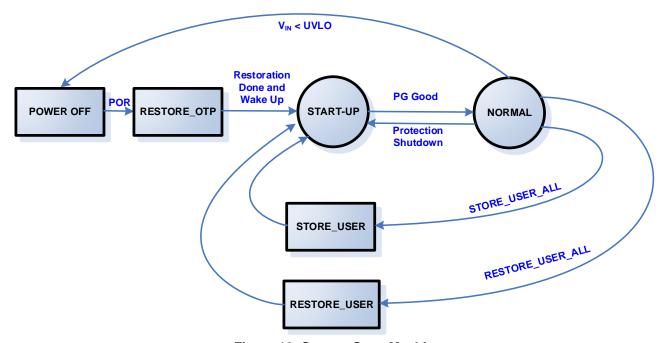

# STATE MACHINE DESCRIPTION

The state machine describes the different states of operation. There are six states in the device: POWER OFF, RESTORE\_OTP, START-UP,

NORMAL, STORE\_USER, and RESTORE\_USER (see Figure 10).

Each state is described in greater detail below.

Figure 10: System State Machine

#### **Power Off State (POWER OFF)**

The MPQ2286 is in the power off state as long the power on reset (POR) is not released.

# Restore the OTP State (RESTORE\_OTP)

When  $V_{\text{IN}}$  exceeds its rising UVLO threshold, POR is released. The MPQ2286 restores the registers from the embedded OTP content data. Once restoration is complete, the MPQ2286 automatically enters the start-up state.

#### Start-Up State (START-UP)

Once restoring the OTP is complete and the wake-up signal is enabled, the device enters the start-up state. All the other supplies are enabled and the output starts to ramp up in the start-up state.

## **Normal State (NORMAL)**

The MPQ2286 enters the normal state as soon as the output regulator voltage is power good. The normal state is the standard operating state for the MPQ2286, during which the output regulator is up and running.

# Store User State (STORE\_USER)

The store user state writes the present data from the registers to the internal OTP content. Then the MPQ2286 transitions to the start-up state and restarts. Only writing to the STORE\_USER\_ALL register from the normal state can force the device to enter the store user state. See the STORE\_USER\_ALL (15h) section on page 46 for more details.

#### Restore User State (RESTORE\_USER)

The restore user state copies the entire contents of the OTP values to the matching locations in the registers. The values in the registers are overwritten by the value retrieved from the OTP. Any items in the OTP that do not have matching locations in the operating memory are ignored. Then the MPQ2286 transitions to the start-up state and restarts. Only writing RESTORE USER ALL register from the normal state can force the device to enter the restore user state. See the RESTORE USER ALL (16h) section on page 46 for more details.

# **REGISTER MAP**

| Command Code        | Command Name        | Type | Bytes | OTP | Page 0 |

|---------------------|---------------------|------|-------|-----|--------|

| 01h                 |                     |      | 1     | Yes | ✓      |

| 03h                 | CLEAR_FAULTS        | W    | 0     | No  | ✓      |

| 10h                 | WRITE_PROTECT       | R/W  | 1     | No  | ✓      |

| 15h                 | STORE_USER_ALL      | W    | 0     | No  | ✓      |

| 16h                 | RESTORE_USER_ALL    | W    | 0     | No  | ✓      |

| 19h                 | CAPABILITY          | R    | 1     | No  | ✓      |

| 20h                 | VOUT_MODE           | R    | 1     | No  | ✓      |

| 21h                 | VOUT_COMMAND        | R/W  | 1     | Yes | ✓      |

| 24h                 | VOUT_MAX            | R/W  | 1     | Yes | ✓      |

| 29h <sup>(11)</sup> | VOUT_SCALE          | R/W  | 1     | Yes | ✓      |

| 2Bh                 | VOUT_MIN            | R/W  | 1     | Yes | ✓      |

| 60h                 | TON_DELAY           | R/W  | 1     | Yes | ✓      |

| 64h                 | TOFF_DELAY          | R/W  | 1     | Yes | ✓      |

| 78h                 | STATUS_BYTE         | R/W  | 1     | No  | ✓      |

| 79h                 | STATUS_WORD         | R/W  | 2     | No  | ✓      |

| 7Ah                 | STATUS_VOUT         | R/W  | 1     | No  | ✓      |

| 7Bh                 | STATUS_IOUT         | R/W  | 1     | No  | ✓      |

| 7Ch                 | STATUS_INPUT        | R/W  | 1     | No  | ✓      |

| 7Dh                 | STATUS_TEMPERATURE  | R/W  | 1     | No  | ✓      |

| 7Eh                 | STATUS_CML          | R/W  | 1     | No  | ✓      |

| 9Bh                 | MFR_REVISION        | R    | 1     | No  | ✓      |

| C4h                 | SECURE_LOCKOUT      | R/W  | 1     | No  | ✓      |

| C5h                 | HICCUP_TIMER        | R/W  | 1     | Yes | ✓      |

| C6h                 | VOUT_STARTUP_SLEW   | R/W  | 1     | Yes | ✓      |

| C7h                 | VOUT_SHUTDOWN_SLEW  | R/W  | 1     | Yes | ✓      |

| C8h                 | VOUT SLEW           | R/W  | 1     | Yes | ✓      |

| C9h                 | OUTPUT DISCHARGE    | R/W  | 1     | Yes | ✓      |

| CAh                 | FREQUENCY_DITHER    | R/W  | 1     | Yes | ✓      |

| CBh                 | FREQUENCY_SET       | R/W  | 1     | Yes | ✓      |

| CCh                 | COMPENSATION CONFIG | R/W  | 2     | Yes | ✓      |

| CEh                 | PROTECTION CONFIG   | R/W  | 1     | Yes | ✓      |

| CDh                 | PG MAPPING          | R/W  | 1     | Yes | ✓      |

| CFh                 | PG_DELAY            | R/W  | 1     | Yes | ✓      |

| D0h                 | PG CONFIG           | R/W  | 1     | Yes | ✓      |

| D1h                 | LIGHT_LOAD          | R/W  | 1     | Yes | ✓      |

| D2h                 | ILIM_SCALE          | R/W  | 1     | Yes | ✓      |

| D3h                 | ADDRESS             | R/W  | 1     | Yes | ✓      |

| D4h                 | CONFIGURATION CODE  | R    | 1     | Yes | ✓      |

| D5h                 | MEMORY_CRC          | R    | 2     | Yes | ✓      |

| D6h                 | LATEST_PEC          | R    | 1     | No  | ✓      |

| D8h                 | MFR_OTP_MEM_STATUS  | R    | 1     | No  | ✓      |

# **REGISTER MAP** (continued)

| <b>Command Code</b> | Command Name         | Type | Bytes | OTP | Page 0 |

|---------------------|----------------------|------|-------|-----|--------|

| DBh                 | ADVANCED_CONFIG      | W    | 1     | No  | ✓      |

| DCh                 | SUMMING_BLOCK_CONFIG | R/W  | 1     | Yes | ✓      |

| DDh                 | MIN_ON_CONFIG        | R/W  | 1     | Yes | ✓      |

#### Note:

<sup>11)</sup> This register value cannot be modified while the device is operating. Disable the output before modifying this register.

# **REGISTER MAP (PAGE 0)**

# **OPERATION (01h)**

Format: Unsigned binary

The OPERATION command on Page 0 configures the converter output's on/off state, in conjunction with input from the EN pin.

| Bits | Access | Bit Name  | Default | Description                                           |

|------|--------|-----------|---------|-------------------------------------------------------|

| 7    | R/W    | OPERATION | 1'b1    | 1'b1: Output on (if enabled high)<br>1'b0: Output off |

| 6:0  | R      | RESERVED  | N/A     | Unused. Writes are ignored and always read as 0.      |

#### CLEAR\_FAULTS (03h)

The CLEAR\_FAULTS command on Page 0 clears any fault bit in all status registers: STATUS\_BYTE (78h), STATUS\_WORD (79h), STATUS\_VOUT (7Ah), STATUS\_INPUT (7Ch), STATUS\_TEMPERATURE (7Dh), and STATUS\_CML (7Eh).

This command is write-only. There is no data byte for this command.

#### WRITE\_PROTECT (10h)

Format: Unsigned binary

The WRITE\_PROTECT command on Page 0 controls writing to the converter. The intent of this command is to provide protection against accident changes. It is not intended to provide protection against deliberate changes to the converter's configuration or operation. All the supported commands may have their parameters read, regardless of the WRITE\_PROTECT settings.

| Bits | Access | Bit Name      | Default   | Description                                                                                                                                                                                                                                                                                                                               |

|------|--------|---------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0  | R/W    | WRITE_PROTECT | 8'b000000 | 8'b10000000: Disable all writes except to the WRITE_PROTECT command 8'b01000000: Disable all writes except to the WRITE_PROTECT, OPERATION, and PAGE commands 8'b00100000: Disable all writes except to the WRITE_PROTECT, OPERATION, PAGE, and VOUT_COMMAND commands 8'b00000000: Enable writes to all commands Others: Invalid commands |

#### STORE\_USER\_ALL (15h)

The STORE\_USER\_ALL command on Page 0 instructs the MPQ2286 to copy the contents of the operating memory to the matching locations in the OTP, except for the internal trim registers. This process begins when the MPQ2286 receives a STORE USER ALL command from the digital interface.

This command is write-only. There is no data byte for this command.

#### RESTORE\_USER\_ALL (16h)

The RESTORE\_USER\_ALL command on Page 0 instructs the MPQ2286 to copy the contents from the OTP and overwrite the matching locations in the operating memory, except for the trim registers. Any items in the OTP that do not have matching locations in the operating memory are ignored.

The RESTORE\_USER\_ALL command can be used while the MPQ2286 is operating. However, the MPQ2286 may be unresponsive during this operation with unpredictable, undesirable, or even catastrophic results.

This command is write-only. There is no data byte for this command.

# **CAPABILITY (19h)**

Format: Unsigned binary

The CAPABILITY command on Page 0 provides 1 byte to return key digital interface features that the MPQ2286 can support.

| Bits | Access | Bit Name                | Default | Description                                                                                                                    |

|------|--------|-------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------|

| 7    | R      | PACKET_ERR_<br>CHECKING | 1'b1    | 1'b1: Packet error checking (PEC) is supported Others: Invalid commands                                                        |

| 6:5  | R      | MAX_BUS_SPEED           | 2'b10   | 2'b10: The maximum supported bus speed is 1MHz<br>Others: Invalid commands                                                     |

| 4    | R      | SMBALERT#               | 1'b0    | 1'b0: The device does not have a SMBALERT# pin and does not support the SMBus Alert Response protocol Others: Invalid commands |

| 3    | R      | NUMERIC_FORMAT          | 1'b0    | 1'b0: Numeric data is in Linear11, ULinear16, Slinear16, or direct format Others: Invalid commands                             |

| 2    | R      | AVSBUS_SUPPORT          | 1'b0    | 1'b0: AVSBus is not supported<br>Others: Invalid commands                                                                      |

| 1:0  | R      | RESERVED                | N/A     | Reserved.                                                                                                                      |

# VOUT\_MODE (20h)

Format: Unsigned binary

The VOUT\_MODE command on Page 0 commands and reads the output voltage mode. The 3MSB determine the data format (only direct format is supported by the MPQ2286).

| Bits | Access | Bit Name  | Default         | Description                                                                                         |

|------|--------|-----------|-----------------|-----------------------------------------------------------------------------------------------------|

| 7:0  | R      | VOUT_MODE | 8'b010000<br>00 | 8'b01000000: Direct mode. The coefficients are m = 160, R = 0, and b = -33 Others: Invalid commands |

# **VOUT\_COMMAND (21h)**

Format: Unsigned binary

The VOUT\_COMMAND command on Page 0 sets Vout.

| Bits | Access | Bit Name | Default   | Description                                                                                                                    |

|------|--------|----------|-----------|--------------------------------------------------------------------------------------------------------------------------------|

|      |        |          |           | V <sub>OUT</sub> can be calculated with the following equation:                                                                |

| 7:0  | R/W    | VOUT CMD | 8'b011111 | V <sub>OUT</sub> = (VOUT_CMD x 6.25mV + 206.25mV) x VOUT_SL                                                                    |

|      |        |          | 11        | If VOUT_SL = 1, $V_{OUT}$ can be set between 0.20625V and 1.8V. If VOUT_SL = 2, $V_{OUT}$ can be set between 0.4125V and 3.6V. |

# VOUT\_MAX (24h)

Format: Unsigned binary

The VOUT\_MAX command on Page 0 sets an upper limit on the  $V_{OUT}$  that the converter can command, regardless of any other commands or combinations. The intent of this command is to provide a safeguard against a user accidentally setting  $V_{OUT}$  to a possibly destructive level, rather than to be the primary output over-voltage protection (OVP).

| Bits | Access | Bit Name | Default         | Description                                                                                                                       |

|------|--------|----------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------|

|      |        |          |                 | Sets the maximum $V_{\text{OUT}}$ , which can be calculated with the following equation:                                          |

|      |        |          |                 | V <sub>OUTMAX</sub> = (VOUT_MAX x 6.25mV + 206.25mV) x VOUT_SL                                                                    |

| 7:0  | R/W    | VOUT_MAX | 8'b111111<br>11 | If VOUT_SL = 1, Vout can be set between 0.20625V and 1.8V. If VOUT_SL = 2, Vout can be set between 0.4125V and 3.6V.              |

|      |        |          |                 | Attempting to write a higher value to VOUT_COMMAND causes VOUT_COMMAND to be set to VOUT_MAX, and asserts a VOUT_MAX_MIN warning. |

## VOUT\_SCALE\_LOOP (29h)

Format: Unsigned binary

The VOUT\_SCALE\_LOOP command on Page 0 sets the VouT scale.

| Bits | Access | Bit Name  | Default | Description                                                                                                           |

|------|--------|-----------|---------|-----------------------------------------------------------------------------------------------------------------------|

| 7:1  | R/W    | RESERVED  | N/A     | Reserved.                                                                                                             |

| 0    | R/W    | VOUT_SC_L | 1'b0    | Sets the Vout scale. Direct mode. The coefficients are m = 1, R = 0, and b = -1.  1'b0: VOUT_SL = 1 1'b1: VOUT_SL = 2 |

#### VOUT\_MIN (2Bh)

Format: Unsigned binary

The VOUT\_MIN command on Page 0 sets a lower limit on the  $V_{\text{OUT}}$  that the converter can command, regardless of any other commands or combinations. The intent of this command is to provide a safeguard against a user accidentally setting  $V_{\text{OUT}}$  to a possibly destructive level, rather than to be the primary output under-voltage protection (UVP).

| Bits | Access | Bit Name                                                       | Default         | Description                                                                                                                       |

|------|--------|----------------------------------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------|

|      |        |                                                                |                 | Sets the minimum $V_{\text{OUT}}$ , which can be calculated with the following equation:                                          |

|      |        | V <sub>OUTMIN</sub> = (VOUT_MIN x 6.25mV + 206.25mV) x VOUT_SL |                 |                                                                                                                                   |

| 7:0  | R/W    | VOUT_MIN                                                       | 00<br>8'b000000 | If VOUT_SL = 1, $V_{OUT}$ can be set between 0.20625V and 1.8V. If $VOUT_SL = 2$ , $V_{OUT}$ can be set between 0.4125V and 3.6V. |

|      |        |                                                                |                 | Attempting to write a lower value to VOUT_COMMAND causes VOUT_COMMAND to be set to VOUT_MIN, and asserts a VOUT_MAX_MIN warning.  |

### TON\_DELAY (60h)

Format: Unsigned binary

The TON\_DELAY command on Page 0 sets the start-up delay time.

| Bits | Access | Bit Name | Default | Description |

|------|--------|----------|---------|-------------|

| 7:5  | R/W    | RESERVED | N/A     | Reserved.   |

|     |     |           |          | Sets the start-up delay time, calculated with the following equation: |

|-----|-----|-----------|----------|-----------------------------------------------------------------------|

| 4:0 | R/W | TON_DELAY | 5'b00000 | Start-Up Delay = TON_DELAY x 0.25ms                                   |

|     |     |           |          | The delay can range between 0ms and 7.75ms.                           |

# TOFF\_DELAY (64h)

Format: Unsigned binary

The TOFF\_DELAY command on Page 0 sets the shutdown delay time.

| Bits | Access                      | Bit Name                                                              | Default | Description                                 |

|------|-----------------------------|-----------------------------------------------------------------------|---------|---------------------------------------------|

| 7:5  | R/W                         | RESERVED                                                              | N/A     | Reserved.                                   |

|      | 4:0 R/W TOFF_DELAY 5'b00000 | Sets the shutdown delay time, calculated with the following equation: |         |                                             |

| 4:0  |                             | Shutdown Delay = TOFF_DELAY x 0.25ms                                  |         |                                             |

|      |                             |                                                                       |         | The delay can range between 0ms and 7.75ms. |

## STATUS\_BYTE (78h)

Format: Unsigned binary

The STATUS\_BYTE command on Page 0 returns the value of a number of flags indicating the state of the MPQ2286. Send a CLEAR\_FAULTS (03h) command to clear the fault flag bits after the fault is removed. See the CLEAR\_FAULTS (03h) section on page 46 for more details.

| Bits | Access | Bit Name      | Default | Description                                                                                                              |

|------|--------|---------------|---------|--------------------------------------------------------------------------------------------------------------------------|

| 7    | R/W    | BUSY          | 1'b0    | 1'b0: No busy fault 1'b1: A fault was declared because the device was busy and unable to respond                         |

| 6    | R/W    | OFF           | 1'b0    | 1'b0: The device is on 1'b1: The device is off                                                                           |

| 5    | R/W    | VOUT_OV_FAULT | 1'b0    | 1'b0: No output over-voltage (OV) fault has occurred 1'b1: An output OV fault has occurred                               |

| 4    | R/W    | IOUT_OC_FAULT | 1'b0    | 1'b0: No output over-current (OC) fault has occurred 1'b1: An output OC fault has occurred                               |

| 3    | R/W    | RESERVED      | N/A     | Reserved.                                                                                                                |

| 2    | R/W    | TEMPERATURE   | 1'b0    | 1'b0: No temperature fault or warning has occurred 1'b1: A temperature fault or warning has occurred                     |

| 1    | R/W    | CML           | 1'b0    | 1'b0: No communications, memory, or logic fault has occurred 1'b1: A communications, memory, or logic fault has occurred |

| 0    | R/W    | FAULT_OTHER   | 1'b0    | 1'b0: No other fault has occurred 1'b1: A fault not covered by bits[7:1] of this command has occurred                    |

# STATUS\_WORD (79h)

Format: Unsigned binary

The STATUS\_WORD command on Page 0 returns 2 bytes of information with a summary of the device's fault/warning conditions. The higher byte gives more detailed information of the fault conditions. The lower byte is shared with register STATUS\_BYTE (78h). Send a CLEAR\_FAULTS (03h) command to clear the fault flag bits after the fault is removed. See the CLEAR\_FAULTS (03h) section on page 46 for more details.

| Bits        | Access | Bit Name      | Default         | Description                                                                                        |

|-------------|--------|---------------|-----------------|----------------------------------------------------------------------------------------------------|

| 15          | R/W    | VOUT_FAULT    | 1'b0            | 1'b0: No output voltage fault has occurred 1'b1: An output voltage fault has occurred              |

| 14          | R/W    | IOUT_FAULT    | 1'b0            | 1'b0: No output current fault has occurred 1'b1: An output current fault has occurred              |

| 13          | R/W    | VINFAULT      | 1'b0            | 1'b0: No input voltage fault has occurred 1'b1: An input voltage fault has occurred                |

| 12          | R/W    | MANUFAC_FAULT | 1'b0            | 1'b0: No manufacturer specific fault has occurred 1'b1: A manufacturer specific fault has occurred |

| 11          | R/W    | PGOOD         | 1'b0            | 1'b0: Power good is high<br>1'b1: Power good is low                                                |

| 10:8        | R/W    | RESERVED      | N/A             | Reserved.                                                                                          |

| Low<br>Byte | R/W    | STATUS_BYTE   | 8'b000000<br>00 | The same as STATUS BYTE (78h).                                                                     |

# STATUS\_VOUT (7Ah)

Format: Unsigned binary

The STATUS\_VOUT command on Page 0 returns detailed fault information. Clear the fault flag bit by writing 1 to the fault bit after this fault has been removed.

| Bits | Access | Bit Name              | Default | Description                                                                                                                                 |

|------|--------|-----------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | R/W    | VOUT_OV_FAULT         | 1'b0    | 1'b0: No output over-voltage (OV) fault has occurred 1'b1: An output OV fault has occurred                                                  |

| 6:5  | R/W    | RESERVED              | N/A     | Reserved.                                                                                                                                   |

| 4    | R/W    | VOUT_UV_FAULT         | 1'b0    | 1'b0: No output under-voltage (UV) fault has occurred 1'b1: An output UV fault has occurred                                                 |

| 3    | R/W    | VOUT_MAX_MIN_<br>WARN | 1'b0    | 1'b0: No attempt to set VouT beyond VOUT_MIN or VOUT_MAX has occurred 1'b1: An attempt to set VouT beyond VOUT_MIN or VOUT_MAX has occurred |

| 2:0  | R/W    | RESERVED              | N/A     | Reserved.                                                                                                                                   |

# STATUS\_IOUT (7Bh)

Format: Unsigned binary

The STATUS\_IOUT command on Page 0 returns detailed fault information. Clear the fault flag bit by writing 1 to the fault bit after this fault has been removed.

| Bits | Access | Bit Name      | Default | Description                                                                                |

|------|--------|---------------|---------|--------------------------------------------------------------------------------------------|

| 7    | R/W    | IOUT_OC_FAULT | 1'b0    | 1'b0: No output over-current (OC) fault has occurred 1'b1: An output OC fault has occurred |

| 6:0  | R/W    | RESERVED      | N/A     | Reserved1.                                                                                 |

# STATUS\_INPUT (7Ch)