# **MPQ4371**

36V, 6A to 11A, Low-EMI, Synchronous Step-Down Converter with ZDP™, AEC-Q100 Qualified

#### DESCRIPTION

The MPQ4371 family of buck converters are configurable-frequency (200kHz to 2.5MHz), synchronous, step-down switching regulators with integrated low on-resistance HS-FETs and LS-FETs. The family covers a 6A to 11A output current ( $I_{OUT}$ ) range and employs zero-delay PWM (ZDP<sup>TM</sup>) control, an MPS-exclusive technology that delivers fast transient response while reducing external capacitor count.

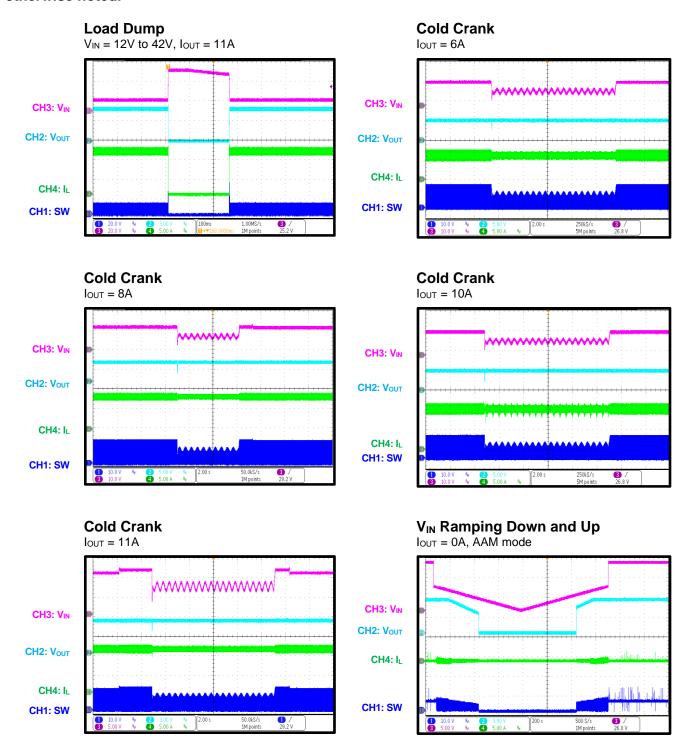

The wide 3.3V to 36V input voltage ( $V_{\text{IN}}$ ) range accommodates a variety of step-down applications in automotive input environment. A 1.8µA shutdown mode quiescent current allows use in battery-powered applications. High power conversion efficiency across the wide load range is achieved by scaling down the switching frequency ( $f_{\text{SW}}$ ) under light loads to reduce the switching and gate driving losses.

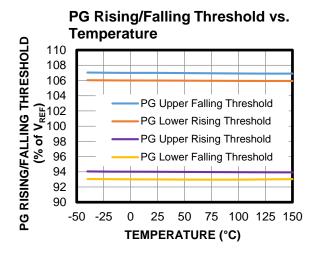

An open-drain power good signal indicates when the output is within 94% to 106% of its nominal voltage. Frequency foldback prevents inductor current runaway during start-up. Thermal shutdown provides reliable, fault-tolerant operation. A high duty cycle and low-dropout mode support automotive cold-crank conditions.

The MPQ4371 is available in QFN-23 (4mmx5mm) or TQFN-23 (4mmx5mm) packages with wettable flanks. It is available in AEC-Q100 Grade 1.

#### **FEATURES**

- Designed for Automotive Transients

- 3.3V to 36V Input Voltage (V<sub>IN</sub>) Range

- o Load Dump Up to 42V

- o Low-Dropout (LDO) Mode

- Available in AEC-Q100 Grade 1

- Highly Scalable Family

- 6A to 11A Output Current (I<sub>OUT</sub>)

Versions in Pin-Compatible Family

- Multi-Phase Capabilities Up to 8 Phases

- Designed for High-Performance and Reduced Component Overhead

- ZDP™ Control for Fast Transient Response and Fewer Capacitors

### FEATURES (continued)

- ±1% Output Accuracy

- Fixed or Adjustable V<sub>OUT</sub> Options

- Fixed Output <sup>(1)</sup>: 1V, 1.2V, 1.8V, 2.5V, 3.3V, 3.8V, or 5V

- Adjustable V<sub>OUT</sub> Up to 12V

- Internal Soft Start

- Output Discharge from SW

- 30ns Minimum On Time

- High Efficiency for Increased Battery Life and Improved Thermals

- 1.8μA Shutdown Current, 3.5μA Standby Current

- AAM Mode Increases Efficiency under Light Loads

- Integrated Low Resistance High-Side and Low-Side MOSFETs (22mΩ/11mΩ)

- Optimized for Low EMC/EMI

- 200kHz to 2.5MHz Configurable f<sub>SW</sub>

- Symmetric VIN Pinout Placement

- Low Noise at High Frequency Band by Quiet-FET™ Switching Technology

- FSS Modulation

- Synchronization to an External Clock

- CISPR25 Class 5 Compliant

- Mesh-Connect<sup>TM</sup> Package

- Available in QFN-23 (4mmx5mm) or TQFN-23 (4mmx5mm) Packages with Wettable Flanks

- Functional Safety System Design Capability

- MPSafe<sup>™</sup>-Compatible: Functional Safety Supporting Document Available

#### APPLICATIONS

- Automotive Infotainment

- Telematics

- Advanced Driver-Assistance Systems (ADAS)

- Industrial Power Systems

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

#### Note:

See the Ordering Information section on page 3 for the exact availability of each fixed output version. Additional output voltages may be available. Contact MPS for details.

1

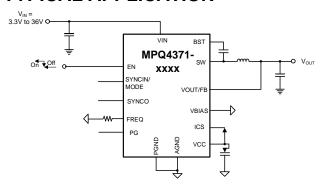

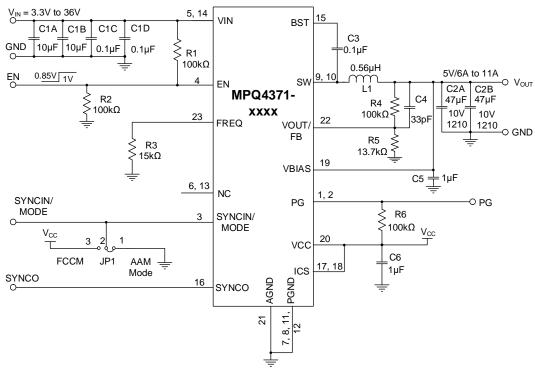

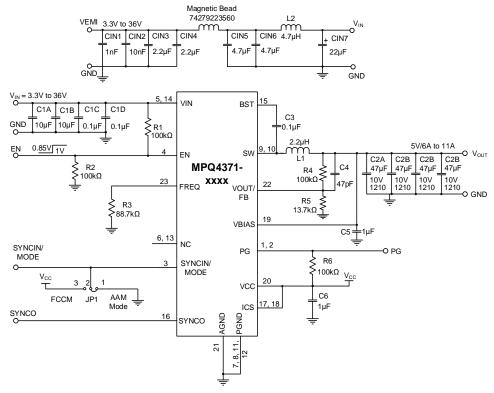

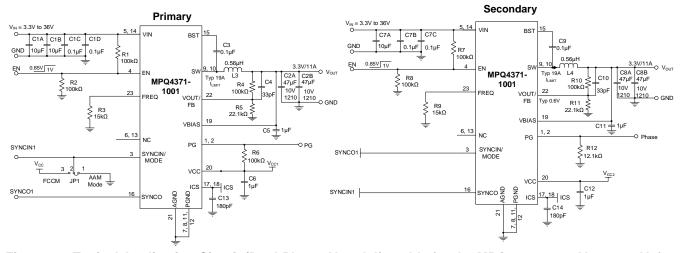

### TYPICAL APPLICATION

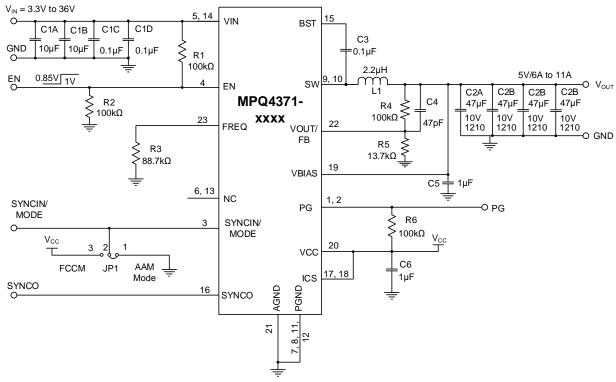

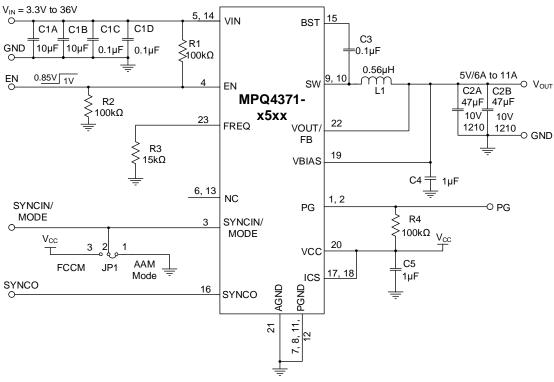

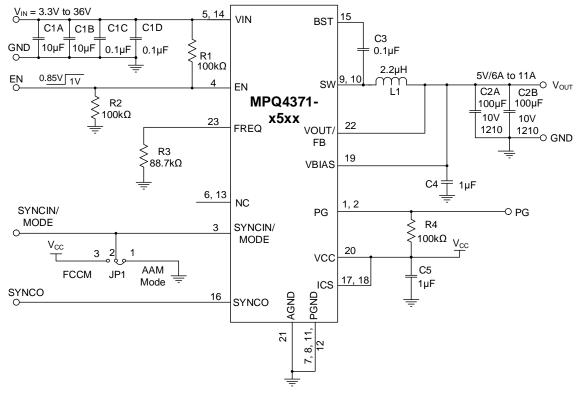

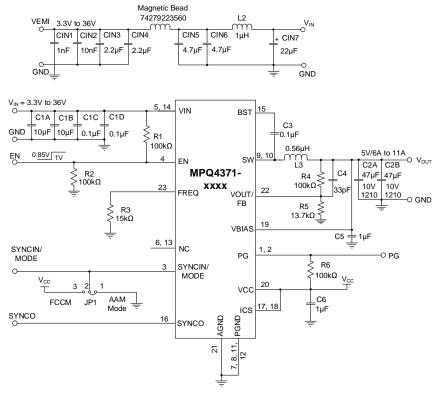

**Figure 1: Fixed Output Version**

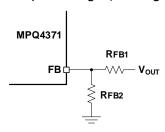

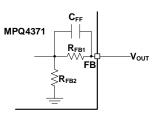

Figure 2: Adjustable Output Version

© 2024 MPS. All Rights Reserved.

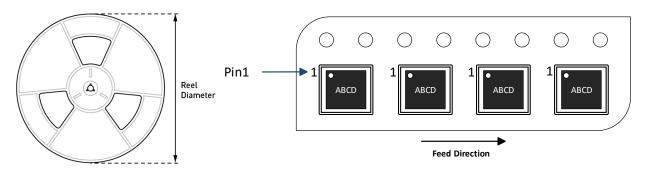

#### ORDERING INFORMATION

| Part Number (2)(3)*      | Package           | Top Marking | MSL Rating** |

|--------------------------|-------------------|-------------|--------------|

| MPQ4371GVE-xxxx-AEC1***  | QFN-23 (4mmx5mm)  | See Below   | 1            |

| MPQ4371GVTE-xxxx-AEC1*** | TQFN-23 (4mmx5mm) | See Below   | 1            |

\* For Tape & Reel, add suffix -Z (e.g. MPQ4371GVE-xxxx-AEC1-Z).

#### Notes:

- 2) Contact MPS for details regarding fixed-output versions.

- 3) The detailed information of part number can be marked as MPQ4371-WXYZ. Table 1 shows the meaning of 4-digit code.

**Table 1: Part Number Digit Code Naming Rules**

| Digit Code                               | Naming Rule          |

|------------------------------------------|----------------------|

|                                          | 1: 11A               |

| W: Defines the nominal load current      | 0: 10A               |

| W. Defines the nominal load current      | 8: 8A                |

|                                          | 6: 6A                |

|                                          | 0: Adjustable output |

|                                          | 1: Fixed 1V output   |

|                                          | A: Fixed 1.2V output |

| X: Defines the output voltage            | B: Fixed 1.8V output |

| A. Dennes the output voltage             | 2: Fixed 2.5V output |

|                                          | 3: Fixed 3.3V output |

|                                          | 4: Fixed 3.8V output |

|                                          | 5: Fixed 5V output   |

| Y: Defines the frequency spread spectrum | 0: With FSS          |

| (FSS) configuration                      | A: Without FSS       |

| 7: Defines the multi phase capability    | 0: Single-phase      |

| Z: Defines the multi-phase capability    | 1: Multi-phase       |

#### TOP MARKING

MPSYWW MP4371 LLLLLL E

MPS: MPS prefix Y: Year code WW: Week code MP4371: Part number LLLLL: Lot number E: Wettable flank

<sup>\*\*</sup> Moisture Sensitivity Level Rating

<sup>\*\*\*</sup> Wettable Flank

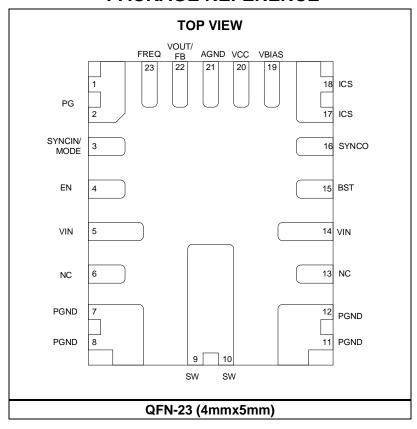

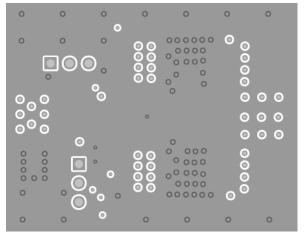

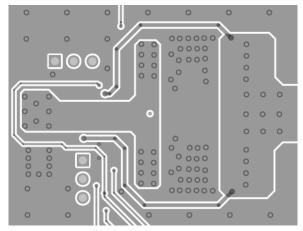

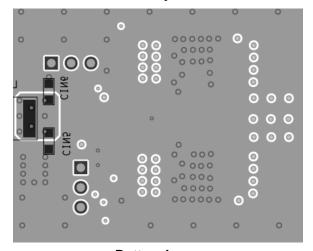

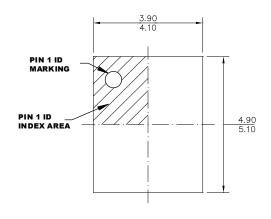

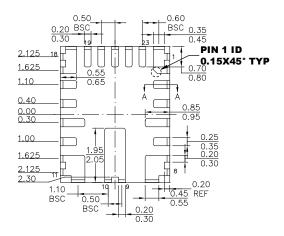

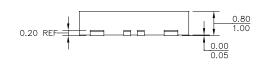

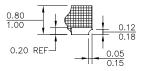

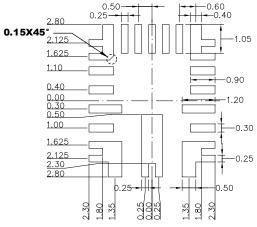

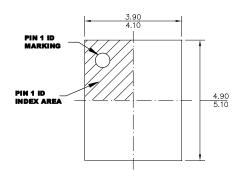

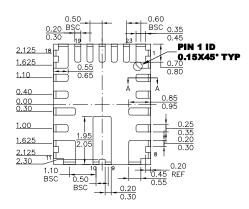

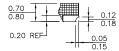

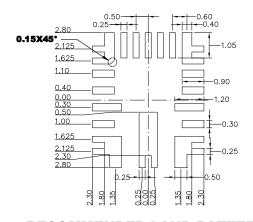

### **PACKAGE REFERENCE**

### **PIN FUNCTIONS**

| Pin#            | Name            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 |                 | Power good (PG) output and secondary phase selection. The output of the PG pin is an open drain.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1, 2            | PG              | For single-phase applications, PG must be connected to a power source by a pull-up resistor if the PG function is used. PG goes high if the output voltage ( $V_{OUT}$ ) is within 94% to 106% of the nominal voltage; PG goes low if $V_{OUT}$ exceeds 107% or falls below 93% of the nominal voltage. In single-phase applications, float PG when it is not used.                                                                                                                                                                                                                                                                         |

|                 |                 | For multi-phase applications, if the device is in primary mode, the PG pin's function is the same as it would be for a single-phase application. If the device is in secondary mode, connect a resistor to ground to set the phase shift. Then power good indication is disabled and does not pull high. The PG pin cannot be left floating for secondary devices. See the Power Good (PG) Indication or Phase Shift Setting section on page 70 for more information.                                                                                                                                                                       |

| 3               | SYNCIN/<br>MODE | <b>External sync input and primary mode selection.</b> Apply a clock signal to this pin to synchronize the internal oscillator frequency to the external clock. If the device is set as a primary device, use an external clock or pull this pin high to enter forced continuous conduction mode (FCCM). Pull this pin low to enable discontinuous conduction mode (DCM) and pulse-skipping at light loads. The pin has a weak internal pull-down resistor, so this pin can be floating to set advanced asynchronous modulation (AAM) mode. When the part is set as a secondary device, connect this pin to the primary device's SYNCO pin. |

| 4               | EN              | <b>Enable.</b> Pulling this pin below the specified threshold (0.85V) shuts the chip down. Pulling EN above the specified threshold (1V) enables the chip. EN can be directly connected to VIN. Do not float this pin.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5, 14           | VIN             | <b>Input supply.</b> VIN supplies power to all the internal control circuitry and the power switch connected to SW. A proper decoupling capacitance must be connected between VIN and PGND at each side of the IC to minimize switching spikes.                                                                                                                                                                                                                                                                                                                                                                                             |

| 6, 13           | NC              | <b>No connection.</b> The NC pin does not have an internal connection to the die. It can be left floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 7, 8, 11,<br>12 | PGND            | <b>Power ground.</b> Connect the PGND pin to a large GND plane to ensure excellent heat dissipation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 9, 10           | SW              | <b>Switch node.</b> The SW pin is connected to the high-side MOSFET's source and the low-side MOSFET's drain. Connect the power inductor to this pin with a wide trace and limit its area to avoid EMI radiation.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 15              | BST             | <b>Bootstrap.</b> The BST pin is the positive power supply for the high-side MOSFET driver connected to SW. Connect a bypass capacitor between BST and SW.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                 |                 | <b>Sync output and mode select for secondary.</b> When SYNCO is at high impedance, the device operates in primary operation mode, this pin outputs a clock signal in phase with the internal oscillator signal or external clock at the SYNCIN/MODE pin. In single-phase operation, this pin must be floating.                                                                                                                                                                                                                                                                                                                              |

| 16              | SYNCO           | In multi-phase applications, if this pin is tied to a low-impedance ground, voltage source, or clock, the device operates as a secondary device. When working as a secondary device, this pin selects the light-load operating mode (high for FCCM; low for AAM mode). In multi-phase applications, connect the SYNCO pin of all secondary devices together with the primary device's SYNC/MODE pin.                                                                                                                                                                                                                                        |

| 17, 18          | ICS             | <b>Current-sharing pin.</b> In a single-phase applications, connect ICS to the VCC pin. In a multiphase application, connect the ICS pins from all the parts together in order to improve the current sharing between the different phases.                                                                                                                                                                                                                                                                                                                                                                                                 |

### MPQ4371 - 36V, 6A TO 11A, ULTRA-LOW Iq, SYNC BUCK CONVERTER, AEC-Q100

# PIN FUNCTIONS (continued)

| Pin# | Name    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |         | Internal LDO supply. VBIAS is the power supply for the VCC regulator.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 19   | VBIAS   | The VCC regulator uses VBIAS as a power supply if the BIAS pin's voltage ( $V_{BIAS}$ ) is between 4.5V and 5.5V. This pin can be connected directly to the output voltage when $V_{OUT}$ is between 4.6V to 5.5V to improve the converter's efficiency, especially at high frequencies. Alternatively, connect this pin to another 5V rail if it is available in the system, and the current draw is <30mA. Add one decoupling capacitor between the VBIAS pin and GND if this function is used. |

|      |         | When there is no suitable power source for VBIAS, or the function is not used, connect this pin to the output voltage or GND.                                                                                                                                                                                                                                                                                                                                                                     |

|      |         | If $V_{OUT} > 5.5V$ , avoid connecting the VBIAS pin to the output. Avoid providing an external VBIAS voltage before VIN. Do not float this pin.                                                                                                                                                                                                                                                                                                                                                  |

| 20   | VCC     | <b>Internal LDO output.</b> VCC supplies 5V of power to the internal control circuit and gate drivers. A decoupling capacitor must be connected from VCC to AGND, and placed close to this pin.                                                                                                                                                                                                                                                                                                   |

| 21   | AGND    | <b>Analog ground.</b> Connect the AGND pin to the DC/DC GND and close to the VCC capacitor.                                                                                                                                                                                                                                                                                                                                                                                                       |

|      |         | <b>V</b> <sub>OUT</sub> <b>regulation input / feedback divider.</b> For the fixed-output version, connect this pin to the output voltage directly to regulate V <sub>OUT</sub> .                                                                                                                                                                                                                                                                                                                  |

| 22   | VOUT/FB | For the adjustable-output version, set Vout by connecting FB to the center point between the external resistor divider from the output and AGND. The feedback voltage is 0.6V. Place the resistor divider as close to FB as possible. Avoid placing many vias on the FB traces.                                                                                                                                                                                                                   |

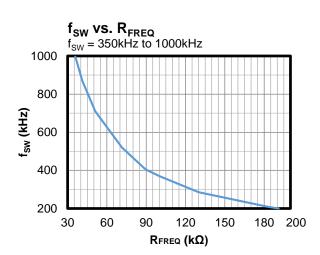

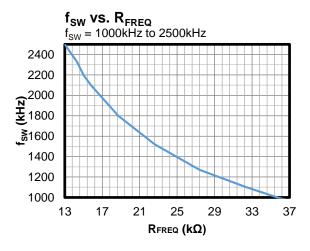

| 23   | FREQ    | <b>Switching frequency configurations.</b> Connect a resistor from the FREQ pin to ground to set the switching frequency (fsw).                                                                                                                                                                                                                                                                                                                                                                   |

### ESD Ratings

| Human body model (HB   | M)    | Cla   | ss 2 <sup>(6)</sup> |

|------------------------|-------|-------|---------------------|

| Charged-device model ( | (CDM) | Class | C2b (7)             |

### **Recommended Operating Conditions**

| Input voltage (V <sub>IN</sub> )          | 3.3V to 36V    |

|-------------------------------------------|----------------|

| V <sub>BIAS</sub>                         |                |

| Output voltage (V <sub>OUT</sub> )        | 0.6V to 12V    |

| Operating junction temp (T <sub>J</sub> ) | 40°C to +150°C |

| Thermal Resistance | $oldsymbol{	heta}$ JA | <b>Ө</b> ЈС            |           |

|--------------------|-----------------------|------------------------|-----------|

| QFN-23 (4mmx5mm)   |                       |                        |           |

| JESD51-7           | 41.2                  | 3.9                    | °C/W (8)  |

| EVQ4371-V-00A      | 22.8                  |                        | .°C/W (9) |

|                    |                       | $oldsymbol{\psi}_{JT}$ |           |

| JESD51-7           |                       | . 0.5                  | .°C/W (8) |

| EVQ4371-V-00A      |                       | 1.14                   | °C/W (9)  |

| TQFN-23 (4mmx5mm)  |                       |                        |           |

| JESD51-7           | 41.2                  | 3.9                    | °C/W (8)  |

|                    |                       | $oldsymbol{\psi}_{JT}$ |           |

| JESD51-7           |                       | . 0.4                  | .°C/W (8) |

#### Notes:

- 4) Exceeding these ratings may damage the device.

- 5) The maximum allowable power dissipation is a function of the maximum junction temperature,  $T_J$  (MAX), the junction-to-ambient thermal resistance,  $\theta_{JA}$ , and the ambient temperature,  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) =  $(T_J$  (MAX)  $T_A$ ) /  $\theta_{JA}$ . Exceeding the maximum allowable power dissipation can cause excessive die temperature, and the regulator may go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- 6) Per AECQ100-002.

- 7) Per AECQ100-011.

- 8) Measured on a JESD51-7, 4-layer PCB. The values given in this table are only valid for comparison with other packages and cannot be used for design purposes. These values were calculated in accordance with JESD51-7, and simulated on a specified JEDEC board. They do not represent the performance obtained in an actual application. The value of  $\theta_{\rm Jc}$  shows the thermal resistance from junction-to-case bottom. The value of  $\Psi_{\rm JT}$  shows the characterization parameter from junction-to-case top.

- Measured on an MPS standard EVB: 8.3cmx8.3cm, 2oz. copper thickness, 4-layer PCB. The value of Ψ<sub>JT</sub> shows the characterization parameter from junction-to-case top.

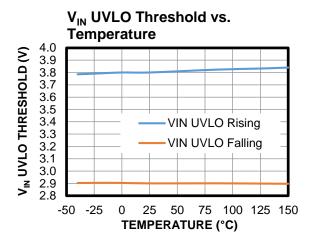

### **ELECTRICAL CHARACTERISTICS**

$V_{IN} = 12V$ ,  $V_{EN} = 2V$ ,  $T_J = -40$ °C to +150°C, typical values are at  $T_J = 25$ °C, unless otherwise noted...

| Parameter                                                                     | Symbol                    | Condition                                                                                                         | Min | Тур  | Max  | Units |

|-------------------------------------------------------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------|-----|------|------|-------|

| Input Supply                                                                  |                           |                                                                                                                   |     |      |      |       |

| Input voltage (V <sub>IN</sub> ) undervoltage lockout (UVLO) rising threshold | VIN <sub>UV_RISING</sub>  |                                                                                                                   | 3.6 | 3.8  | 4.1  | V     |

| V <sub>IN</sub> UVLO falling threshold                                        | VIN <sub>UV_FALLING</sub> |                                                                                                                   | 2.7 | 2.9  | 3.1  | V     |

| V <sub>IN</sub> UVLO hysteresis                                               | VIN <sub>UV_HYS</sub>     |                                                                                                                   |     | 0.9  |      | V     |

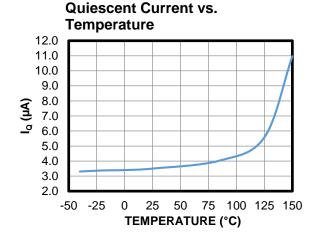

| VIN quiescent current (10)                                                    | lα                        | FB = 0.63V, no load,<br>SYNCIN/MODE = GND<br>(AAM mode), non-switching,<br>T <sub>J</sub> = -40 to +85°C          |     | 3.5  | 8.6  | μA    |

| viiv quiescent current                                                        | IQ                        | FB = 0.63V, no load,<br>SYNCIN/MODE = GND<br>(AAM mode), non-switching,<br>T <sub>J</sub> = -40 to +125°C         |     |      | 15   | μA    |

| VIN quiescent current (switching) (10)                                        | I <sub>Q_SLEEP</sub>      | SYNCIN/MODE = GND<br>(AAM mode), switching,<br>V <sub>BIAS</sub> = 5V, no load,<br>T <sub>J</sub> = -40 to +85°C  |     | 4.5  | 9    | μA    |

|                                                                               |                           | SYNCIN/MODE = GND<br>(AAM mode), switching,<br>V <sub>BIAS</sub> = 5V, no load,<br>T <sub>J</sub> = -40 to +125°C |     |      | 16.5 | μA    |

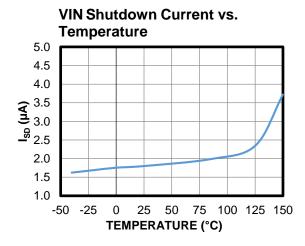

| VIN active current (non-switching)                                            | I <sub>Q_</sub> ACTIVE    | FB = 0.63V, no load,<br>SYNCIN/MODE = VCC<br>(CCM), non-switching                                                 |     | 1300 | 2300 | μA    |

| VIN shutdown current                                                          | I                         | $EN = 0V, T_J = -40^{\circ}C \text{ to } +85^{\circ}C$                                                            |     | 1.8  | 4    | μΑ    |

| VIIV SIIdidOWII Cullelli                                                      | Ishdn                     | EN = 0V                                                                                                           |     |      | 22.5 | μΑ    |

| V <sub>IN</sub> over-voltage protection (OVP) threshold                       | VINOVP_RISING             |                                                                                                                   | 36  | 38   | 40   | V     |

| V <sub>IN</sub> OVP hysteresis                                                | VINOVP_HYS                |                                                                                                                   |     | 1    |      | V     |

| VCC and VBIAS                                                                 |                           |                                                                                                                   |     |      |      |       |

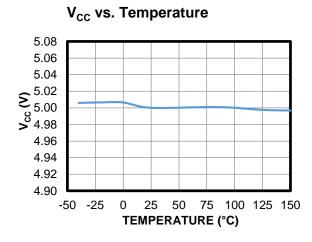

| VCC voltage                                                                   | Vcc                       | $I_{VCC} = 0mA$ , VCC from VIN                                                                                    | 4.8 | 5.0  | 5.2  | V     |

| VOO VOItage                                                                   | VCC                       | I <sub>VCC</sub> = 30mA, V <sub>BIAS</sub> = 5V                                                                   |     | 4.95 |      | V     |

| VCC regulation                                                                |                           | Ivcc = 30mA                                                                                                       |     | 1    |      | %     |

| VCC current limit                                                             | I <sub>LIMIT_VCC</sub>    | $V_{CC} = 4V$                                                                                                     | 89  | 120  | 167  | mA    |

|                                                                               | ·LIIVIII _ V C C          | Vcc = 0V                                                                                                          | 40  | 70   | 120  | mA    |

| VBIAS take-over rising threshold                                              | V <sub>BIAS-RISING</sub>  |                                                                                                                   |     | 4.5  |      | V     |

| VBIAS take-over hysteresis                                                    |                           |                                                                                                                   |     | 200  |      | mV    |

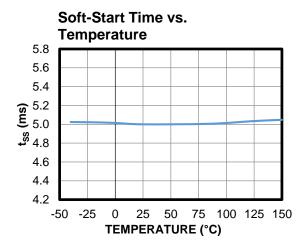

| Soft Start                                                                    |                           |                                                                                                                   |     |      |      |       |

| Soft-start time                                                               | t <sub>SS</sub>           | EN high to PG high                                                                                                | 4   | 5    | 6    | ms    |

|                                                                               |                           |                                                                                                                   |     |      |      |       |

# **ELECTRICAL CHARACTERISTICS** (continued)

$V_{IN}$  = 12V,  $V_{EN}$  = 2V,  $T_J$  = -40°C to +150°C, typical values are at  $T_J$  = 25°C, unless otherwise noted.

| Parameter                                                  | Symbol                         | Condition                                                            | Min  | Тур  | Max  | Units |

|------------------------------------------------------------|--------------------------------|----------------------------------------------------------------------|------|------|------|-------|

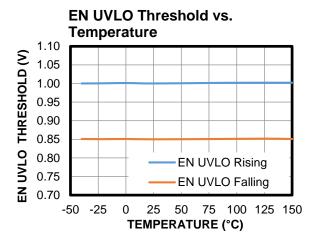

| EN Function                                                |                                |                                                                      |      |      |      |       |

| EN rising threshold                                        | VEN_RISING                     |                                                                      | 0.8  | 1    | 1.2  | V     |

| EN falling threshold                                       | Ven_falling                    |                                                                      | 0.65 | 0.85 | 1.05 | V     |

| EN hysteresis voltage                                      | V <sub>EN_HYS</sub>            |                                                                      |      | 150  |      | mV    |

| Output and Regulation                                      |                                |                                                                      |      |      |      |       |

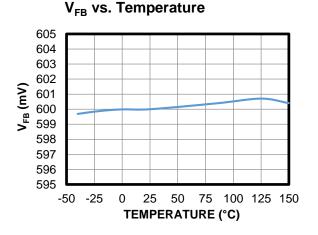

| FB voltage (adjustable output version)                     | V <sub>FB</sub>                |                                                                      | 594  | 600  | 606  | mV    |

| V <sub>OUT</sub> regulation voltage (fixed output version) | V <sub>OUT_REG</sub>           | V <sub>IN</sub> = 3.3V to 36V                                        | -1   |      | +1   | %     |

| FB leakage in fixed output version                         | Іvouт                          | Vout = Vvout_reg                                                     |      | 2.3  |      | μΑ    |

| FB leakage in adjustable output version                    |                                | FB = 0.63V                                                           |      | 1    | 100  | nA    |

| V <sub>OUT</sub> Discharge from SW                         | Idischarge                     | EN = 0V,<br>V <sub>OUT</sub> = 0.3V,<br>V <sub>IN</sub> = 3.3 to 36V | 2    |      |      | mA    |

| Switches and Frequency                                     |                                |                                                                      |      |      |      |       |

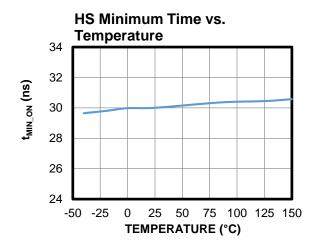

| Minimum on time <sup>(10)</sup>                            | ton_min                        |                                                                      | 12   | 30   | 35   | ns    |

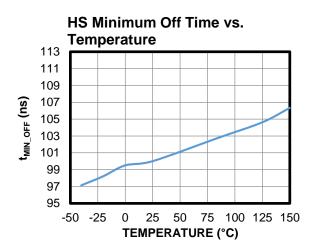

| Minimum off time <sup>(10)</sup>                           | t <sub>OFF_MIN</sub>           |                                                                      |      | 100  | 125  | ns    |

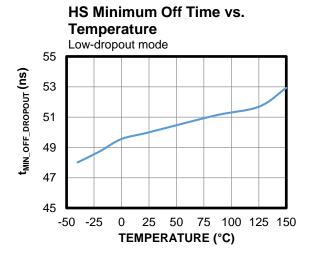

| Minimum off time in low-dropout mode (10)                  | toff_min_dropout               |                                                                      |      | 50   | 60   | ns    |

| Switch leakage current                                     | I <sub>SW_LKG</sub>            |                                                                      |      | 0.01 | 9    | μΑ    |

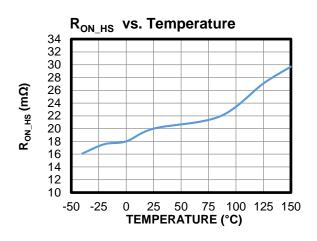

| High-side MOSFET (HS-FET) on resistance                    | R <sub>ON_H</sub> s            | V <sub>BST</sub> -V <sub>SW</sub> = 5V                               |      | 22   | 42   | mΩ    |

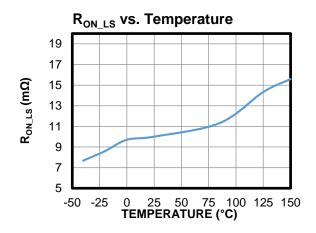

| Low-side MOSFET (LS-FET) on resistance                     | Ron_ls                         | Vcc = 5V                                                             |      | 11   | 22   | mΩ    |

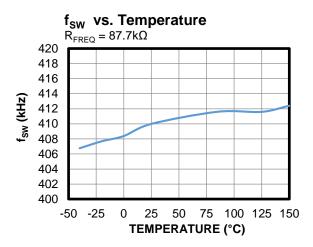

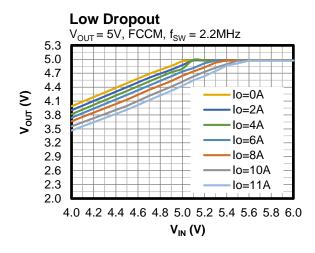

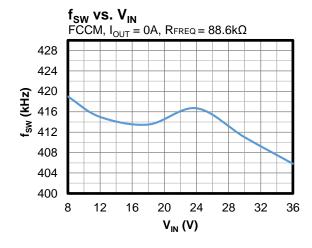

|                                                            |                                | $R_{FREQ} = 88.7 k\Omega$                                            | 370  | 410  | 450  | kHz   |

| Switching frequency                                        | fsw                            | $R_{FREQ} = 33k\Omega$                                               | 900  | 1000 | 1100 | kHz   |

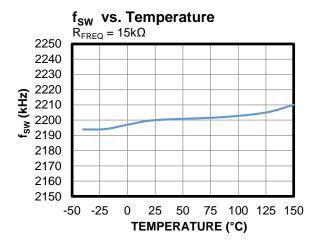

|                                                            |                                | $R_{FREQ} = 15k\Omega$                                               | 1980 | 2200 | 2420 | kHz   |

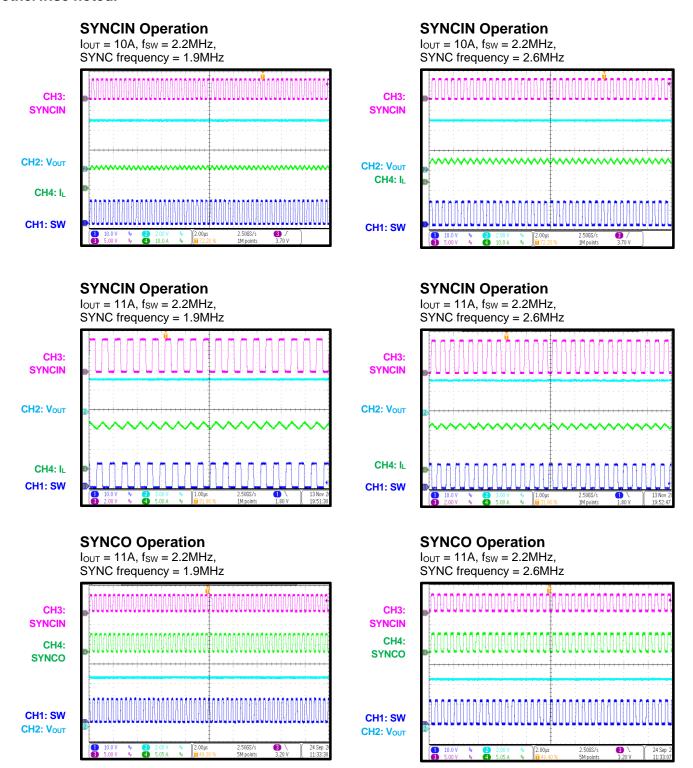

| SYNCIN and SYNCO                                           |                                |                                                                      |      |      |      |       |

| SYNCIN voltage rising threshold                            | VSYNC_RISING                   |                                                                      |      |      | 1.4  | V     |

| SYNCIN voltage falling threshold                           | Vsync_falling                  |                                                                      | 0.4  |      |      | V     |

| SYNCIN timeout                                             | tmode                          | SYNCIN/MODE low to DCM                                               | 30   |      | 65   | μs    |

| SYNCIN clock range                                         | fsync                          | % of free-running frequency (fsw)                                    | 90   |      | 110  | %     |

| SYNCO high voltage                                         | Vsynco_High                    | Isynco = -1mA                                                        | 3.3  | 4.5  |      | V     |

| SYNCO low voltage                                          | Vsynco_Low                     | Isynco = 1mA                                                         |      |      | 0.4  | V     |

| BST                                                        | •                              | •                                                                    | •    | •    | •    | •     |

| BST-SW refresh rising threshold                            | V <sub>UVBST-SW-RISING</sub>   |                                                                      |      | 2.5  |      | V     |

| BST-SW refresh falling threshold                           | V <sub>UVBST</sub> -SW-FALLING |                                                                      |      | 2.3  |      | V     |

| BST-SW refresh hysteresis                                  | Vuvbst-sw_hys                  |                                                                      | 0.19 |      |      | V     |

|                                                            |                                |                                                                      |      |      |      |       |

© 2024 MPS. All Rights Reserved.

# **ELECTRICAL CHARACTERISTICS** (continued)

$V_{IN} = 12V$ ,  $V_{EN} = 2V$ ,  $T_J = -40$ °C to +150°C, typical values are at  $T_J = 25$ °C, unless otherwise noted.

| Parameter                                  | Symbol                    | Condition                          | Min  | Тур  | Max  | Units |

|--------------------------------------------|---------------------------|------------------------------------|------|------|------|-------|

| ICS                                        |                           |                                    |      |      |      |       |

| Current-sharing gain                       | Gcs                       |                                    |      | 30   |      | mV/A  |

| PG Function                                |                           |                                    |      |      |      | -     |

| PG rising threshold                        | V <sub>PGVTH_RISING</sub> | V <sub>OUT</sub> rising            | 91%  | 94%  | 97%  |       |

| PG fishing trifeshold                      | VPGVIH_RISING             | Vouт falling                       | 103% | 106% | 109% |       |

| PC falling throshold                       | Vacuati au ma             | Vouт falling                       | 90%  | 93%  | 96%  | Vout  |

| PG falling threshold                       | VPGVTH_FALLING            | Vout rising                        | 104% | 107% | 110% | V 001 |

| PG trip threshold hysteresis               | V <sub>PGVTH_HYS</sub>    |                                    |      | 1    |      |       |

| PG output voltage low                      | V <sub>PG_LOW</sub>       | Isink = 1mA                        |      | 10   | 100  | mV    |

| PG rising deglitch                         | tpg_r_delay               |                                    |      | 120  |      | μs    |

| PG falling deglitch                        | tpg_f_delay               |                                    |      | 100  |      | μs    |

| Protections                                |                           |                                    |      |      |      |       |

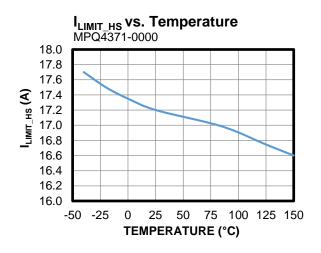

|                                            | ILIMIT_HS                 | Duty cycle = 30%, for MPQ4371-1XYZ | 16.6 | 19   | 22   |       |

| HS current limit (11)                      |                           | Duty cycle = 30%, for MPQ4371-0XYZ | 15.2 | 17.2 | 19   | A     |

| 113 Current IIIIII.                        |                           | Duty cycle = 30%, for MPQ4371-8XYZ | 12.6 | 13.8 | 15   |       |

|                                            |                           | Duty cycle = 30%, for MPQ4371-6XYZ | 8.6  | 10.3 | 12   |       |

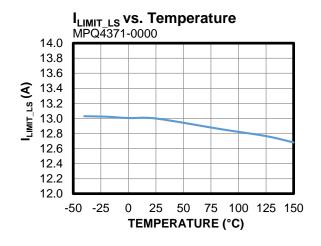

|                                            |                           | Duty cycle = 30%, for MPQ4371-1XYZ | 11.2 | 13.2 |      |       |

| LS valley current                          | 1                         | Duty cycle = 30%, for MPQ4371-0XYZ | 10.2 | 13   | 15.2 | A     |

| limit (11)                                 | ILIMIT_LS                 | Duty cycle = 30%, for MPQ4371-8XYZ | 8.2  | 9.6  |      | _ ^   |

|                                            |                           | Duty cycle = 30%, for MPQ4371-6XYZ | 6.2  | 7.2  |      |       |

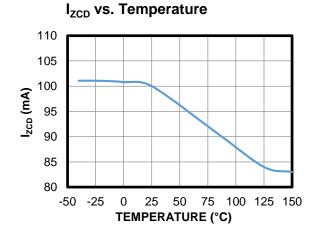

| Zero-current<br>detection (ZCD)<br>current | Izco                      | AAM mode                           | 0    | 100  | 300  | mA    |

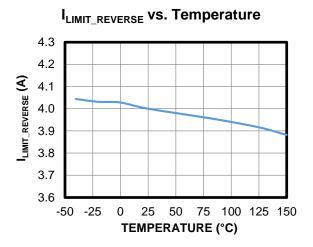

| LS reverse current limit                   | ILIMIT_REVERSE            | FCCM                               | -5.2 | -4   | -2.8 | А     |

| Thermal shutdown                           | T <sub>SD</sub>           |                                    | 150  | 180  |      | °C    |

| Thermal shutdown hysteresis (10)           | T <sub>SD_HYS</sub>       |                                    |      | 30   |      | °C    |

#### Notes:

<sup>10)</sup> Derived from bench characterization, not tested in production.

<sup>11)</sup> Cannot test in production for the MPQ4371-1XYZ/8XYZ/6XYZ. Guaranteed by design and bench test characterization.

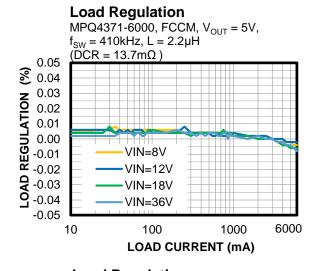

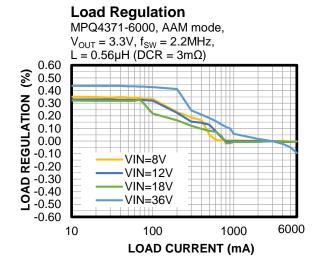

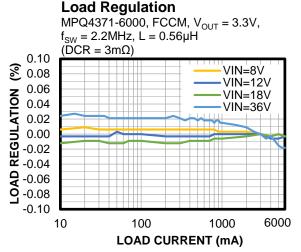

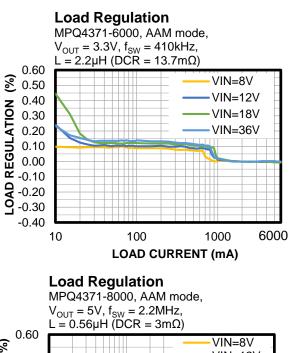

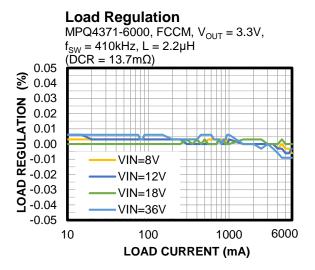

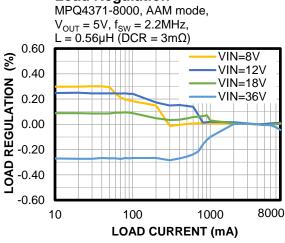

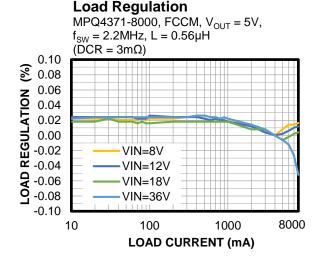

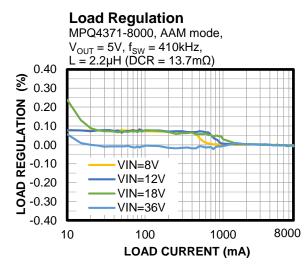

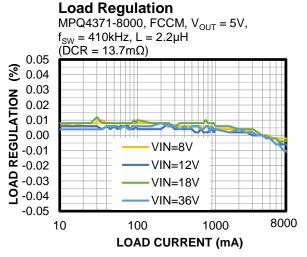

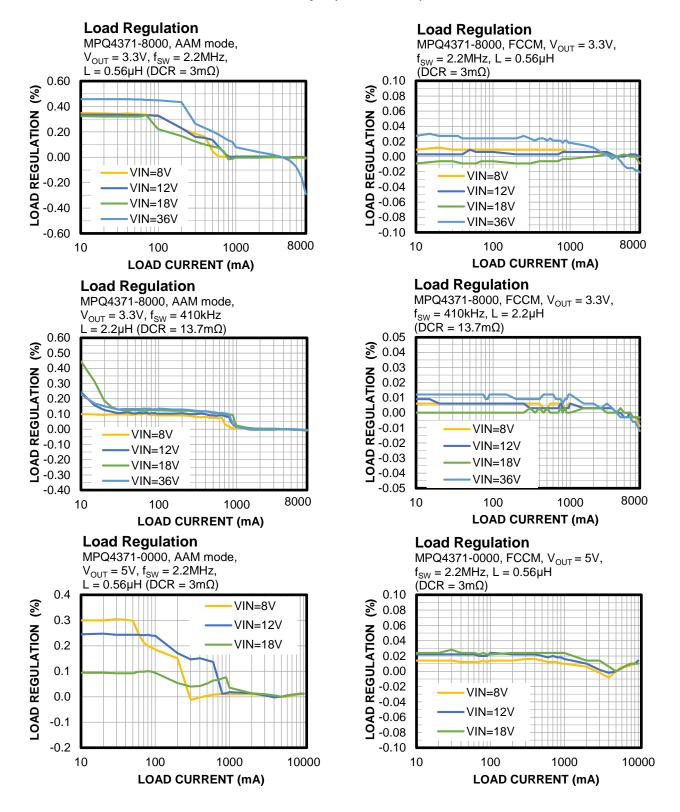

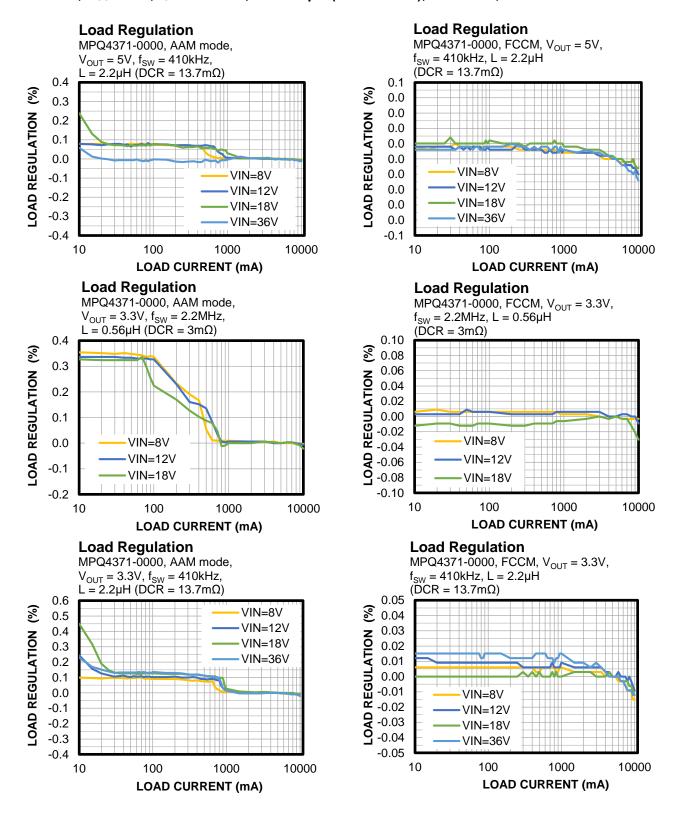

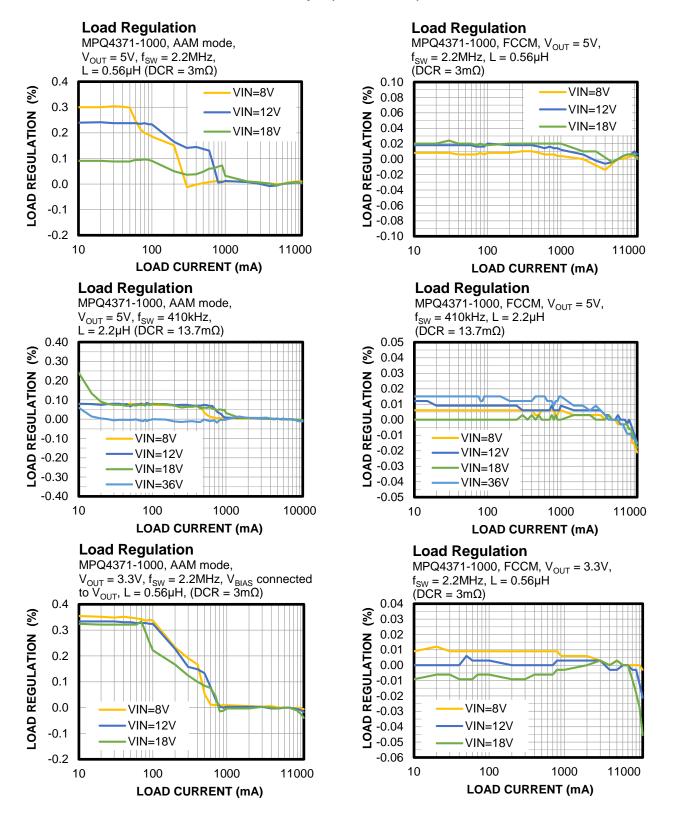

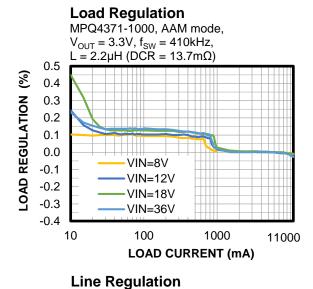

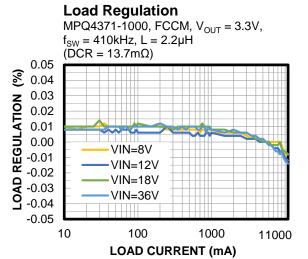

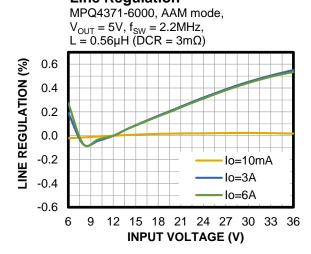

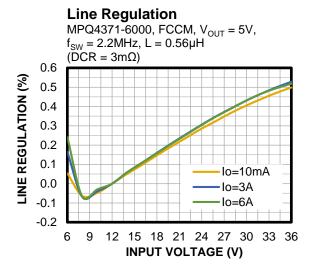

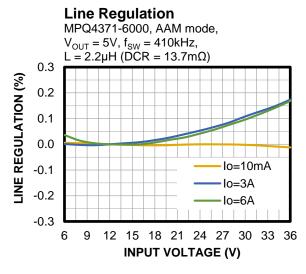

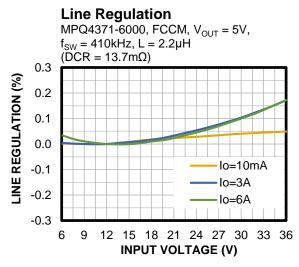

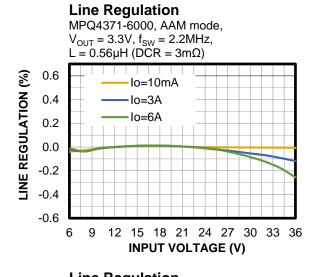

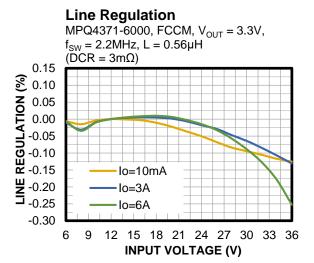

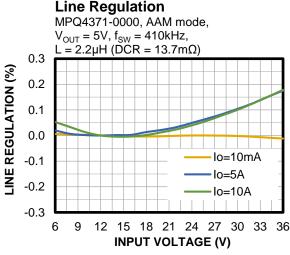

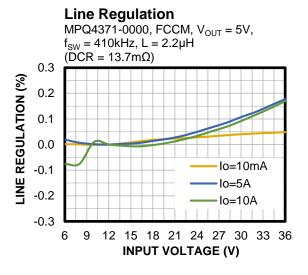

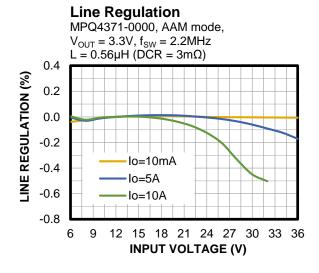

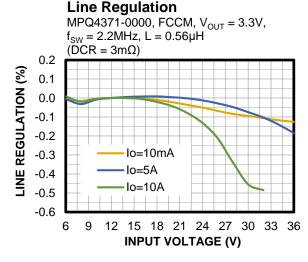

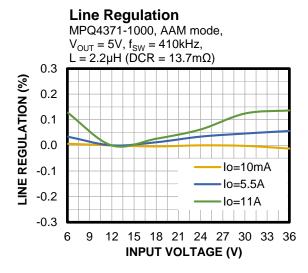

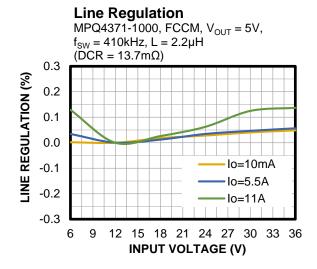

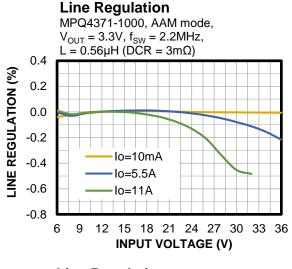

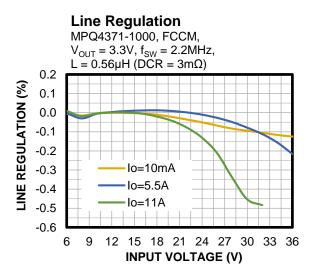

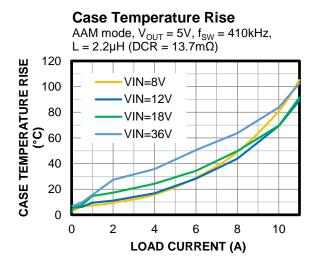

#### TYPICAL CHARACTERISTICS

$V_{IN} = 12V$ ,  $V_{OUT} = 5V$ ,  $T_{J} = -40$ °C to +150°C, unless otherwise noted.

MPQ4371 - 36V, 6A TO 11A, ULTRA-LOW IQ, SYNC BUCK CONVERTER, AEC-Q100

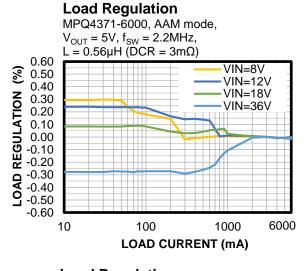

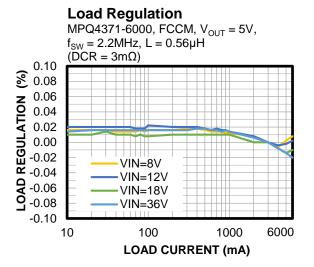

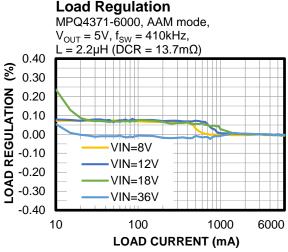

### TYPICAL CHARACTERISTICS (continued)

$V_{IN} = 12V$ ,  $V_{OUT} = 5V$ ,  $T_J = -40$ °C to +150°C, unless otherwise noted.

MPQ4371 - 36V, 6A TO 11A, ULTRA-LOW IQ, SYNC BUCK CONVERTER, AEC-Q100

### **TYPICAL CHARACTERISTICS** (continued)

$V_{IN} = 12V$ ,  $V_{OUT} = 5V$ ,  $T_{J} = -40$ °C to +150°C, unless otherwise noted.

### TYPICAL CHARACTERISTICS (continued)

$V_{IN}$  = 12V,  $V_{OUT}$  = 5V,  $T_J$  = -40°C to +150°C, unless otherwise noted.

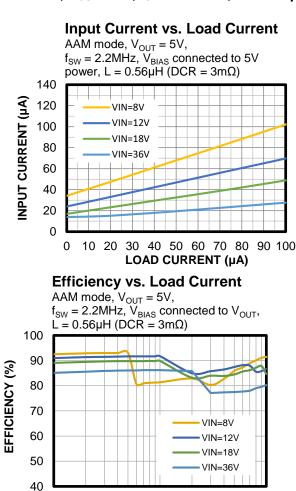

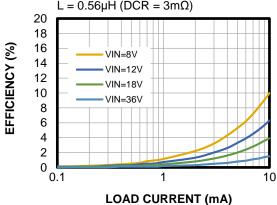

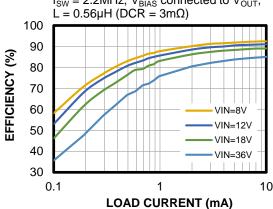

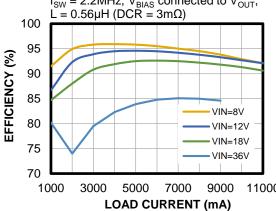

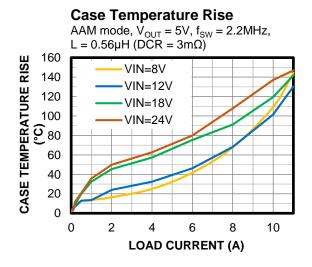

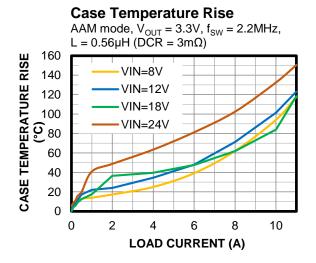

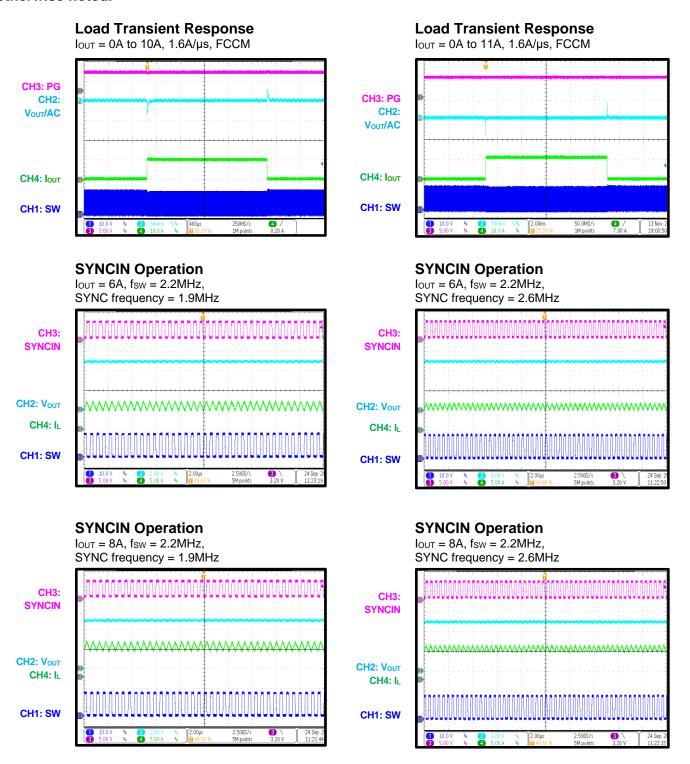

#### TYPICAL PERFORMANCE CHARACTERISTICS

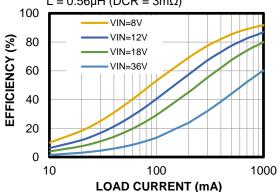

$V_{IN} = 12V$ ,  $V_{OUT} = 5V$ ,  $f_{SW} = 2.2MHz$ ,  $L = 0.56\mu H$  (DCR =  $3m\Omega$ ),  $T_A = 25^{\circ}C$ , unless otherwise noted.

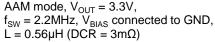

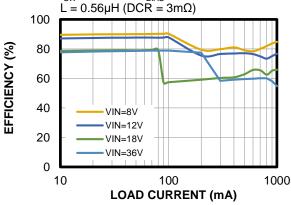

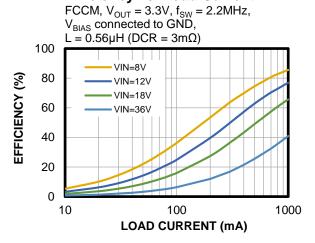

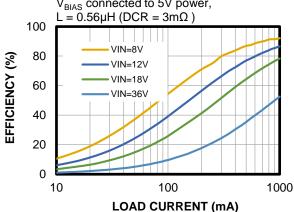

## Efficiency vs. Load Current

100

LOAD CURRENT (mA)

1000

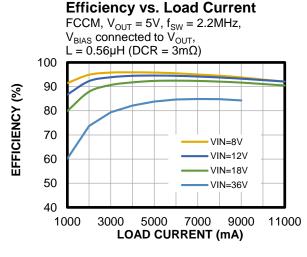

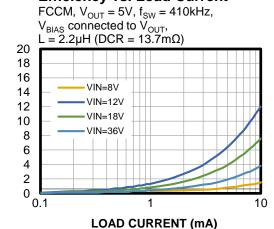

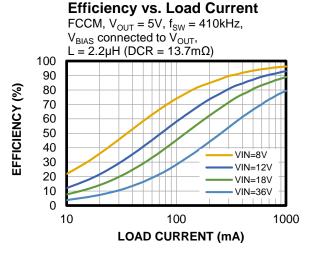

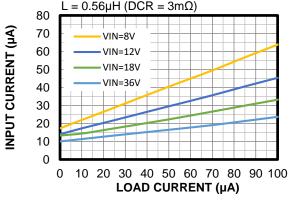

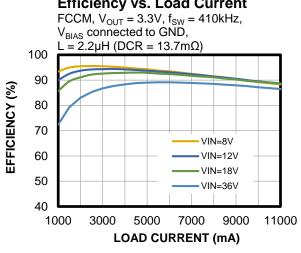

FCCM,  $V_{OUT} = 5V$ ,  $f_{SW} = 2.2MHz$ ,  $V_{BIAS}$  connected to  $V_{OUT}$ ,  $L = 0.56 \mu H (DCR = 3m\Omega)$

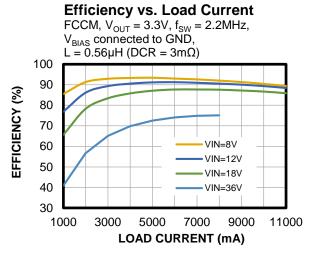

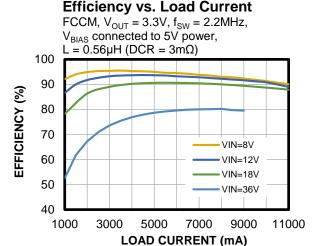

### **Efficiency vs. Load Current**

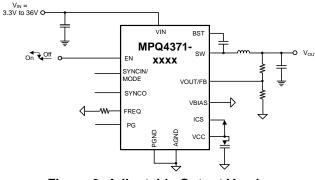

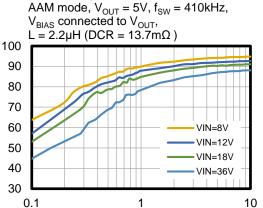

AAM mode,  $V_{OUT} = 5V$ ,  $f_{SW} = 2.2 MHz$ ,  $V_{BIAS}$  connected to  $V_{OUT}$ ,  $L = 0.56 \mu H$  (DCR =  $3 m \Omega$ )

### **Efficiency vs. Load Current**

AAM mode,  $V_{OUT} = 5V$ ,  $f_{SW} = 2.2MHz$ ,  $V_{BIAS}$  connected to  $V_{OUT}$ ,  $L = 0.56\mu H$  (DCR =  $3m\Omega$ )

#### Efficiency vs. Load Current

FCCM,  $V_{OUT} = 5V$ ,  $f_{SW} = 2.2MHz$ ,  $V_{BIAS}$  connected to  $V_{OUT}$ ,  $L = 0.56\mu H$  (DCR =  $3m\Omega$ )

10

40

20 0

### TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{IN} = 12V$ ,  $V_{OUT} = 5V$ ,  $f_{SW} = 2.2MHz$ ,  $L = 0.56\mu H$  (DCR =  $3m\Omega$ ),  $T_A = 25^{\circ}C$ , unless otherwise noted.

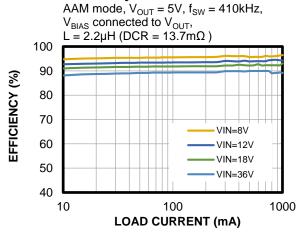

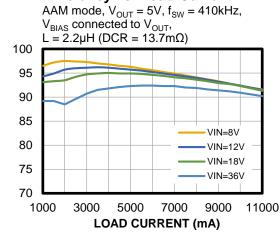

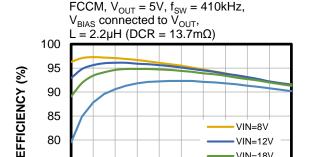

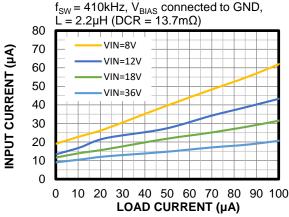

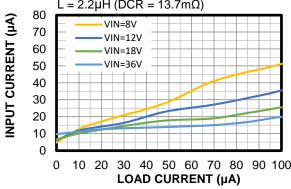

#### AAM mode, $V_{OUT} = 5V$ , $f_{SW} = 410kHz$ , V<sub>BIAS</sub> connected to V<sub>OUT</sub>, $L = 2.2 \mu H (DCR = 13.7 m\Omega)$ 160 VIN=8V INPUT CURRENT (µA) 140 VIN=12V 120 VIN=18V 100 VIN=36V 80 60

Input Current vs. Load Current

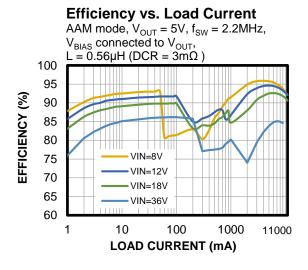

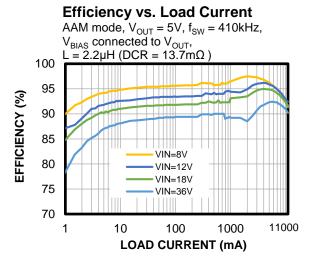

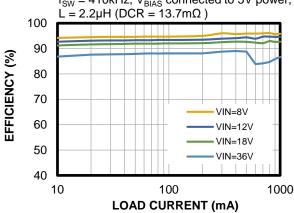

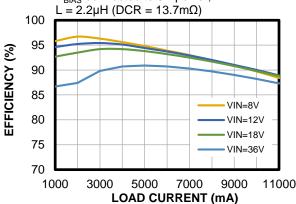

#### **Efficiency vs. Load Current**

10 20 30 40 50 60 70 80 90 100

LOAD CURRENT (µA)

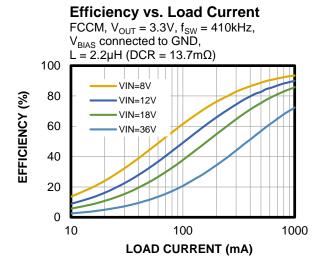

#### Efficiency vs. Load Current

LOAD CURRENT (mA)

#### Efficiency vs. Load Current

**EFFICIENCY (%)**

**EFFICIENCY (%)**

**EFFICIENCY (%)**

75

70

1000

3000

### TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{IN} = 12V$ ,  $V_{OUT} = 5V$ ,  $f_{SW} = 2.2MHz$ ,  $L = 0.56\mu H$  (DCR =  $3m\Omega$ ),  $T_A = 25^{\circ}C$ , unless otherwise noted.

5000

**Efficiency vs. Load Current**

7000

LOAD CURRENT (mA)

VIN=18V

VIN=36V

9000

Efficiency vs. Load Current

#### Input Current vs. Load Current

#### Efficiency vs. Load Current

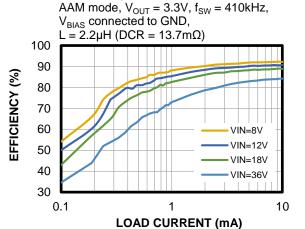

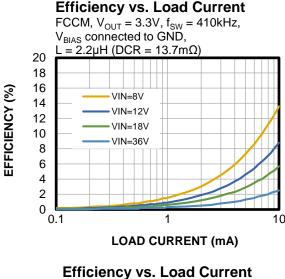

### Efficiency vs. Load Current

50

40

30

20

0.1

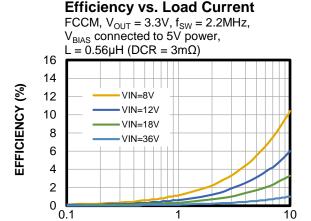

### TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{IN} = 12V$ ,  $V_{OUT} = 5V$ ,  $f_{SW} = 2.2MHz$ ,  $L = 0.56\mu H$  (DCR =  $3m\Omega$ ),  $T_A = 25^{\circ}C$ , unless otherwise noted.

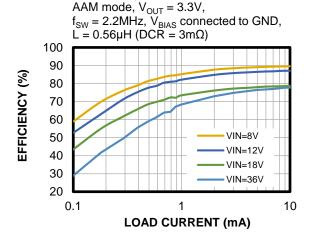

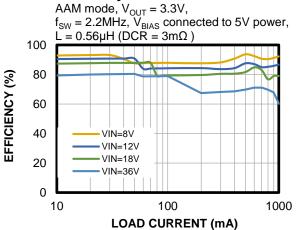

### AAM mode, $V_{OUT} = 3.3V$ , $f_{SW} = 2.2MHz$ , $V_{BIAS}$ connected to 5V power, $L = 0.56\mu H (DCR = 3m\Omega)$ 100 90 **EFFICIENCY (%)** 80 70 60 VIN=8V

VIN=12V

VIN=18V

VIN=36V

10

Efficiency vs. Load Current

#### Efficiency vs. Load Current

#### Efficiency vs. Load Current

1

LOAD CURRENT (mA)

#### **Efficiency vs. Load Current**

#### Efficiency vs. Load Current

### TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{IN} = 12V$ ,  $V_{OUT} = 5V$ ,  $f_{SW} = 2.2MHz$ ,  $L = 0.56\mu H$  (DCR =  $3m\Omega$ ),  $T_A = 25^{\circ}C$ , unless otherwise noted.

LOAD CURRENT (mA)

Efficiency vs. Load Current

#### Input Current vs. Load Current

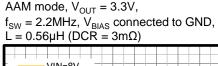

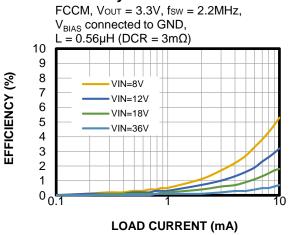

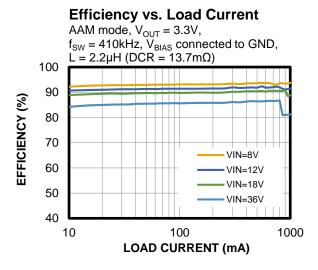

AAM mode,  $V_{OUT} = 3.3V$ ,  $f_{SW} = 410kHz$ ,  $V_{BIAS}$  connected to GND,  $L = 2.2 \mu H (DCR = 13.7 m\Omega)$

### Efficiency vs. Load Current

19

### TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{IN} = 12V$ ,  $V_{OUT} = 5V$ ,  $f_{SW} = 2.2MHz$ ,  $L = 0.56\mu H$  (DCR =  $3m\Omega$ ),  $T_A = 25^{\circ}C$ , unless otherwise noted.

#### Input Current vs. Load Current

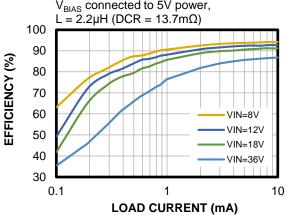

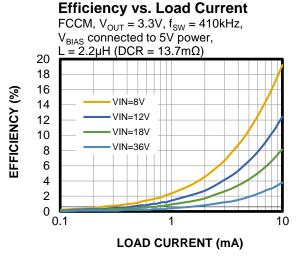

AAM mode, V<sub>OUT</sub> = 3.3V, f<sub>SW</sub> = 410kHz, V<sub>BIAS</sub> connected to 5V power,

#### **Efficiency vs. Load Current**

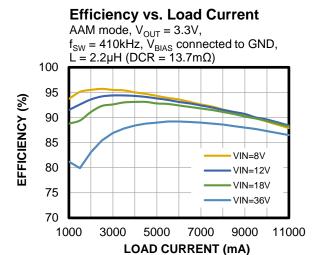

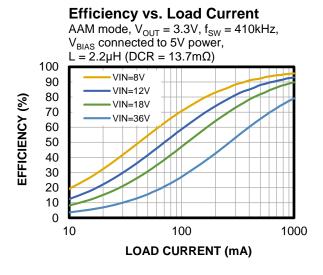

AAM mode,  $V_{OUT} = 3.3V$ ,  $f_{SW} = 410kHz$ ,  $V_{BIAS}$  connected to 5V power,

#### Efficiency vs. Load Current

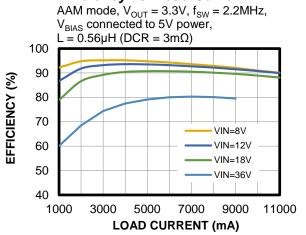

AAM mode,  $V_{OUT} = 3.3V$ ,  $f_{SW} = 410kHz$ ,  $V_{BIAS}$  connected to 5V power, L = 2.2uH (DCR =  $13.7m\Omega$ )

#### Efficiency vs. Load Current

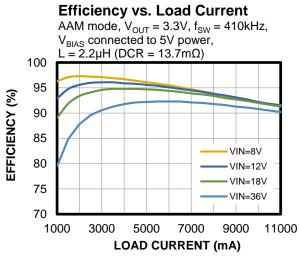

AAM mode, Vout = 3.3V, fsw = 410kHz,  $V_{BIAS}$  connected to 5V power,  $L = 2.2\mu H$  (DCR = 13.7m $\Omega$ )

$V_{IN} = 12V$ ,  $V_{OUT} = 5V$ ,  $f_{SW} = 2.2MHz$ ,  $L = 0.56\mu H$  (DCR =  $3m\Omega$ ),  $T_A = 25^{\circ}C$ , unless otherwise noted.

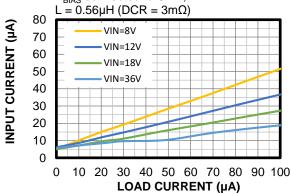

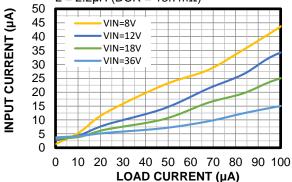

#### MPQ4371-x5xx, AAM mode, $V_{OUT} = 5V$ , $f_{SW} = 2.2MHz$ , $V_{\text{BIAS}}$ connected to $V_{\text{OUT}}$ , $L = 0.56\mu H (DCR = 3m\Omega)$ 100 INPUT CURRENT (µA) VIN=8V 80 VIN=12V VIN=18V 60 VIN=36V 40 20 10 20 30 40 50 60 70 80 90 100 LOAD CURRENT (µA)

Input Current vs. Load Current

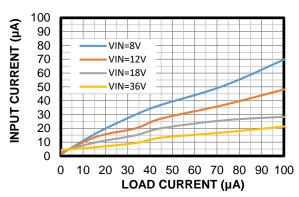

#### Input Current vs. Load Current

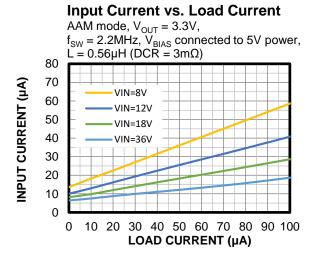

MPQ4371-x3xx, AAM mode,  $V_{OUT} = 3.3V$ ,  $f_{SW} = 2.2MHz$ ,  $V_{BIAS}$  connected to GND,  $L = 0.56\mu H$  (DCR = 3mΩ)

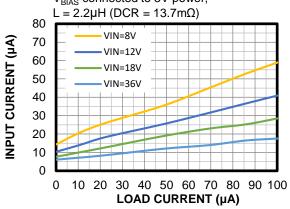

### Input Current vs. Load Current

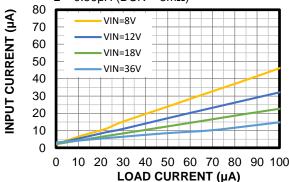

MPQ4371-x3xx, AAM mode,  $V_{OUT}$  = 3.3V,  $f_{SW}$  = 410kHz,  $V_{BIAS}$  connected to GND, L = 2.2 $\mu$ H (DCR = 13.7m $\Omega$ )

#### Input Current vs. Load Current for

MPQ4371-x5xx, AAM mode,  $V_{OUT}$  = 5V,  $f_{SW}$  = 410kHz,  $V_{BIAS}$  connected to  $V_{OUT}$ , L = 2.2μH (DCR = 13.7mΩ)

#### Input Current vs. Load Current

MPQ4371-x3xx, AAM mode,  $V_{OUT}=3.3V, f_{SW}=2.2MHz$   $V_{BIAS}$  connected to 5V power,  $L=0.56\mu H \ (DCR=3m\Omega)$

#### Input Current vs. Load Current

MPQ4371-x3xx, AAM mode,  $V_{OUT} = 3.3V$ ,  $f_{SW} = 410$ kHz,  $V_{BIAS}$  connected to 5V power,  $L = 2.2\mu H$  (DCR =  $13.7m\Omega$ )

$V_{IN} = 12V$ ,  $V_{OUT} = 5V$ ,  $f_{SW} = 2.2MHz$ ,  $L = 0.56\mu H$  (DCR =  $3m\Omega$ ),  $T_A = 25^{\circ}C$ , unless otherwise noted.

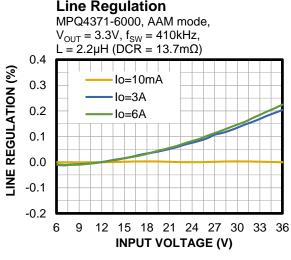

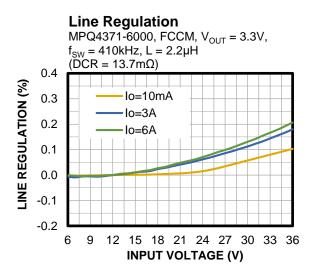

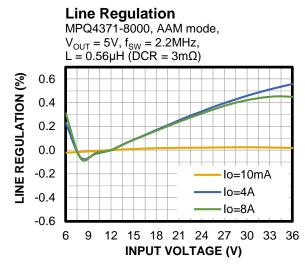

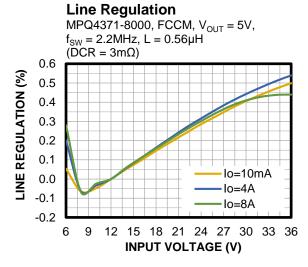

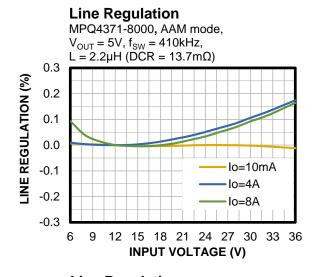

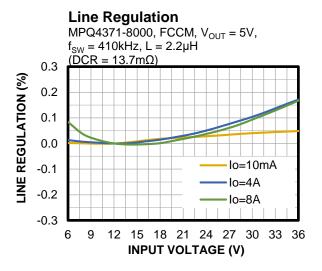

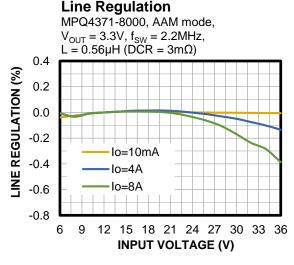

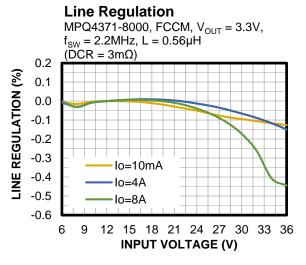

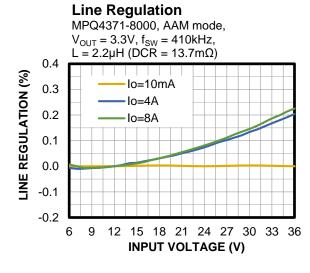

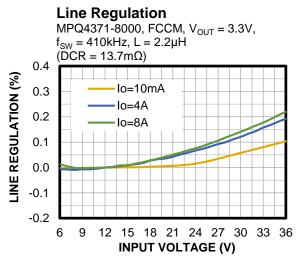

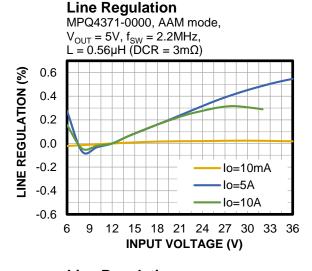

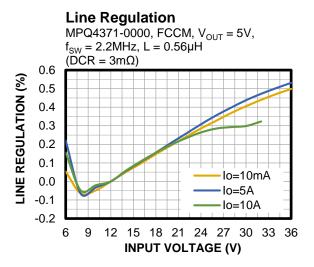

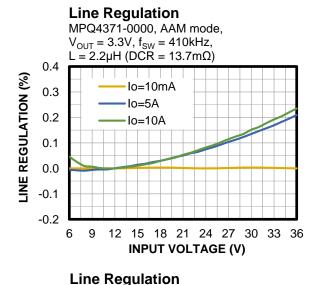

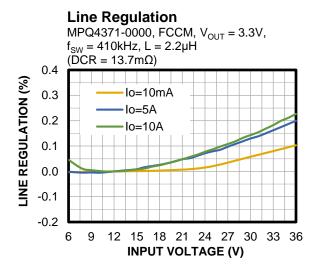

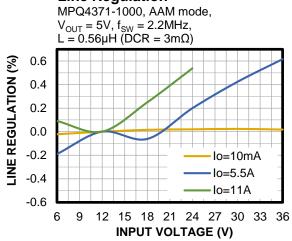

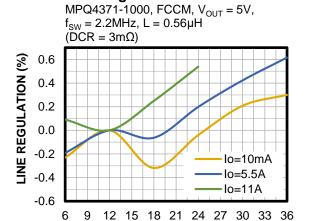

**INPUT VOLTAGE (V)**

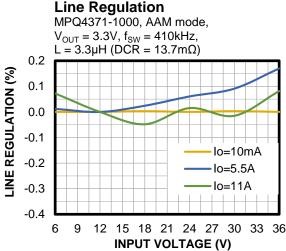

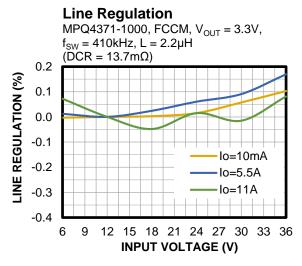

**Line Regulation**

32

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

### TYPICAL PERFORMANCE CHARACTERISTICS (continued)

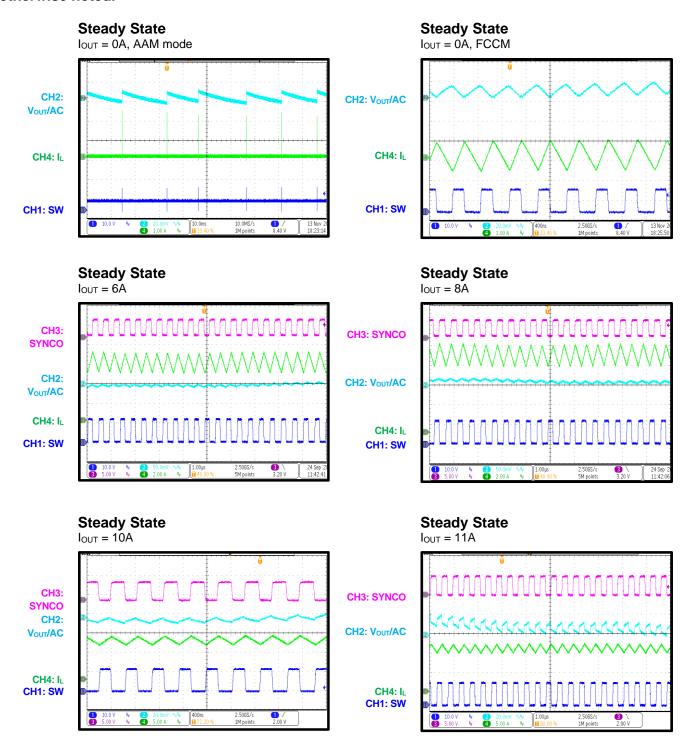

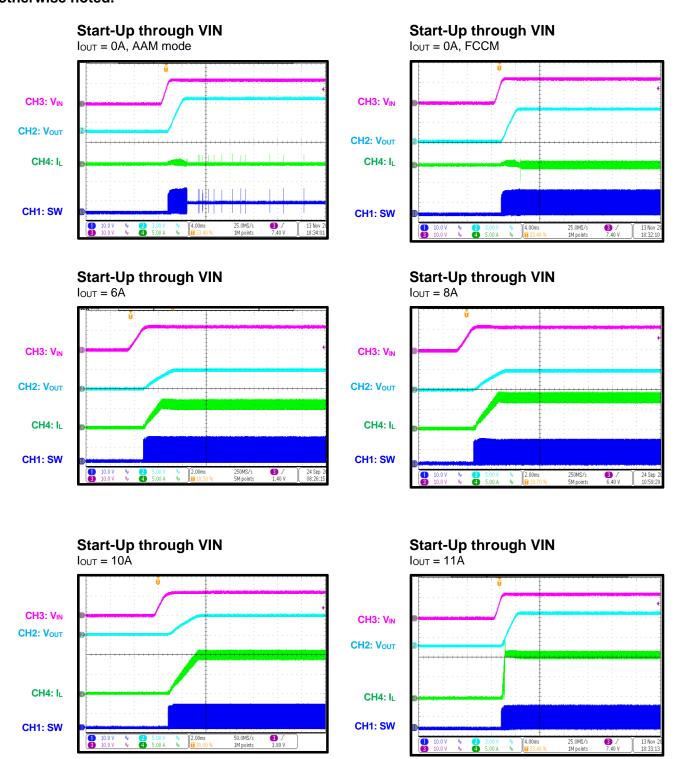

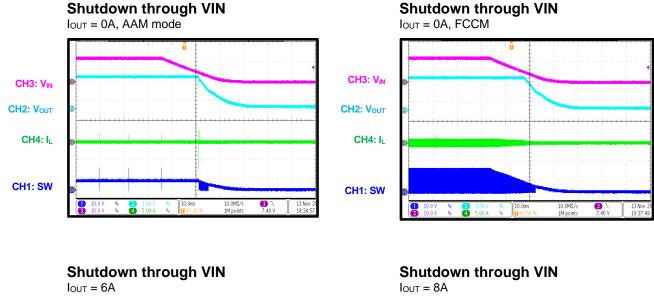

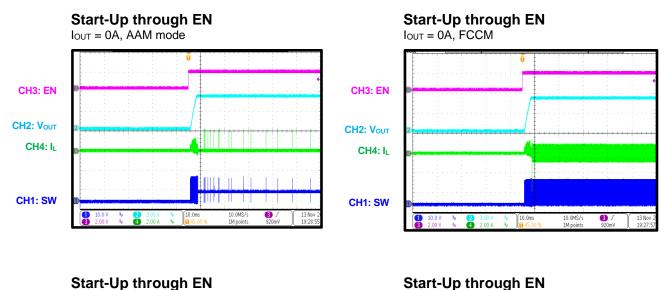

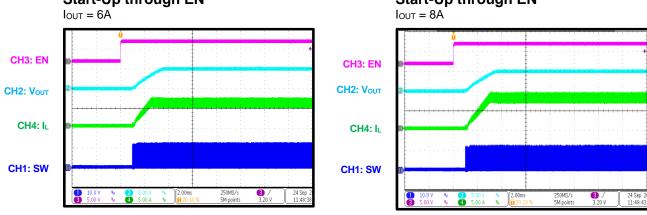

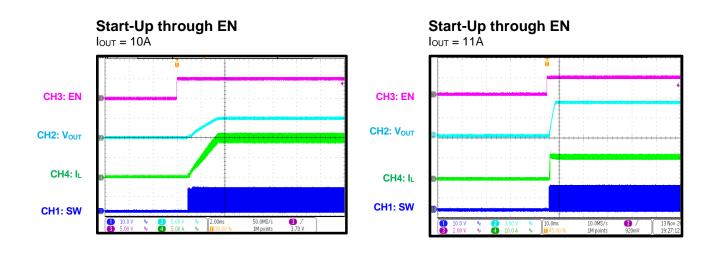

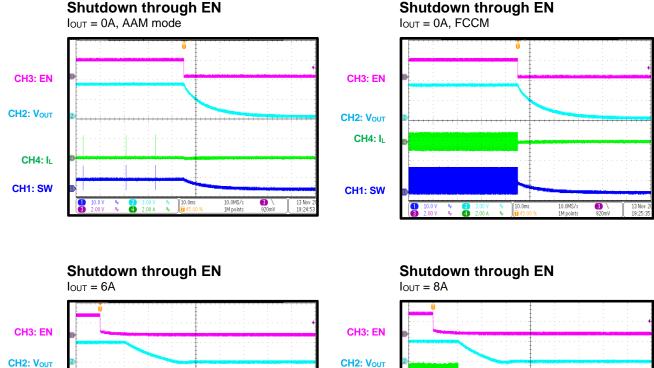

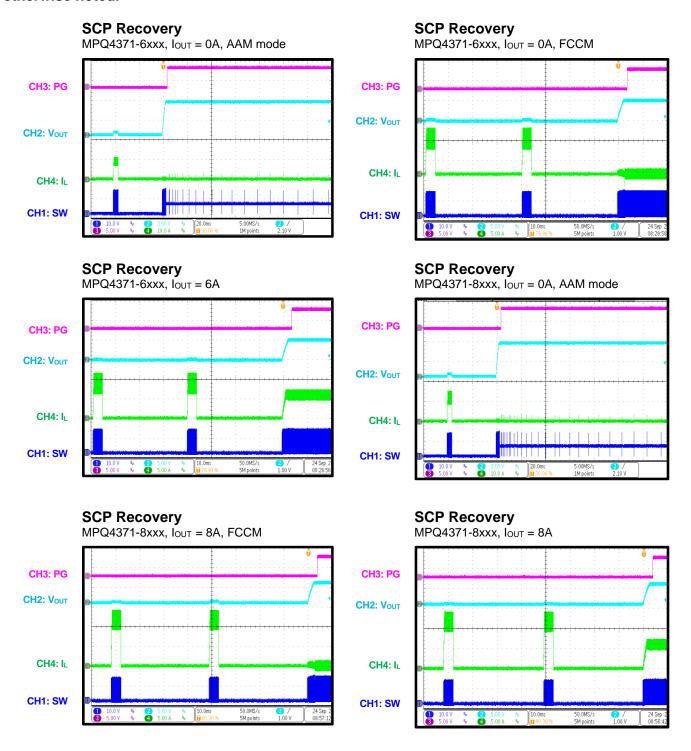

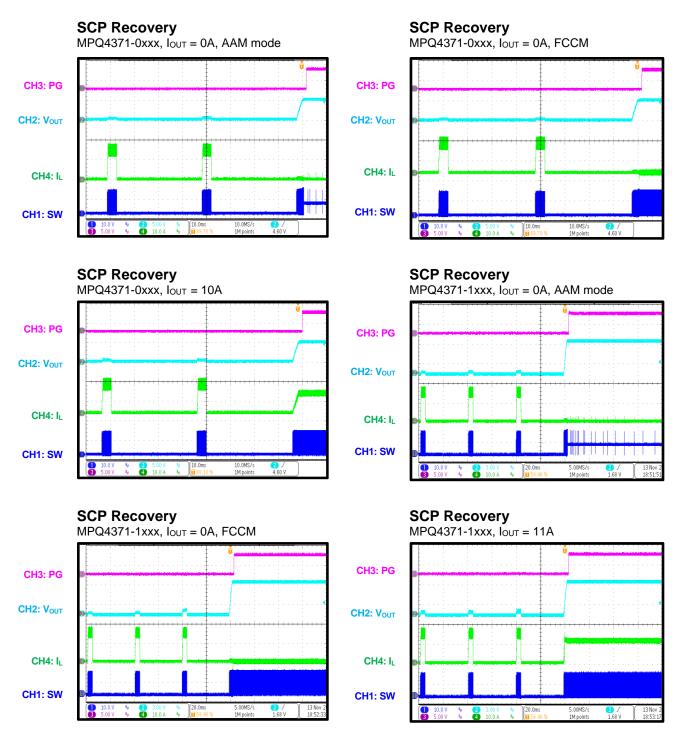

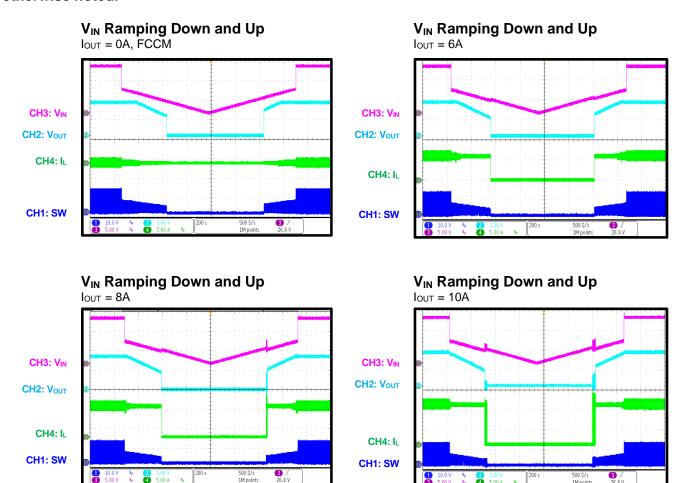

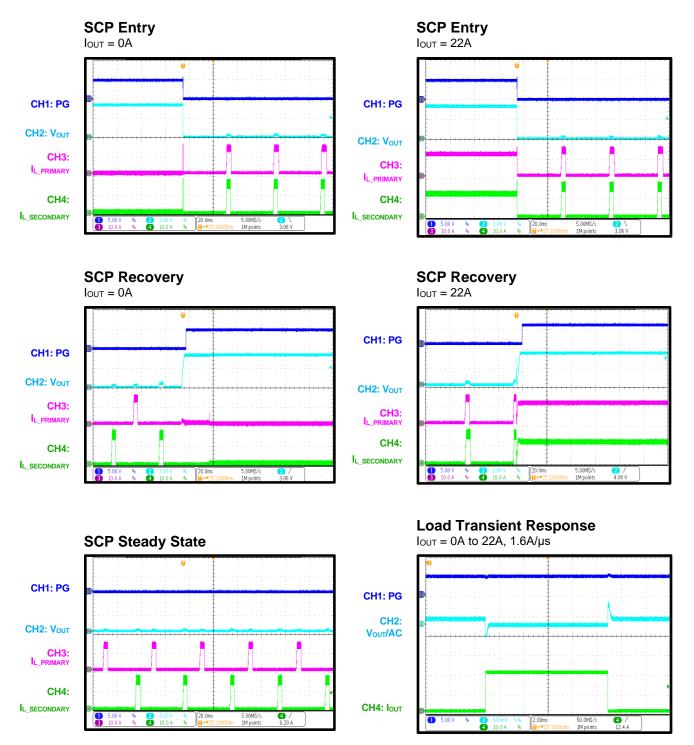

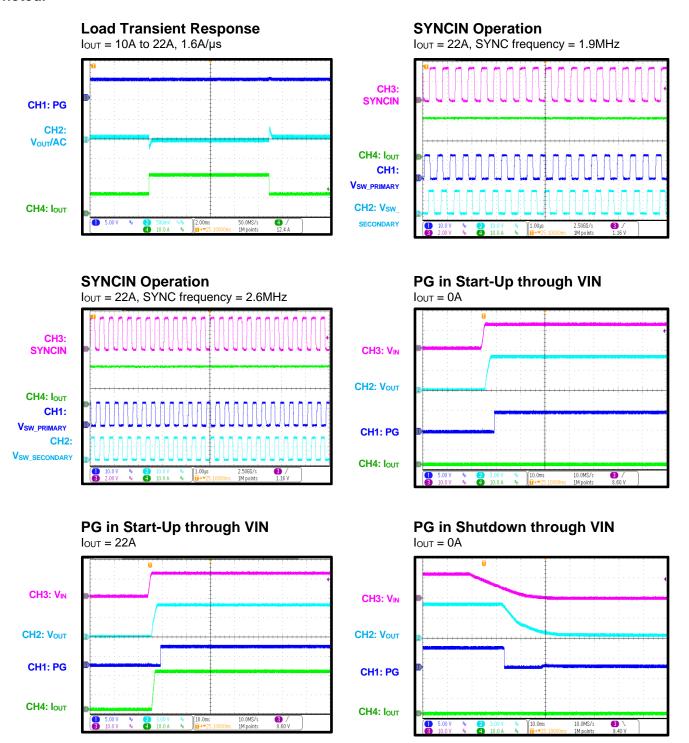

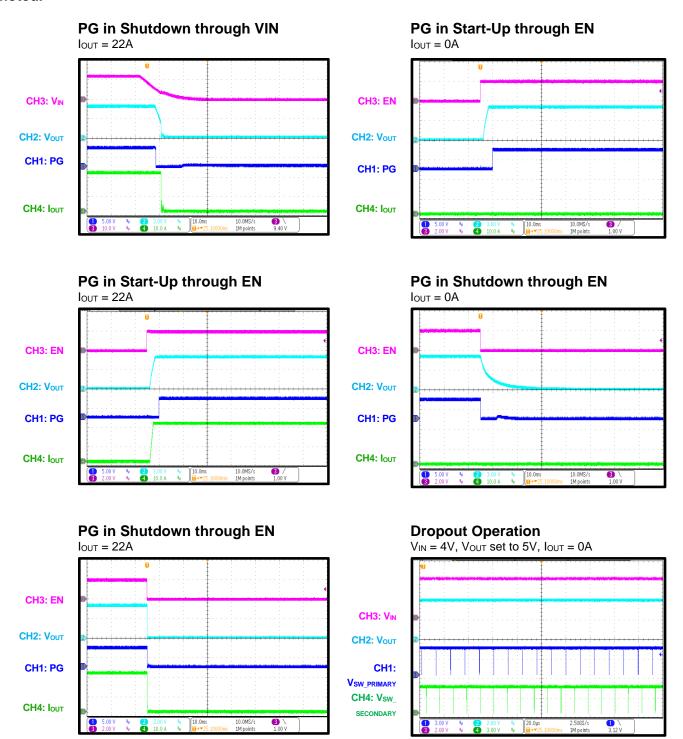

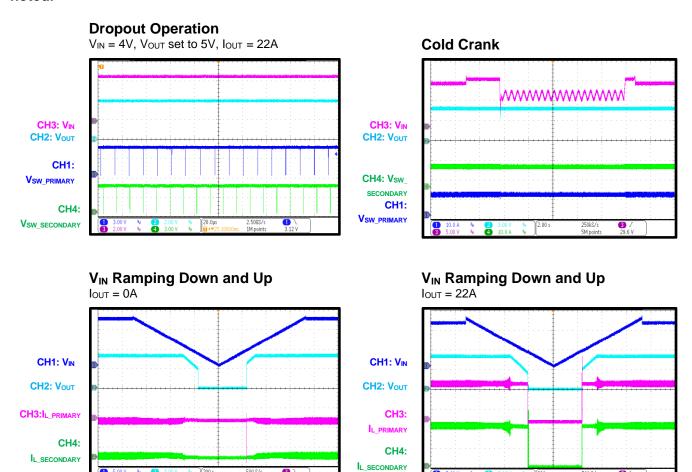

$V_{\text{IN}}$  = 12V,  $V_{\text{OUT}}$  = 5V, single-phase, L = 0.56 $\mu$ H,  $f_{\text{SW}}$  = 2.2MHz, AAM mode,  $T_{\text{A}}$  = 25°C, unless otherwise noted.

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

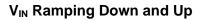

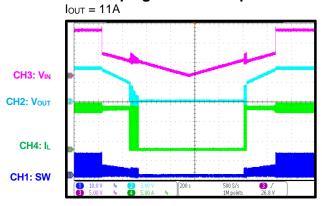

$V_{IN}$  = 12V,  $V_{OUT}$  = 5V, dual-phase, L = 0.56 $\mu$ H,  $f_{SW}$  = 2.2MHz, AAM mode,  $T_A$  = 25°C, unless otherwise noted.

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{\text{IN}}$  = 12V,  $V_{\text{OUT}}$  = 5V, dual-phase, L = 0.56 $\mu$ H,  $f_{\text{SW}}$  = 2.2MHz, AAM mode,  $T_{\text{A}}$  = 25°C, unless otherwise noted.

3 \ 7.20 A

### TYPICAL PERFORMANCE CHARACTERISTICS (continued)

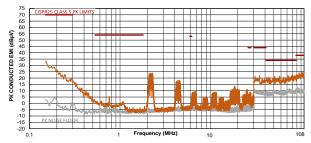

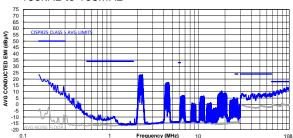

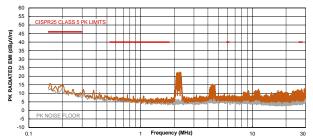

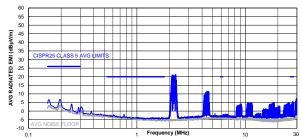

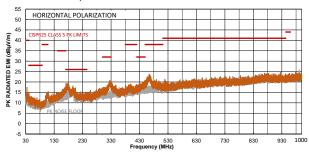

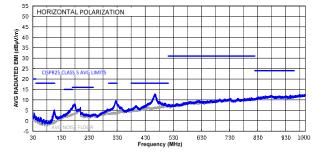

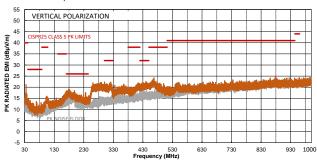

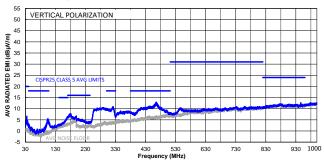

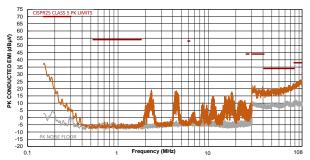

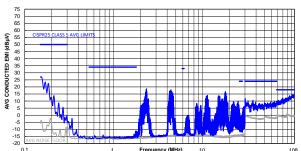

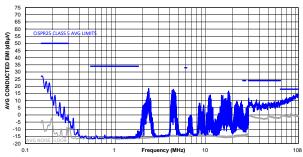

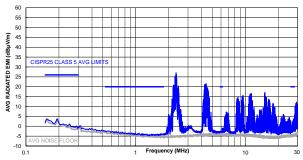

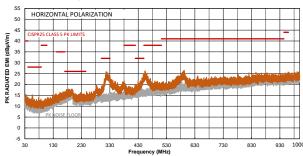

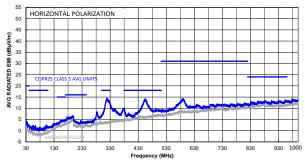

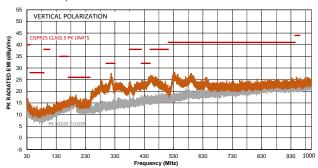

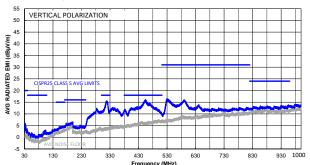

$V_{IN} = 12V$ ,  $V_{OUT} = 5V$ , single-phase,  $L = 0.56\mu H^{(12)}$ ,  $f_{SW} = 2.2MHz$ , AAM mode,  $T_A = 25^{\circ}C$ , unless otherwise noted. (13)

### **CISPR 25 Class 5 Peak Conducted Emissions**

150kHz to 108MHz

## **CISPR 25 Class 5 Average Conducted Emissions**

150kHz to 108MHz

#### **CISPR 25 Class 5 Peak Radiated Emissions**

150kHz to 30MHz

#### **CISPR25 Class 5 Average Radiated Emissions**

150kHz to 30MHz

### **CISPR 25 Class 5 Peak Radiated Emissions**

Horizontal, 30MHz to 1GHz

#### **CISPR 25 Class 5 Average Radiated Emissions**

Horizontal, 30MHz to 1GHz

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{IN}$  = 12V,  $V_{OUT}$  = 5V, single-phase, L = 0.56 $\mu$ H  $^{(12)}$ ,  $f_{SW}$  = 2.2MHz, AAM mode,  $T_A$  = 25°C, unless otherwise noted.  $^{(13)}$

### CISPR 25 Class 5 Peak Radiated Emissions

Vertical, 30MHz to 1GHz

## CISPR 25 Class 5 Average Radiated Emissions

Vertical, 30MHz to 1GHz

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{IN}$  = 12V,  $V_{OUT}$  = 5V, dual-phase, L = 0.56 $\mu$ H  $^{(12)}$ ,  $f_{SW}$  = 2.2MHz, AAM mode,  $T_A$  = 25°C, unless otherwise noted.  $^{(14)}$

# **CISPR 25 Class 5 Peak Conducted Emissions**

150kHz to 108MHz

# **CISPR 25 Class 5 Average Conducted Emissions**

150kHz to 108MHz

#### CISPR 25 Class 5 Peak Radiated Emissions

150kHz to 30MHz

## CISPR 25 Class 5 Average Radiated Emissions

150kHz to 30MHz

### CISPR 25 Class 5 Peak Radiated Emissions

Horizontal, 30MHz to 1GHz

# **CISPR 25 Class 5 Average Radiated Emissions**

Horizontal, 30MHz to 1GHz

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{IN}$  = 12V,  $V_{OUT}$  = 5V, dual-phase, L = 0.56 $\mu$ H  $^{(12)}$ ,  $f_{SW}$  = 2.2MHz, AAM mode,  $T_A$  = 25°C, unless otherwise noted.  $^{(14)}$

### CISPR 25 Class 5 Peak Radiated Emissions

Vertical, 30MHz to 1GHz

# **CISPR 25 Class 5 Average Radiated Emissions**

Vertical, 30MHz to 1GHz

#### Notes

- 12) Inductor part number: XEL6030-561MEB/C. DCR =  $3m\Omega$ .

- 13) The EMC test results are based on the application circuit with EMI filters (see Figure 19 on page 77).

- 14) The EMC test results are based on the application circuit with EMI filters (see Figure 23 on page 79).

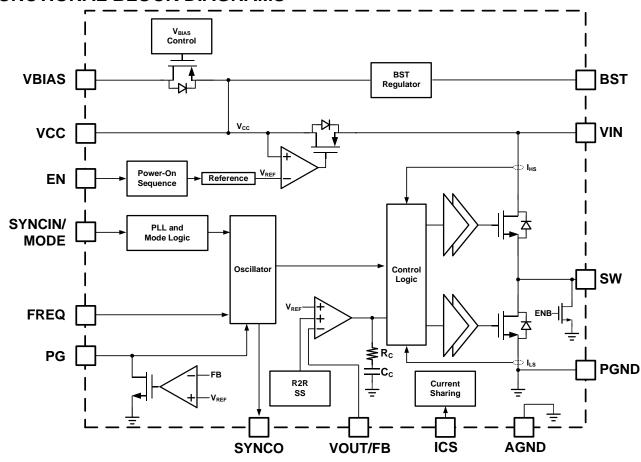

## **FUNCTIONAL BLOCK DIAGRAMS**

Figure 3: Functional Block Diagram for Adjustable-Output Version

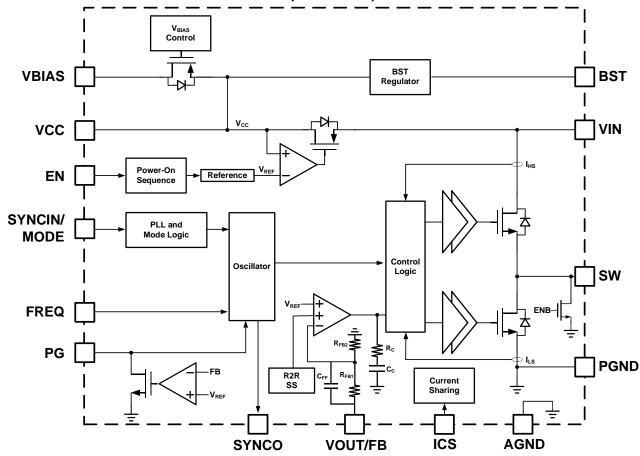

## **FUNCTIONAL BLOCK DIAGRAMS** (continued)

Figure 4: Functional Block Diagram for Fixed-Output Version

MPQ4371 - 36V, 6A TO 11A, ULTRA-LOW IQ, SYNC BUCK CONVERTER, AEC-Q100

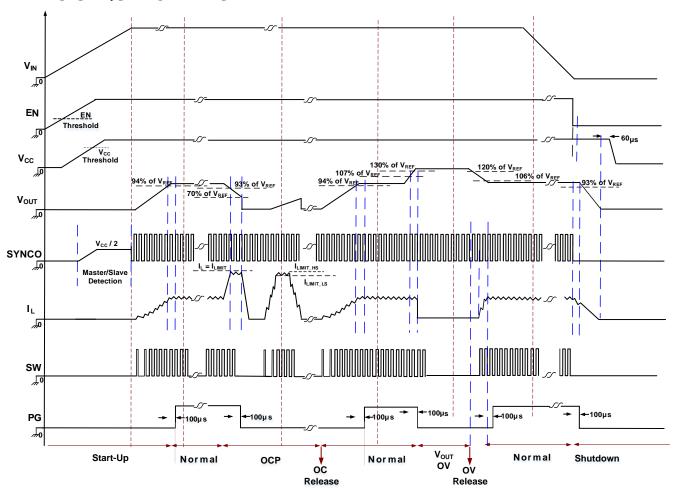

## **TIMING SEQUENCE DIAGRAM**

Figure 5: Timing Sequence Diagram

#### **OPERATION**

The MPQ4371 family of buck converters are configurable-frequency (200kHz to 2.5MHz), synchronous, step-down switching regulators with integrated low on resistance HS-FETs and LS-FETs. The family covers a 6A to 11A output current (I<sub>OUT</sub>) range and employs zero-delay pulse-width modulation (PWM) (ZDP<sup>TM</sup>) control, an MPS-exclusive technology that delivers fast transient response while reducing external capacitor count. In addition, it maintains the fixed f<sub>SW</sub>, and its low operational quiescent current makes this device well-suited for battery-powered applications.

#### Zero-Delay PWM (ZDP™) Control

Automotive applications generally require fixedfrequency operation to reduce EMI concerns, but with fixed-frequency traditional topologies control have major limitations. For example, voltage mode is difficult to compensate in automotive environments, while peak current mode control struggles to keep up with stringent modern system-on-chip (SoC) transient without excessive requirements output capacitance. With these requirements in mind, the MPQ4371 features fixed-frequency ZDP™

ZDP<sup>™</sup> control combines current information with the hysteretic-style output voltage control in a clocked system. This provides an optimal transient response while maintaining a high phase margin across a wide variety of operating conditions and external component values. This control maintains superior EMI performance. The improved transient response reduces output capacitor requirements and lowers system cost. Trailing edge modulation facilitates a narrow minimum on time for high conversion ratio applications.

At the beginning of the PWM cycle, the high-side MOSFET (HS-FET) turns off, and the low-side MOSFET (LS-FET) turns on immediately until the control signal reaches the COMP voltage (V<sub>COMP</sub>). The HS-FET remains off for at least 80ns at the beginning of the cycle.

#### **Light-Load Operation**

Under light-load conditions, the MPQ4371 can operate in two different operation modes by setting the state of the SYNCIN/MODE pin.

The MPQ4371 works in forced continuous conduction mode (FCCM) when SYNCIN/MODE pin is pulled above 1.4V or an external clock is used. In FCCM, the MPQ4371 works with a fixed frequency from the no-load to full-load range. The MPQ4371 has a reverse current limit to prevent the negative current from dropping too low and damaging the components. Once the negative inductor current reaches the reverse current limit, the HS-FET immediately turns on, and the LS-FET turns off. The advantages of FCCM are its constant frequency and lower output voltage ripple at light loads. FCCM also has a better response to sudden load changes.

The MPQ4371 works in advanced asynchronous modulation (AAM) mode when the SYNCIN/MODE pin is pulled below 0.4V. AAM mode cannot be entered until soft start has finished. AAM mode optimizes efficiency under light-load and no-load conditions.

In AAM mode, the LS-FET emulates a diode and the HS-FET has a fixed one-shot on-time to charge the inductor and regulate the output. As the load decreases, the interval between each one-shot increases. When this interval is longer than 8µs, the MPQ4371 enters sleep mode, which turns off some internal circuits and extends the on time to achieve an ultra-low quiescent current. When the load increases, and the interval becomes shorter than 6us. the device exits sleep mode and re-enters AAM mode. The part can exit AAM mode immediately if the SYNCIN/MODE pin goes high. If there is a fault (e.g. over-current, over-temperature), then the MPQ4371 does not disable the internal circuits in sleep mode.

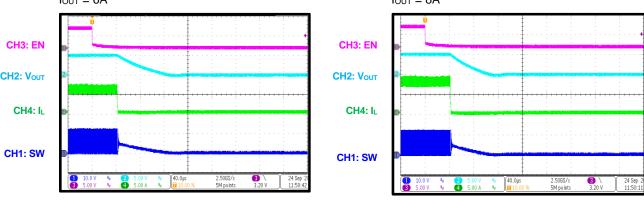

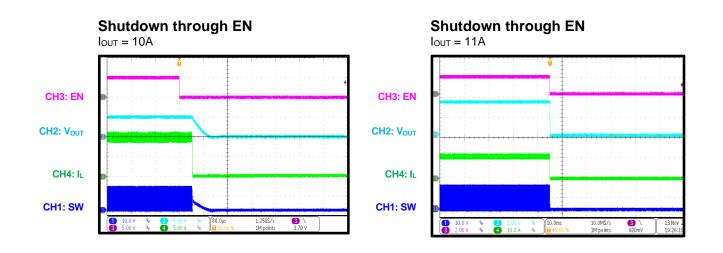

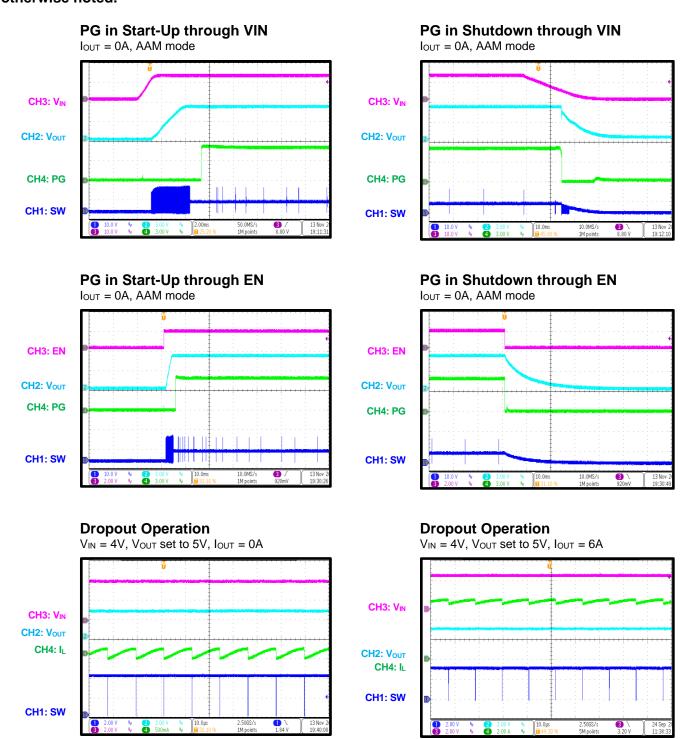

#### Start-Up and Shutdown

If both the input voltage  $(V_{IN})$  and EN exceed their appropriate thresholds, the chip starts. The reference block starts first, generating a stable reference voltage and currents, and then the internal regulator is enabled. The regulator provides a stable supply for the remaining circuitries.

While the internal supply rail is up, an internal timer holds the HS-FET and LS-FET off for about 100µs to blank the start-up glitches. When the

soft-start block is enabled, it first holds its softstart output low to ensure that the remaining circuits are ready, and then slowly ramps up.

Four events shut down the chip: EN going low,  $V_{\text{IN}}$  going low, thermal shutdown and  $V_{\text{IN}}$  overvoltage (OV) shutdown. In the shutdown procedure, the signaling path is blocked first to avoid any fault triggering, then  $V_{\text{COMP}}$  and the internal supply rail are pulled down. The floating driver is not subject to this shutdown command, but its charging path is disabled.

#### **Error Amplifier (EA)**

The error amplifier (EA) compares the FB pin's voltage ( $V_{FB}$ ) with the internal reference (0.6V). The output of the EA is then compared to  $V_{FB}$  again. The output of this comparator is compared to the current information to control the power MOSFET's duty cycle.

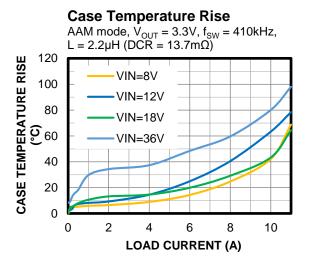

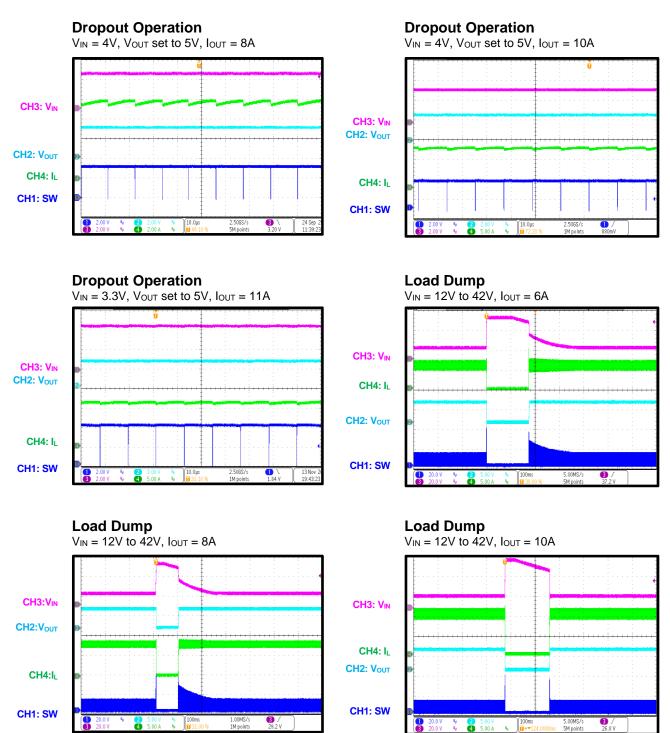

#### Low-Dropout (LDO) Mode

When  $V_{\text{IN}}$  drops close to the output voltage ( $V_{\text{OUT}}$ ) and the device detects the minimum off time (100ns) that the HS-FET is using, the MPQ4371 is in low-dropout mode. The MPQ4371 reduces  $f_{\text{SW}}$  to achieve a high duty cycle. When  $f_{\text{SW}}$  drops to about 100kHz, the minimum off time is about 50ns to achieve a higher duty cycle. During soft start, the MPQ4371 only enters low-dropout mode after 60% of the SS time has elapsed.

The effective duty cycle during the regulator's dropout period is mainly influenced by the voltage drop across the power MOSFET, the inductor's resistance, and the PCB resistance.

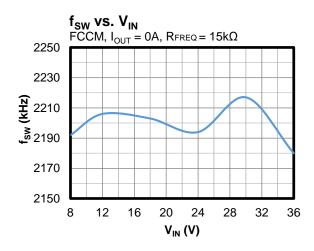

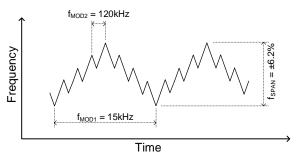

#### Frequency Spread Spectrum (FSS)

The MPQ4371 uses dual spread spectrum modulation. First, the MPQ4371 has a 15kHz modulating frequency ( $f_{\text{MOD1}}$ ) with  $\leq$ 128 steps and a triangular profile to spread the internal oscillator frequency across a  $\pm$ 6.2% window. The number of steps varies with the configured oscillator frequency so that the exact same  $f_{\text{SW}}$  steps cycle by cycle.

A second modulating frequency ( $f_{MOD2}$ ) of 120kHz varies the oscillator frequency across a  $\pm 2.5\%$  window with a maximum of 16 steps. This higher modulating frequency improves the effect of FSS across the high-frequency EMI measurements, where the resolution bandwidth (RBW) is 120kHz (see Figure 6).

Figure 6: FSS

The emission power of the fundamental  $f_{SW}$  and its harmonics is distributed into smaller pieces by creating side-bands when modulating  $f_{SW}$  with the triangle modulation waveform. This significantly reduces the amplitude of individual EMI spikes (also called spurs).

#### **Soft Start**

The MPQ4371 has an internal soft start implemented to prevent the converter's output voltage from overshooting during start-up. The default soft-start duration is 4ms.

#### Pre-Biased Start-Up

When the MPQ4371 starts up and  $V_{FB}$  is < 100% of its target, the MPQ4371 initiates soft start.

If  $V_{FB}$  is between 100% and 130% of its target at start-up while in FCCM, this means that the output has a pre-biased voltage. Neither the HS-FET nor LS-FET turn on until the internal soft start process is 80% complete. Then the MPQ4371 starts switching and regulates the output before soft start finishes.

If  $V_{FB}$  exceeds 130% of its target at start-up, the MPQ4371 start to slowly discharge the output through the discharging FET on SW. Once  $V_{FB}$  reaches 120% of its target, the MPQ4371 starts the internal soft start and operates following the pre-biased start-up process, as explained in the previous paragraph.

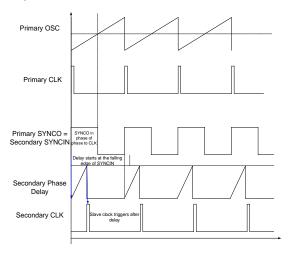

#### SYNCIN and SYNCO

$f_{\rm SW}$  can be synchronized to the rising edge of a clock signal applied at the SYNCIN/MODE pin. The recommended SYNCIN frequency range is between 200kHz and 2.5MHz. The SYNCIN frequency should be set to match the internal  $f_{\rm SW}$  with a  $\pm 10\%$  tolerance.

The SYNCO pin provides a clock signal that is in phase with the internal oscillator when there is no SYNCIN signal, or a clock signal in phase

with SYNCIN. Figure 7 shows when an external clock signal is applied at SYNCIN. This makes it simple to enable a dual-phase interleaving configuration.

Figure 7: SYNCIN and SYNCO Scheme

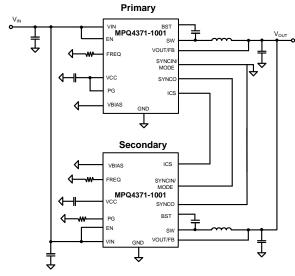

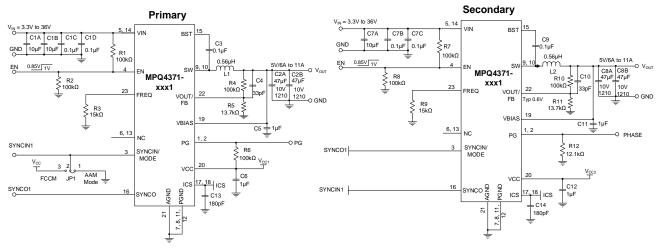

#### Primary/Secondary Selection and Multi-Phase Function

"Primary" and "secondary" are terms are used to describe the role of the different ICs in a multiphase power converter. The primary device generates a clock signal to which the secondary device is synchronized, and it also asserts PG based on the output regulation.

The device detects the SYNCO pin's status during start-up to configure the primary and secondary selection. If the chip detects a high impendence on the SYNCO pin, the device is configured to be a primary device. If the SYNCO pin is pulled high (connected to VCC or an external voltage) or low (connected to GND), the device is configured to be a secondary device.

To work in a multi-phase topology, The VOUT/FB pins of the devices must be connected together directly or through feedback resistors.

The ICS pins must be connected together, and a local, lower-value capacitor much be placed between each ICS pin and GND.

The primary device's SYNCO pin is connected to the SYNCIN/MODE pins of the secondary devices, which are interleaved. If the primary device's SYNCIN/MODE pin is used for mode selection, the secondary devices' SYNCO pins tied to the primary device's SYNCIN/MODE pin; pull SYNCIN/MODE low to select AAM mode, or pull it high for FCCM. If the primary device's SYNCIN/MODE pin is applied with the external clock signal to synchronize the internal oscillator frequency, the SYNCO pins of the secondary devices can only be pulled high or low, and they cannot be connected to the primary device's SYNCN/MODE pin. With multiphase applications, avoid floating the primary device's SYNCIN/MODE pin, or connect it to GND/VCC through a larger resistor (> $20k\Omega$ ).

Pull the PG pin to a power source through a resistor or leave it floating if it is not used for the primary device. For secondary devices, connect a resistor to ground on the PG pin to set the phase delay and allow for simple multi-phase operation; Connect PG directly to GND to select no delay on the SYNCIN signal for secondary phase.

Figure 8 shows a dual-phase configuration.

Figure 8: Dual-Phase Configuration

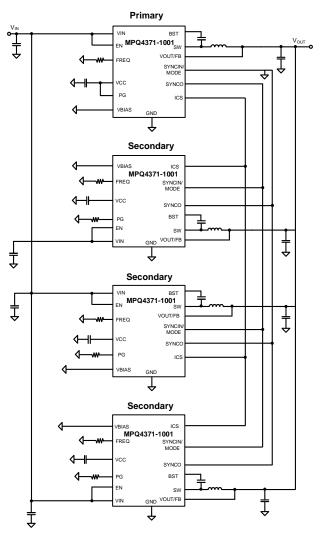

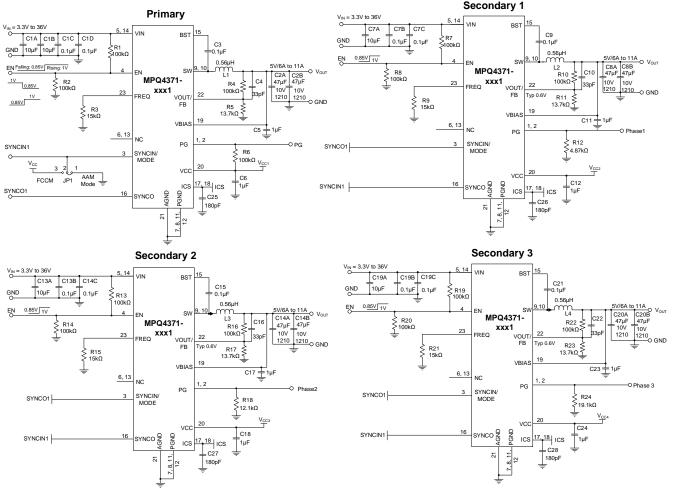

Figure 9 on page 67 shows a 4-phase configuration.

Figure 9: 4-Phase Configuration

For multi-phase applications, start with AAM mode then change to FCCM after the PG signal of the primary phase pulls high.

#### Thermal Shutdown

Thermal shutdown is implemented to prevent the chip from thermal runaway. When the silicon die temperature exceeds its upper threshold (180°C), the MPQ4371 shuts down the power MOSFETs. When the temperature falls below the lower threshold (150°C), thermal shutdown is removed, so the chip is enabled again.

#### **V<sub>IN</sub> Over-Voltage Protection (OVP)**

The MPQ4371 stops switching when  $V_{IN}$  exceeds its OV rising threshold (typically 38V). The device resumes normal regulation and switching when  $V_{IN}$  drops to its OV falling threshold (typically 37V).

If the MPQ4371 is operating in sleep mode, this OVP function is turned off between the noswitching periods. The  $V_{\text{IN}}$  OVP function only works during the one-shot HS on time and detects if  $V_{\text{IN}}$  reaches the OVP threshold.

#### **Peak and Valley Current Limit**

Both the HS-FET and LS-FET have cycle-by-cycle current-limit protection. When the inductor current ( $I_L$ ) reaches the high-side peak current limit (typically 17.2A for the MPQ4371-0xxx) while the HS-FET is on, the HS-FET is forced off immediately to prevent the current from rising further. If there is an internal clock signal before the peak current limit is reached, the HS-FET also turns off.

When the LS-FET is on, the next clock's rising edge is held until  $I_{\perp}$  drops below the low-side valley current limit (typically 12A for the MPQ4371-0xxx). Then  $I_{\perp}$  can drop to a sufficiently low value when the HS-FET turns on again. This current limit scheme prevents current runaway if an overload or short-circuit event occurs.

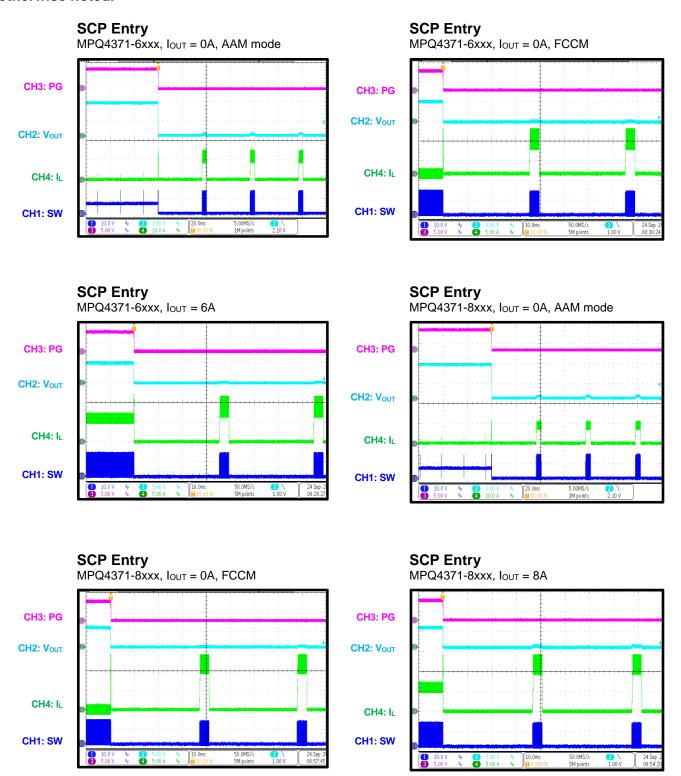

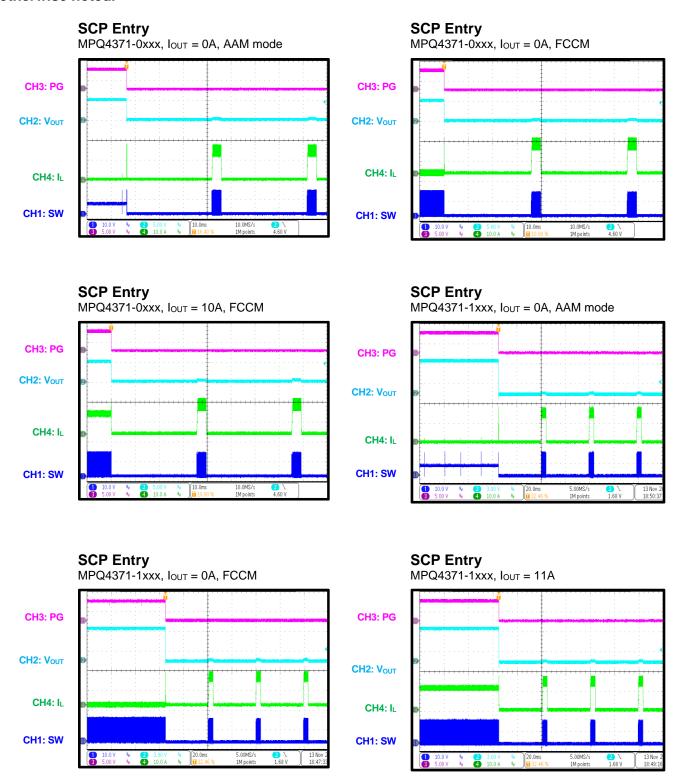

#### **Short-Circuit Protection (SCP)**

If  $V_{\text{OUT}}$  drops below 93% of its nominal output and the EA's output is clamped, the MPQ4371 counts the valley current limit counter (LSOC) about 128 times and enters hiccup mode.

If  $V_{\text{OUT}}$  drops below 70% of its nominal output, the MPQ4371 counts the LSOC about 8 times then enters hiccup mode. The device restarts with a full soft start after about 32ms. This hiccup process repeats until the fault is removed.

During the hiccup period, when  $V_{FB}$  reaches 80% of internal reference, the part considers the SCP recovery action. In this scenario, the device reinitiates a soft start, which can prevents large output voltage spikes if the MPQ4371 recovers during the SCP period.

# Output Over-Voltage Protection (OVP) and Discharge

If Vout exceeds 130% of its nominal regulation value in non-sleep mode (e.g. FCCM), the MPQ4371 stops switching. Then an internal discharge path from SW to GND is activated to discharge Vout. The discharge is disabled when Vout drops back to 120% of its nominal value, and the device resumes switching when Vout drops below the nominal output voltage.

#### MPQ4371 - 36V, 6A TO 11A, ULTRA-LOW Iq, SYNC BUCK CONVERTER, AEC-Q100

If the device is operating in a sleep mode, the output OVP function is turned off, and the PG rising and falling thresholds are used to detect OVP. The discharge circuit is activated if  $V_{\text{OUT}}$  is exceeds 107% of its normal regulation value, and discharging is disabled when  $V_{\text{OUT}}$  drops back to 106% of its nominal value. The MPQ4371 resumes switching when  $V_{\text{OUT}}$  drops below its nominal value.

If Vouτ exceeds 130% of its nominal regulation value in a non-sleep mode (e.g. AAM mode or DCM) within 160μs, the MPQ4371 follows the non-sleep mode (e.g. CCM) function.

If the period is longer than 160µs, the MPQ4371 enters sleep mode, and the OVP threshold becomes 107% or 106% of the nominal value, which same as sleep mode OVP function.

Not only does output OVP trigger the discharge function; the output discharge function is also activated during EN shutdown.

## **APPLICATION INFORMATION**

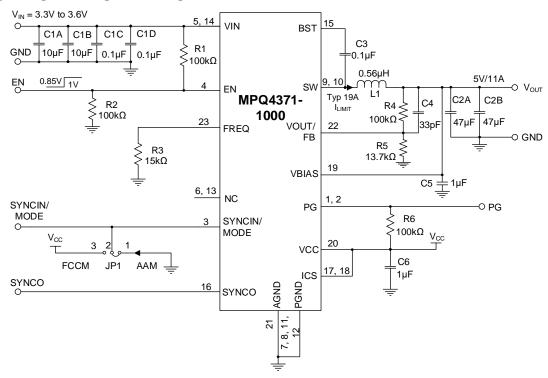

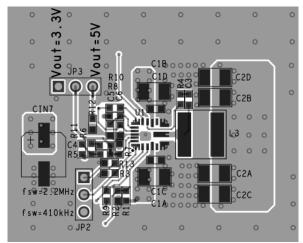

Figure 10: Typical Application Circuit for the MPQ4371-1000 (Vout = 5V, fsw = 2.2MHz)

**Table 1: Design Guide Index and Recommended Values**

| Table 1. Design Guide mack and Neconmiciaed Values |             |                       |                                                                  |                               |  |

|----------------------------------------------------|-------------|-----------------------|------------------------------------------------------------------|-------------------------------|--|

| Pin#                                               | Pin name    | Component             | Design Guide Index                                               | Value                         |  |

| 1, 2                                               | PG          | R6                    | Power Good (PG) Indication or Phase Shift Setting (PG, Pins 1–2) | 100kΩ                         |  |

| 3                                                  | SYNCIN/MODE | -                     | Sync Input and MODE Selection (SYNCIN/MODE, Pin 3)               | -                             |  |

| 4                                                  | EN          | R1, R2                | Enable and VIN Under-Voltage Lockout (UVLO) (EN, Pin 4)          | 100kΩ,100kΩ                   |  |

| 5, 14                                              | VIN         | C1A, C1B,<br>C1C, C1D | Selecting the Input Capacitors (VIN, Pins 5 and 14)              | 10μF,<br>10μF,0.1μF,<br>0.1μF |  |

| 6, 13                                              | NC          | N/A                   | N/A                                                              | -                             |  |

| 7, 8,<br>11, 12                                    | PGND        | -                     | GND Connection (PGND, Pins 7–8 and Pins 11–12; AGND, Pin 21)     | -                             |  |

| 9, 10                                              | SW          | L1, C2A,<br>C2B       | Selecting the Inductor and Output Capacitors (SW, Pins 9–10)     | 0.56μH,47μF,<br>47μF          |  |

| 15                                                 | BST         | C3                    | Floating Driver and Bootstrap Charging (BST, Pin 15)             | 0.1µF                         |  |

| 16                                                 | SYNCO       | -                     | Sync Output (SYNCO, Pin 16)                                      | -                             |  |

| 17, 18                                             | ICS         | -                     | Current Sharing (ICS, Pins 17–18)                                | -                             |  |

| 19                                                 | VBIAS       | C5                    | Internal LDO Supply (VBIAS, Pin 19)                              | 1µF                           |  |

| 20                                                 | VCC         | C6                    | Internal LDO Supply (VCC, Pin 20)                                | 1µF                           |  |

| 21                                                 | AGND        | -                     | GND Connection (PGND, Pins 7–8 and Pins 11–12; AGND, Pin 21)     | -                             |  |

| 22                                                 | VOUT/FB     | R4, R5, C4            | Setting the Feedback (VOUT/FB, Pin 22)                           | 100kΩ,<br>13.7kΩ, 33pF        |  |

| 23                                                 | FREQ        | R3                    | Setting the Switching Frequency (fsw) (FREQ, Pin 23)             | 15kΩ                          |  |

## Power Good (PG) Indication or Phase Shift Setting (PG, Pins 1–2)

For single-phase applications and for the primary device in multi-phase applications, the PG resistance ( $R_{PG}$ , also R6) is recommended to be about  $100k\Omega.$  The MPQ4371 has an open-drain PG output that indicates whether the regulator output is within its specific nominal output window. If using PG, connect it to a logic high level power source (e.g. 3.3V) via a pull-up resistor. PG goes high if  $V_{\text{OUT}}$  is within 94% to 106% of the nominal voltage; PG goes low if  $V_{\text{OUT}}$  exceeds 107% or falls below 93% of the nominal voltage. Float PG if it is not used.

For secondary devices in multi-phase applications, this pin can set the phase shift by connecting a resistor (R<sub>PHASE</sub>) to ground. Table 2 shows the relationship between the phase shift and R<sub>PHASE</sub> under high- and low-frequency conditions.

Table 2: Phase Shift vs. RPHASE

| Phase RPHASE at Shift fsw_PRIMARY = 410kHz |        | RPHASE at fsw_PRIMARY = 2.2MHz |  |

|--------------------------------------------|--------|--------------------------------|--|

| 90°                                        | 33kΩ   | 4.87kΩ                         |  |

| 120°                                       | 46.4kΩ | 7.32kΩ                         |  |

| 180°                                       | 73.2kΩ | 12.1kΩ                         |  |

| 240°                                       | 97.6kΩ | 16.9kΩ                         |  |

| 270°                                       | 115kΩ  | 19.1kΩ                         |  |

| 359°                                       | 150kΩ  | 26.1kΩ                         |  |

# Sync Input and MODE Selection (SYNCIN/MODE, Pin 3)

For single-phase applications and primary devices in multi-phase applications, when this pin is used as the sync input pin,  $f_{SW}$  can be synchronized to the rising edge of a clock signal applied at the SYNCIN/MODE pin. The recommended SYNCIN frequency range is between 90% and 110% of the set  $f_{SW}$ . When this pin is used for mode selection, pull this pin high so that the MPQ4371 operates in FCCM; pull this pin low or float this pin for AAM mode. Table 3 shows the detailed mode selection.

**Table 3: Mode Selection**

| SYNCIN/MODE Input | Operation |

|-------------------|-----------|

| Floating          | AAM mode  |

| <0.4V             | AAM mode  |

| >1.4V             | FCCM      |

| External clock in | FCCM      |

For secondary devices in multi-phase applications, it is recommended to connect the SYNCIN/MODE pin of the secondary devices to the primary device's SYNCO pin. In this scenario, keep the primary device's SYNCO pin at a high impedance.

## Enable and $V_{IN}$ Under-Voltage Lockout (EN, Pin 4)

EN is a digital control pin that turns the regulator on and off.

# Enabled by External Logic High/Low (H/L) Signal

When the EN voltage reaches about 0.7V, the VCC supply turns on. When  $V_{\text{IN}}$  exceeds about 2.7V, then  $V_{\text{IN}}$  provides an accurate reference voltage for the EN threshold. Forcing EN to exceed its rising threshold voltage of 1V turns on the device. The device is turned off by driving EN below 0.85V.

### Configurable V<sub>IN</sub> UVLO

When  $V_{\text{IN}}$  is sufficiently high, the chip can be enabled and disabled by the EN pin. The EN pin can generate a configurable  $V_{\text{IN}}$  UVLO threshold and hysteresis.

The MPQ4371 has an internal, fixed UVLO threshold. The rising threshold is 3.8V, while the falling threshold is about 2.9V. For applications that need a higher UVLO point, an external resistor divider can be placed between VIN and EN to achieve a higher equivalent UVLO threshold (see Figure 11).

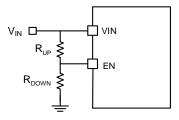

Figure 11: Adjustable UVLO Using EN Divider

The UVLO rising and falling thresholds can be calculated with Equation (1) and Equation (2), respectively:

$$VIN_{UV\_RISING} = \left(1 + \frac{R_{UP}}{R_{DOWN}}\right) \times V_{EN\_RISING}$$

(1)

$$VIN_{UV\_FALLING} = (1 + \frac{R_{UP}}{R_{DOWN}}) \times V_{EN\_FALLING}$$

(2)

Where  $V_{EN\ RISING}$  is 1V, and  $V_{EN\ FALLING}$  is 0.85V.

# Selecting the Input Capacitors (VIN, Pins 5 and 14)

The step-down converters have a discontinuous input current, and require a capacitor to supply AC current to the converters while maintaining the DC input voltage. For the best performance, use low-ESR capacitors. Ceramic capacitors with X5R or X7R dielectrics are highly recommended because of their low ESR and small temperature coefficients.

For most applications, use a  $4.7\mu\text{F}$  to  $10\mu\text{F}$  capacitor. It is strongly recommended to use another, lower-value capacitor (e.g.  $0.1\mu\text{F}$ ) with a small package size (0603) to absorb high-frequency switching noise. Place this capacitor as close to VIN and GND as possible.

Since  $C_{IN}$  absorbs the input switching current, it requires an adequate ripple current rating. The RMS current in the input capacitor can be estimated with Equation (3):

$$I_{CIN} = I_{LOAD} \times \sqrt{\frac{V_{OUT}}{V_{IN}} \times (1 - \frac{V_{OUT}}{V_{IN}})}$$

(3)

The worst-case condition occurs at  $V_{IN} = 2 \text{ x}$   $V_{OUT}$ , calculated with Equation (4):

$$I_{CIN} = \frac{I_{LOAD}}{2} \tag{4}$$

For simplification, choose an input capacitor with an RMS current rating greater than half of the maximum load current.

The input capacitor can be electrolytic, tantalum, or ceramic. When using electrolytic or tantalum capacitors, add a small, high-quality ceramic capacitor (e.g. 0.1µF) as close to the IC as possible. When using ceramic capacitors, ensure that they have enough capacitance to provide a sufficient charge to prevent excessive voltage ripple at the input. The input voltage ripple caused by the capacitance can be estimated with Equation (5):

$$\Delta V_{IN} = \frac{I_{LOAD}}{f_{SW} \times C_{IN}} \times \frac{V_{OUT}}{V_{IN}} \times (1 - \frac{V_{OUT}}{V_{IN}}) \tag{5}$$

# Selecting the Inductor and Output Capacitors (SW, Pins 9–10)

#### Selecting the Inductor

A 0.1µH to 10µH inductor with a DC current rating at least 25% higher than the maximum load current is recommended for most applications. For higher efficiency, choose an inductor with a lower DC resistance. A larger-value inductor results in less ripple current and a lower output voltage ripple, but also has a larger physical size, higher series resistance, and lower saturation current. A good rule to determine the inductance is to allow the inductor ripple current to be approximately 30% of the maximum load current. The inductance can be calculated with Equation (6):

$$L = \frac{V_{OUT}}{f_{sw} x \Delta I_L} x (1 - \frac{V_{OUT}}{V_{IN}})$$

(6)

Where  $\Delta I_{L}$  is the peak-to-peak inductor ripple current.