# NTP53x2

# NTAG 5 link - NFC Forum-compliant I<sup>2</sup>C bridge

Rev. 3.1 — 24 March 2020 544531

Product data sheet COMPANY PUBLIC

# 1 General description

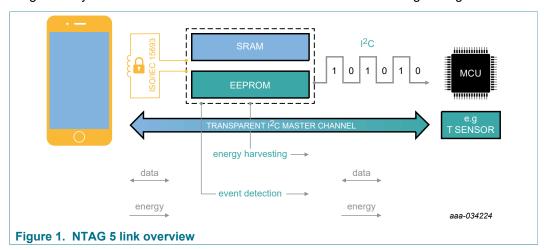

Optimized for sensor-driven applications, this highly integrated NFC IC creates a secure, standard-based link from the device to the cloud, in a future proof way to address and even power sensors.

NTAG 5 link is available in two different variants (see <u>Section 4</u>). NTP5332 supports all features of NTP5312, and on top of these, it offers also I<sup>2</sup>C master features, as well as AES mutual authentication.

NXP's NTAG 5 link lets designers of sensor-equipped systems add an NFC interface with a wired host interface that's configurable as an I<sup>2</sup>C master/slave, a pulse width modulator (PWM), or a general-purpose I/O (GPIO). Operating at 13.56 MHz, it is an NFC Forum-compliant Type 5 Tag (customer development board is NFC Forum certified - Certification ID: 58626) that can be read and written by an NFC-enabled device at close range and by an ISO/IEC 15693-enabled industrial reader over a longer range.

The NTAG 5 link can act as a direct bridge between an NFC-enabled device and any I<sup>2</sup>C slave, such as a sensor or external memory. This is especially useful in environments that require zero-power, single-shot measurements.

With NTAG 5 link, the device can connect to the cloud with a single tap. The connection uses an NFC Forum-compliant data exchange mechanism involving SRAM to ensure highly interoperable data transfers.

Support for ISO/IEC 15693 lets the NTAG 5 link communicate securely in two ways: with powerful industrial readers, at a range of up to 60 cm and with NFC-enabled devices in proximity range. This duality makes it possible for the device to be calibrated and parameterized automatically while in the factory and then, when put to be used in the field, safely communicate with contactless devices such as mobile phones.

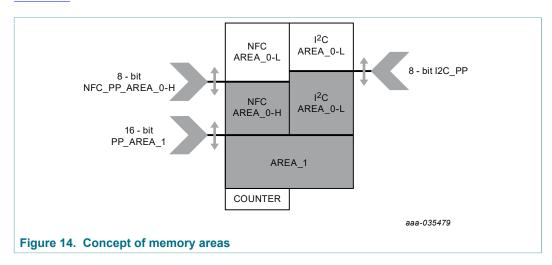

NTAG 5 link offers 2048 bytes (16384 bits) bytes of memory which can be divided into three areas, and each area can use a different protection level, varying from no

# NTAG 5 link - NFC Forum-compliant I<sup>2</sup>C bridge

protection to 32-/64-bit password-protected read/write access or up to 128-bit-AES mutual authentication protected read/write access.

The NTAG 5 link comes with pre-programmed proof-of-origin functionality to verify authenticity. The ECC-based originality signature can be reprogrammed or locked by the customer.

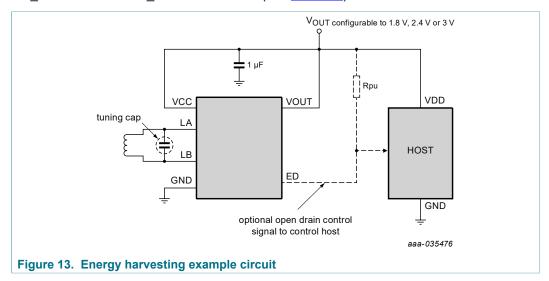

The NTAG 5 link can operate without a battery by drawing power from the NFC reader instead. It supports energy harvesting, which means it can be used to supply power to other components in the system. When sufficient energy is available, NTAG 5 link can supply a fixed, configurable voltage level to ensure a stable overall system.

## NTAG 5 link - NFC Forum-compliant I<sup>2</sup>C bridge

#### 2 Features and benefits

- Reading distance with long-range reader > 60 cm (> 25 inches)

- Zero-power readout of an I<sup>2</sup>C sensor

- Adjustable security levels up to mutual AES authentication (NTP5332 only)

- Flexible split between three open and/or protected memory areas

- Ensured authenticity of product through value chain

- Interoperable data exchange according to NFC Forum standards

- · Energy-efficient design with reduced bill of material

- Interoperable and high performance NFC interface

- ISO/IEC 15693 and NFC Forum Type 5 Tag compliant

- 64-bit Unique IDentifier

- Reliable and robust memory

- 2048 bytes (16384 bits) user EEPROM on top of configuration memory

- 256 bytes (2048 bits) SRAM for frequently changing data and pass-through mode

- 40 years data retention

- Write endurance of 1 000 000 cycles

- · Configurable contact interface

- <u>l<sup>2</sup>C slave</u> standard (100 kHz) and fast (400 kHz) mode

- NTP5332 offers a Transparent I<sup>2</sup>C master channel (for example, read sensors without an MCU)

- One configurable event detection pin

- Two GPIOs as multiplexed I<sup>2</sup>C lines

- Two Pulse Width Modulation (PWM) channels as multiplexed GPIOs and/or ED pin

- 1.62 V to 5.5 V supply voltage

- · Scalable security for access and data protection

- Disable NFC interface temporarily

- Disable I<sup>2</sup>C interface temporarily

- NFC PRIVACY mode

- Read-only protection as defined in NFC Forum Type 5 Tag Specification

- Full, read-only, or no memory access based on 32-bit password from both interfaces

- Optional 64-bit password protection from NFC perspective

- 128-bit AES authentication as defined in ISO/IEC 15693 for NTP5332

- ECC-based reprogrammable originality signature

- Multiple fast data transfer mode

- Pass-through mode with 256 byte SRAM buffer

- Standardized data transfer mode (PHDC, TNEP)

- · Low-power budget application support

- Energy harvesting with configurable output voltage up to 30 mW

- Low-power standby current typically <6 μA</li>

- Hard power down current typically <0.25 μA</li>

- Very robust architecture

- -40 °C to 85°C

- Extensive product support package

- Feature specific application notes

- Development board including software and source code

- Hands-on training

# NTAG 5 link - NFC Forum-compliant I<sup>2</sup>C bridge

# 3 Applications

- Use cases

- Simple dynamic secure pairing

- Commissioning

- Parameterization

- Diagnosis

- Firmware download

- Low BoM and low-power data acquisition for sensors

- Calibration

- Trimming

- Authenticity check and data protection

- Late "in the box" configuration

- LED driver configuration

- NFC charging

- Applications

- Lighting

- Smart home

- Hearable and Wearable

- Consumer

- Industrial

- Gaming

- Smart sensor

- Smart metering

# NTAG 5 link - NFC Forum-compliant I<sup>2</sup>C bridge

# 4 Ordering information

**Table 1. Ordering information**

| Orderable part | Package |                                                                                                                                                                                                          |           |

|----------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| number         | Name    | Description                                                                                                                                                                                              | Version   |

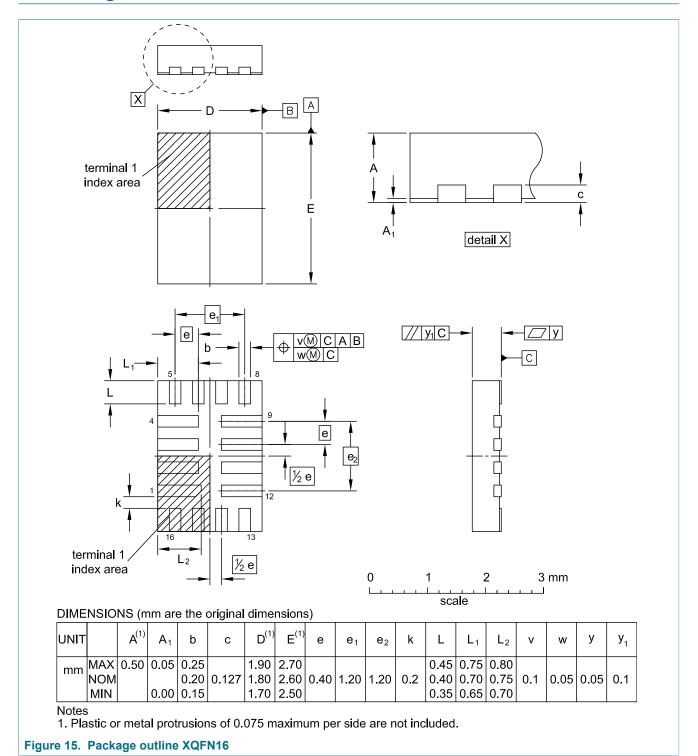

| NTP53121G0JHKZ | XQFN16  | NTAG 5 link; with I <sup>2</sup> C interface and 2048 bytes user EEPROM plastic, extremely thin quad flat package; no leads; 16 terminals                                                                | SOT1161-2 |

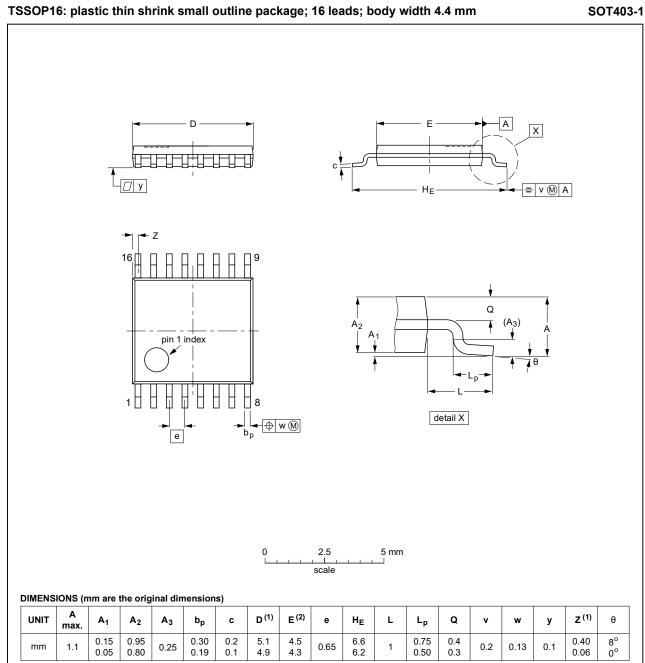

| NTP53121G0JTTZ | TSSOP16 | NTAG 5 link; with I <sup>2</sup> C interface and 2048 bytes user EEPROM plastic, thin shrink small outline package; 16 leads; 0.65 mm pitch; 5 mm x 4.4 mm x 1.1 mm body                                 | SOT403-1  |

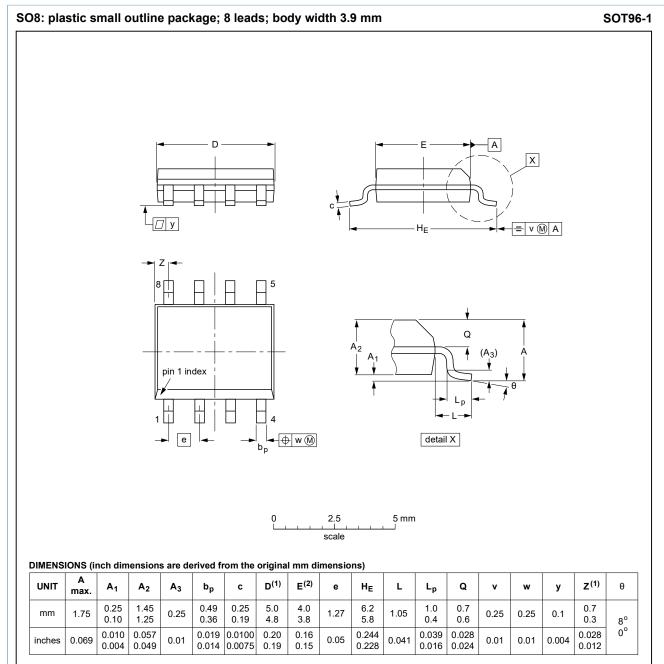

| NTP53121G0JTZ  | SO8     | NTAG 5 link; with I <sup>2</sup> C interface and 2048 bytes user EEPROM plastic, small outline package; 8 leads; 1.27 mm pitch; 4.9 mm x 3.9 mm x 1.75 mm body                                           | SOT96-1   |

| NTP53121G0FUAV | Wafer   | NTAG 5 link; 8 inch wafer, 150 µm thickness, on film frame carrier, electronic fail die marking according to SECS-II format)                                                                             | -         |

| NTP53321G0JHKZ | XQFN16  | NTAG 5 link with I <sup>2</sup> C master/slave interface, AES authentication and 2048 bytes user EEPROM plastic, extremely thin quad flat package; no leads; 16 terminals                                | SOT1161-2 |

| NTP53321G0JTTZ | TSSOP16 | NTAG 5 link with I <sup>2</sup> C master/slave interface, AES authentication and 2048 bytes user EEPROM plastic, thin shrink small outline package; 16 leads; 0.65 mm pitch; 5 mm x 4.4 mm x 1.1 mm body | SOT403-1  |

| NTP53321G0JTZ  | SO8     | NTAG 5 link with I <sup>2</sup> C master/slave interface, AES authentication and 2048 bytes user EEPROM plastic, small outline package; 8 leads; 1.27 mm pitch; 4.9 mm x 3.9 mm x 1.75 mm body           | SOT96-1   |

| NTP53321G0FUAV | Wafer   | NTAG 5 link; 8 inch wafer, 150 $\mu m$ thickness, on film frame carrier, electronic fail die marking according to SECS-II format)                                                                        | -         |

**REMARK:** Wafer specification addendum is available after exchange of a non-disclosure agreement (NDA)

# NTAG 5 link - NFC Forum-compliant I<sup>2</sup>C bridge

# 5 Marking

Table 2. Marking codes

| Type number   |         | Marking code |        |        |  |  |  |

|---------------|---------|--------------|--------|--------|--|--|--|

|               | Line A  | Line B       | Line C | Line D |  |  |  |

| NTP53121G0JHK | I21     | DBSN ASID    | DYWW   | -      |  |  |  |

| NTP53121G0JTT | NP53121 | DBID ASID    | ZnDYY  | WW     |  |  |  |

| NTP53121G0JT  | NP53121 | DBSN ASID    | nDYWW  | -      |  |  |  |

| NTP53321G0JHK | D21     | DBSN ASID    | DYWW   | -      |  |  |  |

| NTP53321G0JTT | NP53321 | DBID ASID    | ZnDYY  | WW     |  |  |  |

| NTP53321G0JT  | NP53321 | DBSN ASID    | nDYWW  | -      |  |  |  |

Used abbreviations:

ASID: Assembly Sequence ID

D: RHF-2006 indicator

DBID: Diffusion Batch ID

DBSN: Diffusion Batch Sequence Number

n: Assembly Centre Code

WW: week

Y or YY: year

Z: Diffusion Centre Code

# NTAG 5 link - NFC Forum-compliant I<sup>2</sup>C bridge

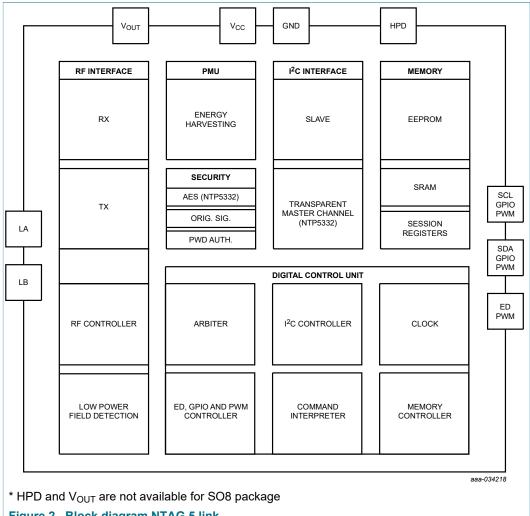

#### **Block diagram** 6

Figure 2. Block diagram NTAG 5 link

# NTAG 5 link - NFC Forum-compliant I<sup>2</sup>C bridge

# 7 Pinning Information

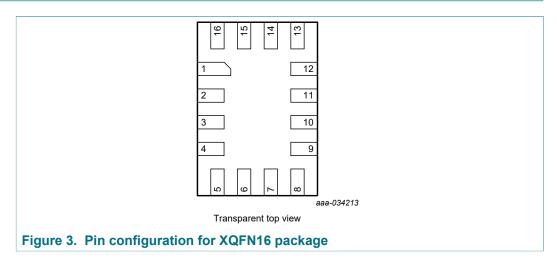

Table 3. Pin description for XQFN16

| Pin | Symbol           | Description                                               | When unused    |

|-----|------------------|-----------------------------------------------------------|----------------|

| 1   | GND              | Ground                                                    | connect to GND |

| 2   | GND              | Ground                                                    | connect to GND |

| 3   | N.C.             | not connected                                             | keep floating  |

| 4   | N.C.             | not connected                                             | keep floating  |

| 5   | N.C.             | not connected                                             | keep floating  |

| 6   | SDA/GPIO1/PWM1   | Multiplexed serial data I <sup>2</sup> C, GPIO1 and PWM1  | keep floating  |

| 7   | SCL/GPIO0/PWM0   | Multiplexed serial clock I <sup>2</sup> C, GPIO0 and PWM0 | keep floating  |

| 8   | ED/PWM0          | Multiplexed event detection and PWM0                      | keep floating  |

| 9   | V <sub>CC</sub>  | External power supply                                     | keep floating  |

| 10  | HPD              | Hard power down                                           | keep floating  |

| 11  | GND              | Ground                                                    | connect to GND |

| 12  | V <sub>OUT</sub> | Energy harvesting voltage output                          | keep floating  |

| 13  | N.C.             | not connected                                             | keep floating  |

| 14  | LB               | Antenna connection                                        | keep floating  |

| 15  | LA               | Antenna connection                                        | keep floating  |

| 16  | N.C.             | not connected                                             | keep floating  |

# NTAG 5 link - NFC Forum-compliant I<sup>2</sup>C bridge

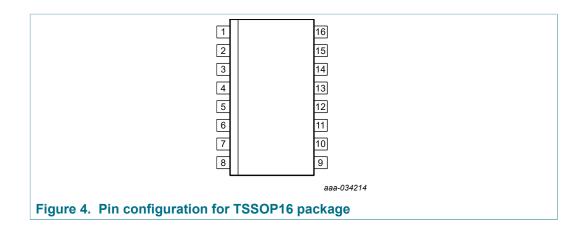

Table 4. Pin description for TSSOP16

| Pin | Symbol           | Description                                               | When unused    |

|-----|------------------|-----------------------------------------------------------|----------------|

| 1   | LA               | Antenna connection                                        | keep floating  |

| 2   | N.C.             | not connected                                             | keep floating  |

| 3   | GND              | Ground                                                    | connect to GND |

| 4   | GND              | Ground                                                    | connect to GND |

| 5   | N.C.             | not connected                                             | keep floating  |

| 6   | N.C.             | not connected                                             | keep floating  |

| 7   | N.C.             | not connected                                             | keep floating  |

| 8   | SDA/GPIO1/PWM1   | Multiplexed serial data I <sup>2</sup> C, GPIO1 and PWM1  | keep floating  |

| 9   | SCL/GPIO0/PWM0   | Multiplexed serial clock I <sup>2</sup> C, GPIO0 and PWM0 | keep floating  |

| 10  | ED/PWM0          | Multiplexed event detection and PWM0                      | keep floating  |

| 11  | V <sub>CC</sub>  | External power supply                                     | keep floating  |

| 12  | HPD              | Hard power down                                           | keep floating  |

| 13  | GND              | Ground                                                    | connect to GND |

| 14  | V <sub>OUT</sub> | Energy harvesting voltage output                          | keep floating  |

| 15  | N.C.             | not connected                                             | keep floating  |

| 16  | LB               | Antenna connection                                        | keep floating  |

# NTAG 5 link - NFC Forum-compliant I<sup>2</sup>C bridge

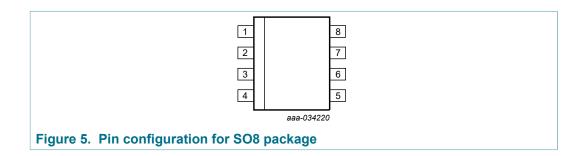

#### Table 5. Pin description for SO8

| Pin | Symbol          | Description                          | When unused    |

|-----|-----------------|--------------------------------------|----------------|

| 1   | GND             | Ground                               | connect to GND |

| 2   | LA              | Antenna connection                   | keep floating  |

| 3   | LB              | Antenna connection                   | keep floating  |

| 4   | GND             | Ground                               | connect to GND |

| 5   | SDA/GPIO1/PWM1  | Multiplexed GPIO1 and PWM1           | keep floating  |

| 6   | SCL/GPIO0/PWM0  | Multiplexed GPIO0 and PWM0           | keep floating  |

| 7   | ED/PWM0         | Multiplexed event detection and PWM0 | keep floating  |

| 8   | V <sub>CC</sub> | External power supply                | keep floating  |

## NTAG 5 link - NFC Forum-compliant I<sup>2</sup>C bridge

# 8 Functional description

#### 8.1 Memory Organization

#### 8.1.1 General

The entire memory is divided into three different parts:

- · User memory

- This part of the memory is intended to be used to store user data. It is organized in blocks of 4 bytes each (see <u>Section 8.1.2</u>).

- According to NFC Forum Type 5 Tag Specification, EEPROM block 0 contains the Capability Container directly followed by the NDEF Message TLV. If NTAG 5 link is used in a proprietary way, any user data may be stored in the user memory. Direct read/write access with the standard READ BLOCK and WRITE BLOCK commands (see <u>Section 8.2.3.5</u>) to this part of the memory is possible depending on the related security and write protection conditions.

- 16-bit counter The last block of the EEPROM memory from NFC perspective contains the 16-bit counter and the counter protection flag (see <u>Section 8.1.2.1</u>). This counter is not accessible from I<sup>2</sup>C perspective.

- · Configuration area

- Within this part of the memory all configuration options are stored (see <u>Section 8.1.3</u>).

This memory area can only be accessed with the READ CONFIG (see <u>Section 8.2.3.2.1</u>) or WRITE CONFIG (see <u>Section 8.2.3.2.2</u>) commands from NFC perspective. From I<sup>2</sup>C perspective, normal READ and WRITE commands are used.

- The configuration area contains required security-related information, such as access keys with related privileges, headers, customer ID (CID), originality signature and many more which will be loaded at power-on reset.

- Access to configuration blocks may be blocked at all or password protected with related configuration bits.

- All session registers are accessible in the configuration area as long as not locked by LOCK\_SESSION\_REG. These configuration items can be changed on the fly and have immediate effect, but get lost after power-on reset.

- SRAM

- SRAM is accessible when NTAG 5 link is V<sub>CC</sub> supplied and SRAM\_ENABLE is set to 1b.

- Volatile SRAM can be used for fast and frequent data transfer (see <u>Section 8.1.5</u>).

With WRITE SRAM (see <u>Section 8.2.3.6.2</u>) and READ SRAM (see <u>Section 8.2.3.6.1</u>), the content is written or read.

- When the SRAM gets mapped to user memory (the start address is always block 0 from both interfaces), then standard READ BLOCK and WRITE BLOCK commands can be used. This mechanism is used, e.g., for PHDC or dynamic pairing.

- From I<sup>2</sup>C perspective, SRAM is always located from address 2000h to 203Fh.

WARNING: The content of bytes and bits defined as RFU SHALL NOT be changed.

#### 8.1.2 User memory

According to NFC Forum Type 5 Tag Specification, the user accessible EEPROM memory is divided into blocks. A block is the smallest access unit. For NTAG 5 link,

NTP53x2

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2020. All rights reserved.

## NTAG 5 link - NFC Forum-compliant I<sup>2</sup>C bridge

each block consists of 4 bytes (1 block = 32 bits). Bit 0 in each byte represents the least significant bit (lsb) and bit 7 the most significant bit (msb), respectively.

User EEPROM map looks totally the same from NFC and I<sup>2</sup>C perspective.

The last block contains the 16-bit counter (see <u>Section 8.1.2.1</u>). It is only accessible from NFC perspective.

NTAG 5 link offers 2048 bytes (16384 bits) of user memory.

Table 6. User memory organization

|         | Table 6. Good money organization |       |            |                |        |             |  |

|---------|----------------------------------|-------|------------|----------------|--------|-------------|--|

| Block A | <b>Block Address</b>             |       | Byte 1     | Byte 2         | Byte 3 | Description |  |

| NFC     | I <sup>2</sup> C                 | (LSB) | Dyte i     | Dyte 2         | (MSB)  |             |  |

| 00h     | 0000h                            |       | Capability | or user memory |        |             |  |

| 01h     | 0001h                            |       |            |                |        |             |  |

| :       | :                                |       | User M     |                |        |             |  |

| 1FEh    | 01FEh                            |       |            |                |        |             |  |

| 1FFh    | -                                | C0    | C1         | 00h            | PROT   | Counter     |  |

User data at delivery contains an NFC Forum-compliant capability container and an NDEF message containing the URL www.nxp.com/nfc. First 6 blocks are initialized as illustrated in below table. The counter block is initialized with all 00h. Content of the rest of the user memory is undefined and contains random (rnd) data at delivery.

Table 7. Memory content at delivery

| Block A | Address          | Purto 0 | Purto 4 | Purto 2 | Puto 2 |  |

|---------|------------------|---------|---------|---------|--------|--|

| NFC     | I <sup>2</sup> C | Byte 0  | Byte 1  | Byte 2  | Byte 3 |  |

| 00h     | 0000h            | E1h     | 40h     | 80h     | 09h    |  |

| 01h     | 0001h            | 03h     | 10h     | D1h     | 01h    |  |

| 02h     | 0002h            | 0Ch     | 55h     | 01h     | 6Eh    |  |

| 03h     | 0003h            | 78h     | 70h     | 2Eh     | 63h    |  |

| 04h     | 0004h            | 6Fh     | 6Dh     | 2Fh     | 6Eh    |  |

| 05h     | 0005h            | 66h     | 63h     | FEh     | 00h    |  |

| 06h     | 0006h            | rnd     | rnd     | rnd     | rnd    |  |

|         |                  | rnd     | rnd     | rnd     | rnd    |  |

| 1FFh    | -                | 00h     | 00h     | 00h     | 00h    |  |

#### 8.1.2.1 16-bit counter

Last Block of the user memory contains the 16-bit counter. The block can be accessed with the standard read and write commands but special data format is required.

The standard protection conditions for the user memory are not valid for the counter block.

Counter block can only be accessed from NFC perspective.

The 16-bit counter can be

• preset to initial start value protected with the write password or by mutual authentication with a key with the Write privilege

NTP53x2

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2020. All rights reserved.

## NTAG 5 link - NFC Forum-compliant I<sup>2</sup>C bridge

- read

- increased by one, optionally protected with the read password or by mutual authentication with a key with the Read privilege

The counter can be read with an (EXTENDED) READ SINGLE BLOCK to the last block or (EXTENDED) READ MULTIPLE BLOCK command including the last block. The 4 byte data of the counter block provide the following information in <u>Table 8</u>.

Table 8. COUNTER BLOCK data structure

| Byte | Name     | Value     | Description                                                                                                                            |  |  |  |

|------|----------|-----------|----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0    | C0 (LSB) | 00h - FFh | Counter value                                                                                                                          |  |  |  |

| 1    | C1 (MSB) | 00h - FFh | - Counter value                                                                                                                        |  |  |  |

| 2    | -        | 00h       | RFU                                                                                                                                    |  |  |  |

|      |          | 00h       | Incrementing of the counter value is not protected                                                                                     |  |  |  |

| 3    | 3 PROT   |           | Incrementing of the counter value is protected with the read password or by mutual authentication depending on the used security level |  |  |  |

The counter can be preset to a start value with an (EXTENDED) WRITE SINGLE BLOCK command to counter block. The counter can only be preset to a start value after a SET PASSWORD command with the write password or a valid mutual authentication with a key with the Write privilege, depending on the used security level.

The PROT byte (data byte 3) value defines if the protection to increment the counter is enabled or disabled. If the protection is enabled, the read password or a valid mutual authentication with a key with the Read privilege is required to increment the counter value, again depending on the used security level.

The data for the (EXTENDED) WRITE SINGLE BLOCK command to preset the counter is defined in Table 9.

**Remark:** A Preset counter value of 0x0001 is not possible, a (EXTENDED) WRITE SINGLE BLOCK command with that value will only increment the counter.

Table 9. Preset counter data structure

| Byte | Name | Value                   | Description                                                                                |  |  |  |

|------|------|-------------------------|--------------------------------------------------------------------------------------------|--|--|--|

| 0    | C0   | 00h, 02h -<br>FFh (LSB) | Counter value                                                                              |  |  |  |

| 1    | C1   | 00h - FFh<br>(MSB)      | Counter value                                                                              |  |  |  |

| 2    | -    | 00h                     | RFU                                                                                        |  |  |  |

| 3    | PROT | 00h                     | Disable the protection to increment the counter                                            |  |  |  |

|      |      | 01h                     | Enable the protection to increment the counter with read password or mutual authentication |  |  |  |

To increment the counter by one with a (EXTENDED) WRITE SINGLE BLOCK command to counter block. If the protection to increment the counter is enabled, a SET PASSWORD command with the read password or a valid mutual authentication with a key with the Read privilege is required before.

The data for the (EXTENDED) WRITE SINGLE BLOCK command to increment the counter is defined in <u>Table 10</u>.

NTP53x2

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2020. All rights reserved

# NTAG 5 link - NFC Forum-compliant I<sup>2</sup>C bridge

**Remark:** The counter can only be incremented with the C0 and C1 values defined in Table 10. Other values than that preset the counter if a SET PASSWORD command with the write password or a valid mutual authentication with a key with the Write privilege has been executed before or leads to an error message.

Table 10. Increment counter data structure

| Byte | Name | Value     | Description                    |

|------|------|-----------|--------------------------------|

| 0    | C0   | 01h (LSB) | Value to increment the counter |

| 1    | C1   | 00h (MSB) | value to increment the counter |

| 2    | -    | 00h       | RFU                            |

| 3    | -    | 00h       | RFU                            |

## 8.1.3 Configuration Memory

The configuration memory contains the security and configuration information. Access to this memory area is only possible with WRITE CONFIG (see <u>Section 8.2.3.2.2</u>) and READ CONFIG (see <u>Section 8.2.3.2.1</u>) commands depending on the initialization status.

Writing to blocks with only RFU bytes is not possible and results in error code 0Fh from NFC perspective and NAK from I<sup>2</sup>C perspective. Reading complete RFU blocks results in receiving all bytes 00h.

Changing RFU bytes and bits is not allowed and may result in unintended behavior.

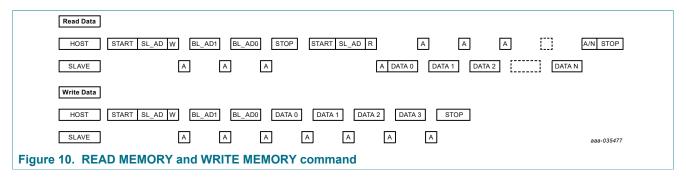

From I<sup>2</sup>C perspective, the configuration can be accessed using READ MEMORY and WRITE MEMORY command. Block address of configuration area from I<sup>2</sup>C perspective starts from 1000h.

In <u>Table 11</u> all NFC\_KHs, NFC\_KPs and AES\_KEYs (all marked with an asterisk) are only available in AES mode. NFC\_KHs and NFC\_KPs are not available at all and set to RFU in plain password mode. In the area of KEY\_0 and KEY\_1, the plain passwords are stored (see <u>Section 8.1.3.9</u>). The rest of the KEY area is RFU in plain password mode.

NOTE: AES mode is only available for NTP5332.

Different features can be configured with CONFIG bits. Similar to all other configuration options, the effect does not take place in the current session. The effect takes place after POR. If immediate change is expected, related session register bytes or bits need to be used (see <u>Section 8.1.4</u>).

To which section each block belongs is defined in first column (Sec.). Sections might be locked by setting related bit to 1b (see <u>Section 8.1.3.32</u>).

**Table 11. Configuration Memory organization**

| Sec. | Block A | Address          | Pyrto 0 | Puto 1                | Puto 2 | Durto 2 | Description                                |

|------|---------|------------------|---------|-----------------------|--------|---------|--------------------------------------------|

| Sec. | NFC     | I <sup>2</sup> C | Byte 0  | Byte 1                | Byte 2 | Byte 3  | Description                                |

| 0    | 00h     | 1000h            |         |                       |        |         | 32 byte Originality                        |

| 0    |         |                  | (       | ORIGINALITY_SIGNATURE |        |         | Signature                                  |

| 0    | 07h     | 1007h            |         |                       |        |         | (see <u>Section 8.1.3.1</u> )              |

| 0    | 08h     | 1008h            | СН      |                       | RFU    |         | Configuration Header (see Section 8.1.3.2) |

# NTAG 5 link - NFC Forum-compliant I<sup>2</sup>C bridge

|      | Block A | Address          | <b>D</b> 4 0 | 5.4.4    | D. ( . 0 | <b>D</b> 1 0                                                 | <b>.</b>                                                            |

|------|---------|------------------|--------------|----------|----------|--------------------------------------------------------------|---------------------------------------------------------------------|

| Sec. | NFC     | I <sup>2</sup> C | Byte 0       | Byte 1   | Byte 2   | Byte 3                                                       | Description                                                         |

| 0    | 09h     | 1009h            | CII          | CID RFU  |          |                                                              | Customer ID (see Section 8.1.3.3)                                   |

| N/A  | 0Ah     | 100Ah            |              | RFL      | J        |                                                              |                                                                     |

| N/A  | 0Bh     | 100Bh            |              | RFU      | J        |                                                              |                                                                     |

| 0    | 0Ch     | 100Ch            | RFU          | NFC_GCH  | RI       | ₹U                                                           | NFC Global Crypto<br>Header (see<br>Section 8.1.3.4)                |

| 0    | 0Dh     | 100Dh            | RFU          | NFC_CCH  | RI       | ₹U                                                           | NFC Crypto<br>Configuration Header<br>(see <u>Section 8.1.3.5</u> ) |

| 0    | 0Eh     | 100Eh            | NFC_AUT      | H_LIMIT  | RI       | NFC Authentication<br>Limit Counter (see<br>Section 8.1.3.6) |                                                                     |

| N/A  | 0Fh     | 100Fh            | RFU          |          |          |                                                              |                                                                     |

| 0    | 10h     | 1010h            | RFU          | NFC_KH0* | RI       | NFC Key Header 0 (see Section 8.1.3.7)                       |                                                                     |

| 0    | 11h     | 1011h            | NFC_KP0*     |          | RFU      | NFC Key Privileges 0 (see Section 8.1.3.8)                   |                                                                     |

| 0    | 12h     | 1012h            | RFU          | NFC_KH1* | RI       | ⁼U                                                           | NFC Key Header 1 (see Section 8.1.3.7)                              |

| 0    | 13h     | 1013h            | NFC_KP1*     |          | RFU      |                                                              | NFC Key Privileges 1 (see Section 8.1.3.8)                          |

| 0    | 14h     | 1014h            | RFU          | NFC_KH2* | RI       | ⁼U                                                           | NFC Key Header 2 (see Section 8.1.3.7)                              |

| 0    | 15h     | 1015h            | NFC_KP2*     |          | RFU      |                                                              | NFC Key Privileges 2 (see Section 8.1.3.8)                          |

| 0    | 16h     | 1016h            | RFU          | NFC_KH3* | RI       | ⁼U                                                           | NFC Key Header 3 (see Section 8.1.3.7)                              |

| 0    | 17h     | 1017h            | NFC_KP3*     |          | RFU      | NFC Key Privileges 3 (see Section 8.1.3.8)                   |                                                                     |

| N/A  | 18h     | 1018h            |              |          |          |                                                              |                                                                     |

| N/A  |         |                  | RFU          |          |          |                                                              |                                                                     |

| N/A  | 1Fh     | 101Fh            |              |          |          |                                                              |                                                                     |

| 0    | 20h     | 1020h            | KEY 0*       |          |          |                                                              | AES key 0 or                                                        |

| 0    | 21h     | 1021h            |              |          |          |                                                              | NFC_PWD_0 to                                                        |

| 0    | 22h     | 1022h            | KEY_0*       |          |          | NFC_PWD_3 (see<br>Section 8.1.3.9)                           |                                                                     |

| 0    | 23h     | 1023h            |              |          |          |                                                              | 223                                                                 |

# NTAG 5 link - NFC Forum-compliant I<sup>2</sup>C bridge

|      | Block A | Address          | Puto 0 Puto 1 |                  |        |                                                                         |                                                                             |

|------|---------|------------------|---------------|------------------|--------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| Sec. | NFC     | I <sup>2</sup> C | Byte 0        | Byte 1           | Byte 2 | Byte 3                                                                  | Description                                                                 |

| 0    | 24h     | 1024h            |               |                  |        |                                                                         | AEC key 4 em                                                                |

| 0    | 25h     | 1025h            | KEY 1*        |                  |        | AES key 1 or<br>NFC_PWD_4 to                                            |                                                                             |

| 0    | 26h     | 1026h            | KEY_1*        |                  |        | NFC_PWD_6 (see<br>Section 8.1.3.9)                                      |                                                                             |

| 0    | 27h     | 1027h            |               |                  |        |                                                                         | <u>Section 6.1.3.9</u> )                                                    |

| 0    | 28h     | 1028h            |               |                  |        |                                                                         |                                                                             |

| 0    | 29h     | 1029h            |               | VEV              | O*     |                                                                         | AES key 2 or RFU                                                            |

| 0    | 2Ah     | 102Ah            |               | KEY <sub>-</sub> |        |                                                                         | (see <u>Section 8.1.3.9</u> )                                               |

| 0    | 2Bh     | 102Bh            |               |                  |        |                                                                         |                                                                             |

| 0    | 2Ch     | 102Ch            |               |                  |        |                                                                         |                                                                             |

| 0    | 2Dh     | 102Dh            |               | VEV              | 0*     |                                                                         | AES key 3 or RFU                                                            |

| 0    | 2Eh     | 102Eh            |               | KEY <sub>-</sub> | _3"    |                                                                         | (see <u>Section 8.1.3.9</u> )                                               |

| 0    | 2Fh     | 102Fh            |               |                  |        |                                                                         |                                                                             |

| 1    | 30h     | 1030h            | I2C_KH        | I2C_KH RFU       |        | I <sup>2</sup> C Key Header (see Section 8.1.3.10)                      |                                                                             |

| 1    | 31h     | 1031h            | I2C_PP        | I2C_PPC          | RF     | ·U                                                                      | I <sup>2</sup> C Protection Pointer<br>and Config (see<br>Section 8.1.3.11) |

| 1    | 32h     | 1032h            | I2C_AUTH      | H_LIMIT          | RF     | ·U                                                                      | Authentication<br>Limit Counter (see<br>Section 8.1.3.12)                   |

| 1    | 33h     | 1033h            |               | I2C_PV           | VD_0   |                                                                         | I <sup>2</sup> C read password (see <u>Section 8.1.3.9</u> )                |

| 1    | 34h     | 1034h            |               | I2C_PV           | VD_1   |                                                                         | I <sup>2</sup> C write password (see <u>Section 8.1.3.9</u> )               |

| 1    | 35h     | 1035h            |               | I2C_PWD_2        |        |                                                                         |                                                                             |

| 1    | 36h     | 1036h            | I2C_PWD_3     |                  |        | Restricted AREA_1 I <sup>2</sup> C write password (see Section 8.1.3.9) |                                                                             |

| 2    | 37h     | 1037h            | CONFIG        |                  |        | Feature Configuration (see <u>Section 8.1.3.13</u> )                    |                                                                             |

| 3    | 38h     | 1038h            | SYNC_DATA     | A_BLOCK          | RF     | :U                                                                      | Block may be used for data transfer synchronization (see Section 8.1.3.14)  |

# NTAG 5 link - NFC Forum-compliant I<sup>2</sup>C bridge

| Coo  | Block A | Address          | Duto 0           | Duto 4                       | Duta 0      | Durán 2            | Description                                                                                                                                                    |

|------|---------|------------------|------------------|------------------------------|-------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sec. | NFC     | I <sup>2</sup> C | Byte 0           | Byte 1                       | Byte 2      | Byte 3             | Description                                                                                                                                                    |

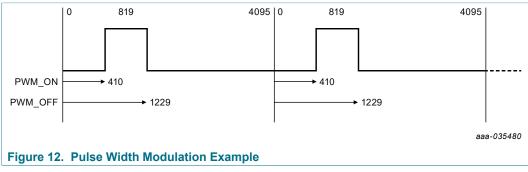

| 3    | 39h     | 1039h            | PWM_GPIO_CONFIG  |                              | RFU         |                    | PWM and GPIO<br>Configuration (see<br>Section 8.1.3.15)                                                                                                        |

| 3    | 3Ah     | 103Ah            |                  | PWM0_O                       | N_OFF       |                    | PWM1 Configuration (see Section 8.1.3.16)                                                                                                                      |

| 3    | 3Bh     | 103Bh            |                  | PWM1_O                       | N_OFF       |                    | PWM1 Configuration (see Section 8.1.3.16)                                                                                                                      |

| 3    | 3Ch     | 103Ch            | V                | WDT_CONFIG SRAM_ COPY_ BYTES |             |                    |                                                                                                                                                                |

| 3    | 3Dh     | 103Dh            | EH_CONF          | RFU                          | ED_CONF     | RFU                | Energy Harvesting (see Section 8.1.3.18) and Event Detection Pin (see Section 8.1.3.19) Configuration                                                          |

| 3    | 3Eh     | 103Eh            | I2C_SLAVE_CONFIG |                              | <del></del> | ER_CONFIG<br>5332) | I <sup>2</sup> C Configuration (see Section 8.1.3.20 and Section 8.1.3.21)                                                                                     |

| 3    | 3Fh     | 103Fh            | SEC_CONF         | SRAM_<br>CONF_PROT           | PP_AF       | REA_1              | Device Security Configuration (see Section 8.1.3.22) SRAM and Configuration Protection (see Section 8.1.3.23) AREA_1 Protection Pointer (see Section 8.1.3.24) |

| N/A  | 40h     | 1040h            |                  |                              |             |                    |                                                                                                                                                                |

| N/A  |         |                  |                  | RF                           | J           |                    |                                                                                                                                                                |

| N/A  | 44h     | 1044h            |                  |                              |             |                    |                                                                                                                                                                |

| 7    | 45h     | 1045             |                  |                              |             |                    |                                                                                                                                                                |

| 7    |         |                  | SRAM_DEFAULT     |                              |             |                    | Default SRAM content (see Section 8.1.5)                                                                                                                       |

| 7    | 54h     | 1054             |                  |                              |             |                    | (550 553,511 0.110)                                                                                                                                            |

| 4    | 55h     | 1055h            | AFI RFU          |                              |             |                    | Application Family Identifier (see Section 8.2.3.9.1)                                                                                                          |

| 4    | 56h     | 1056h            | DSFID            |                              | RFU         |                    | DSFID (see<br>Section 8.1.3.26)                                                                                                                                |

# NTAG 5 link - NFC Forum-compliant I<sup>2</sup>C bridge

| Coo  | Block A | Address          | Byte 0 Byte 1                           |                    | Duta 0   | Durán 2                                                                              | Decemination                                                                                               |

|------|---------|------------------|-----------------------------------------|--------------------|----------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| Sec. | NFC     | I <sup>2</sup> C | Byte 0                                  | Byte 1             | Byte 2   | Byte 3                                                                               | Description                                                                                                |

| 4    | 57h     | 1057h            | EAS_                                    | _ID                | RF       | ·U                                                                                   | EAS ID (see<br>Section 8.1.3.27)                                                                           |

| 4    | 58h     | 1058h            | NFC_<br>PP_AREA_0H                      | NFC_PPC            | RF       | FU                                                                                   | NFC Protection Pointer (see Section 8.1.3.28) and NFC Protection Pointer Conditions (see Section 8.1.3.29) |

| N/A  | 59h     | 1059h            |                                         |                    |          |                                                                                      |                                                                                                            |

| N/A  |         |                  |                                         | RF                 | J        |                                                                                      |                                                                                                            |

| N/A  | 69h     | 1069h            |                                         |                    |          |                                                                                      |                                                                                                            |

| 5    | 6Ah     | 106Ah            |                                         |                    |          |                                                                                      | NFC Lock block                                                                                             |

| 5    |         |                  | NFC_LOCK                                | _BLOCK             | RF       | -U                                                                                   | configuration (see Section 8.6.1)                                                                          |

| 5    | 89h     | 1089h            |                                         |                    |          |                                                                                      |                                                                                                            |

| 6    | 8Ah     | 108Ah            |                                         |                    |          |                                                                                      | I <sup>2</sup> C Lock block                                                                                |

| 6    |         |                  | I2C_LOCK                                | I2C_LOCK_BLOCK RFU |          |                                                                                      | configuration (see                                                                                         |

| 6    | 91h     | 1091h            |                                         |                    |          |                                                                                      | <u>Section 8.1.3.31</u> )                                                                                  |

| 8    | 92h     | 1092h            | NFC_                                    |                    | RFU      |                                                                                      | NFC section lock                                                                                           |

| 8    | 93h     | 1093h            | SECTION_<br>LOCK                        |                    |          |                                                                                      | bytes (see <u>Table 81</u> )                                                                               |

| 8    | 94h     | 1094h            | I2C_                                    |                    | RFU      |                                                                                      | I <sup>2</sup> C section lock bytes                                                                        |

| 8    | 95h     | 1095h            | SECTION_<br>LOCK                        |                    |          |                                                                                      | (see <u>Table 83</u> )                                                                                     |

| N/A  | 96h     | 1096h            |                                         | RFU from NFC       |          |                                                                                      | I <sup>2</sup> C read password<br>authenticate(see<br>Section 8.1.3.9)                                     |

| N/A  | 97h     | 1097h            |                                         | RFU from NFC       | •        |                                                                                      | I <sup>2</sup> C write password<br>authenticate (see<br>Section 8.1.3.9)                                   |

| N/A  | 98h     | 1098h            | RFU from NFC perspective I2C_PWD_2_AUTH |                    |          |                                                                                      | Restricted AREA_1 I <sup>2</sup> C read password authenticate (see Section 8.1.3.9)                        |

| N/A  | 99h     | 1099h            | RFU from NFC perspective I2C_PWD_3_AUTH |                    |          | Restricted AREA_1 I <sup>2</sup> C write password authenticate (see Section 8.1.3.9) |                                                                                                            |

| N/A  | 9Ah     | 109Ah            |                                         | RF                 | <b>I</b> |                                                                                      |                                                                                                            |

| N/A  |         |                  |                                         | IXE                | J        |                                                                                      |                                                                                                            |

## NTAG 5 link - NFC Forum-compliant I<sup>2</sup>C bridge

| Sec. | Block A | Address          | Byte 0 | Byte 1 By | Byte 2 | Byte 3 | Description |

|------|---------|------------------|--------|-----------|--------|--------|-------------|

| Sec. | NFC     | I <sup>2</sup> C | Byte 0 |           | Dyte 2 |        |             |

| N/A  | 9Fh     | 109Fh            |        |           |        |        |             |

## 8.1.3.1 Originality Signature

The Originality signature (see Section 8.8) is stored in first 8 blocks (block 00h to block 07h) of configuration memory and may be verified by the NFC device using the corresponding ECC public key. As the NXP originality signature is on default not locked, it may be re-programmed by the customer. If the originality check is not needed, it may even be used as additional 32 byte user EEPROM.

Table 12. 32 Byte Originality Signature

| Block A | ddress           | Byte 0     | Byte 1 | Puto 2 | Byte 3      |

|---------|------------------|------------|--------|--------|-------------|

| NFC     | I <sup>2</sup> C | Byte 0     | byte i | Byte 2 | byte 3      |

| 00h     | 1000h            | SIG0 (LSB) | SIG1   | SIG2   | SIG3        |

| 01h     | 1001h            | SIG4       | SIG5   | SIG6   | SIG7        |

| 02h     | 1002h            | SIG8       | SIG9   | SIG10  | SIG11       |

| 03h     | 1003h            | SIG12      | SIG13  | SIG14  | SIG15       |

| 04h     | 1004h            | SIG16      | SIG17  | SIG18  | SIG19       |

| 05h     | 1005h            | SIG20      | SIG21  | SIG22  | SIG23       |

| 06h     | 1006h            | SIG24      | SIG25  | SIG26  | SIG27       |

| 07h     | 1007h            | SIG28      | SIG29  | SIG30  | SIG31 (MSB) |

#### 8.1.3.2 Configuration Header

The Configuration Header (CH) byte defines the access conditions of both, Customer ID and Originality Signature.

Table 13. Configuration Header (CH) location

| Block A | Address          | Puto 0 | Byte 1 | Byto 2 | Byte 2 Byte 3 |

|---------|------------------|--------|--------|--------|---------------|

| NFC     | I <sup>2</sup> C | Byte 0 | byte i | Byte 2 |               |

| 08h     | 1008h            | СН     | RFU    |        |               |

Configuration Header byte can be read with READ CONFIG command (see Section 8.2.3.2.1) and written with WRITE CONFIG command (see Section 8.2.3.2.2). Once locked (set to E7h), CH byte cannot be updated anymore and Originality Signature and Customer ID gets locked permanently from NFC perspective.

From I<sup>2</sup>C perspective this block can be read and written if not locked by the I<sup>2</sup>C section lock. Once locked, CH byte cannot be updated anymore and Originality Signature and CID gets locked permanently from I<sup>2</sup>C perspective.

**Table 14. Configuration Header Codes**

| Value | Mode                | Write Access |

|-------|---------------------|--------------|

| 81h   | Writeable (default) | Yes          |

| E7h   | Locked              | No           |

## NTAG 5 link - NFC Forum-compliant I<sup>2</sup>C bridge

| Value      | Mode    | Write Access |

|------------|---------|--------------|

| All others | Invalid | No           |

#### 8.1.3.3 Customer ID (CID)

The Customer ID at delivery is C000h and can be reprogrammed and locked. It might be used to identify the product.

The two most significant bits (b7 and b6 of CID (MSB)) are always equal to 11b. Only CID[13-0] may be written by customer. Note, that other values of the two most significant bits are RFU.

When the CID is written with WRITE CONFIG command, the 2 most significant bits are always set to 11b. The input CID in WRITE CONFIG command (see <u>Section 8.2.3.2.2</u>) is bit wise ORed with C000h.

As long as not locked by the I<sup>2</sup>C section lock, CID maybe updated from I<sup>2</sup>C perspective with the same logic as from NFC perspective.

Example: When setting CID to 10AAh, resulting customer-specific CID is D0AAh.

Table 15. Customer ID (CID) location

| Block A | Address          | Byto 0    | Byte 1    | Byte 2 | Byte 3 |

|---------|------------------|-----------|-----------|--------|--------|

| NFC     | I <sup>2</sup> C | Byte 0    | byte i    | Byte 2 |        |

| 09h     | 1009h            | CID (LSB) | CID (MSB) | RF     | -U     |

The CID can be permanently locked by setting the Configuration Header to Locked state (see <u>Table 14</u>) using WRITE CONFIG command. Note, that Originality Signature gets locked, too.

#### 8.1.3.4 NFC Global Crypto Header

The NFC Global Crypto Header (NFC\_GCH) defines the status and access of the

- NFC passwords in plain password mode and all other NFC features listed below

- NFC Keys

- NFC Protection Pointer

- NFC Protection Pointer Conditions

- NFC Key Headers

- NFC Key Privileges

- NFC Crypto Configuration Header

- · EAS and AFI protection

As long as not locked by the RF section lock, the NFC Global Crypto Header can be written with WRITE CONFIG command (see <u>Section 8.2.3.2.2</u>). The programming of NFC Global Crypto Header can be done in only one direction from lower state to higher independently from the interface and it is irreversible.

Same rules apply from I<sup>2</sup>C perspective, as long as not locked by the I<sup>2</sup>C section lock.

Once locked (as per table below), GCH cannot be updated anymore.

# NTAG 5 link - NFC Forum-compliant I<sup>2</sup>C bridge

Table 16. NFC Global Crypto Header (GCH) location

| Block A | Address          | Byto 0 | Byte 1  | Byte 2 | Byte 3 |

|---------|------------------|--------|---------|--------|--------|

| NFC     | I <sup>2</sup> C | Byte 0 | byte i  | Byte 2 | byte 3 |

| 0Ch     | 100Ch            | RFU    | NFC_GCH | RF     | ⁼U     |

#### Table 17. Global Crypto Header Configuration in plain password mode

|            | <u> </u>           |                                                                                              |

|------------|--------------------|----------------------------------------------------------------------------------------------|

| Value      | Status             | Description                                                                                  |

| 81h        | Writable (default) | The NFC passwords can be read and written with the READ CONFIG and WRITE CONFIG commands.    |

| E7h        | Locked             | The NFC passwords cannot be read and written with the READ CONFIG and WRITE CONFIG commands. |

| all others | Invalid            |                                                                                              |

Table 18. Global Crypto Header Configuration Value in AES mode

| Value | Status                          | Description                                                                                                                                                                                                                                                                              |

|-------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 81h   | Deactivated (default)           | The settings of the NFC Protection Pointer and the NFC Protection Pointer Condition are not activated. Read and write access to the user memory is possible independent of the settings without a previous mutual authentication.                                                        |

|       |                                 | The Protection Pointer Address and the NFC Protection Pointer Condition byte can be modified with a PROTECT PAGE command without a previous mutual authentication except of the LOCK PAGE PROTECTION CONDITION command has been successfully executed before.                            |

|       |                                 | The Keys and Key Privileges can be read and written with the READ CONFIG and WRITE CONFIG commands according to the status of the related Key Header.                                                                                                                                    |

|       |                                 | The settings for the EAS/AFI protection are not activated. Access with the related commands to EAS and AFI is possible without a previous mutual authentication.                                                                                                                         |

| 87h   | Deactivated & privileges locked | The status is the same as for 81h with the exception that the Key Privileges are locked and cannot longer be modified.  The settings for the EAS/AFI protection are not activated. Access with the related commands to EAS and AFI is possible without a previous mutual authentication. |

| C1h   | Access right activated          | The settings of the Protection Pointer address and the Protection Pointer Condition are enabled. Read and write access protection is enabled according to the initialized values.                                                                                                        |

|       |                                 | The Keys and Key Privileges can be read and written with the READ CONFIG and WRITE CONFIG commands according to the status of the related Key Header.                                                                                                                                    |

|       |                                 | The settings for the EAS/AFI protection are enabled. Access with the related commands to EAS and AFI is only possible according to the EAS/AFI protection conditions.                                                                                                                    |

## NTAG 5 link - NFC Forum-compliant I<sup>2</sup>C bridge

| Value      | Status                                    | Description                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C7h        | Access right activated &privileges locked | The status is the same as for C1h with the exception that the Key Privileges are locked and cannot longer be modified.  The settings for the EAS/AFI protection are enabled. Access with the related commands to EAS and AFI is only possible according to the EAS/AFI protection conditions.                                                                                                                             |

| E7h        | Activated                                 | The settings of the NFC Protection Pointer and the NFC Protection Pointer Condition are enabled. Read and write access protection is enabled according to the initialized values.  All Key Header Privileges and Keys are locked cannot be modified The settings for the EAS/AFI protection are enabled. Access with the related commands to EAS and AFI is only possible according to the EAS/AFI protection conditions. |

| all others | Invalid                                   |                                                                                                                                                                                                                                                                                                                                                                                                                           |

#### 8.1.3.5 NFC Crypto Configuration Header

The value of the NFC Crypto Configuration Header (NFC\_CCH) locks the NFC Authentication Limit to the defined value and can only be changed after authentication. NFC\_CCH can be written by using the WRITE CONFIGURATION command (see Section 8.2.3.2.2).

From I<sup>2</sup>C perspective, NFC\_CCH can be accessed with READ and WRITE command, as long as not locked by the I<sup>2</sup>C section lock.

Table 19. Crypto Configuration Header (CCH) location

| Block A | Address          | Byte 0 | Byte 1  | Byte 2 | Byte 3 |

|---------|------------------|--------|---------|--------|--------|

| NFC     | I <sup>2</sup> C | Byte 0 | byte i  | Byte 2 |        |

| 0Dh     | 100Dh            | RFU    | NFC_CCH | RF     | -U     |

**Table 20. Crypto Configuration Header Values**

| Value      | Mode               | Write Access                                                                                                                                                                                                                                                                                          |

|------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 81h        | Unlocked (default) | Authentication limit can be modified.                                                                                                                                                                                                                                                                 |

| E7h        | Locked             | Authentication limit is locked and can only be modified after mutual authentication with a key with activated crypto configuration privilege or authenticating with the write password. In 64-bit password mode both, the read and write password are required, depending on the used security level. |

| All others | Invalid            |                                                                                                                                                                                                                                                                                                       |

#### 8.1.3.6 NFC Authentication Limit Counter

The NFC Authentication Limit Counter is a feature to limit the number of authentications. When enabled, the counter is incremented for every CHALLENGE (see Section 8.2.3.4.6) or AUTHENTICATION (see Section 8.6.4) command. Both, positive and negative attempts get counted. On default, the counter is not enabled (NFC AUTH LIMIT = 0000h).

## NTAG 5 link - NFC Forum-compliant I<sup>2</sup>C bridge

In plain password mode, NTAG 5 link implements the NFC Authentication Limit in counting negative Password Authentication attempts with the SET PASSWORD command, except for the Privacy password. The counter will be reset automatically to zero after a successful authentication.

Table 21. NFC Authentication Limit Counter (NFC AUTH LIMIT) location

| Block | Address          | Buto 0                   | Duto 4                   | Puto 2 | Byte 3 |

|-------|------------------|--------------------------|--------------------------|--------|--------|

| NFC   | I <sup>2</sup> C | Byte 0                   | Byte 1                   | Byte 2 |        |

| 0Eh   | 100Eh            | NFC_AUTH_<br>LIMIT (LSB) | NFC_AUTH_<br>LIMIT (MSB) | RF     | -U     |

Byte 0 of Block 0Eh is LSB and Byte 1 is MSB of the NFC Authentication Limit counter value.

The Authentication limit is enabled with the most significant bit of Byte 1 is set to 1b. The remaining 15 bits of NFC AUTH LIMIT are defining the preset value.

The start value for the Authentication Limit can be preset with a WRITE CONFIG command (see <u>Section 8.2.3.2.2</u>) if

- the Crypto Config Header is not set to "Locked" and the NFC Global Crypto Header is not set to "Activated" or

- a valid mutual authentication with a key with the Crypto Config privilege set has been executed before.

In plain password mode, the Counter can be written with a WRITE CONFIG command (see Section 8.2.3.2.2) if

- the Crypto Config Header is not set to "Locked" and NFC Global Crypto Header is not set to "Locked", or

- a valid SET\_PASSWORD command with the write password has been executed before. In 64-bit password mode, both read and write passwords are required.

#### Examples:

- 8000h enables and presets the authentication limit to 0, which means the maximum number of authentications (32767) before a preset is required again

- F000h enables and presets the authentication limit to 28672

If the NFC Authentication Limit is enabled, the authentication limit value is increased by one at each CHALLENGE or AUTHENTICATE command (first step only). As soon as the value of the Authentication limit reaches

- FF00h: only mutual authentication will be accepted to reset the authentication limit

- FFFFh: no further authentication is possible any longer. This status is irreversible.

**Remark:** The absolute maximum authentication limit value is FFFEh before a preset is required, otherwise the authentication is irreversibly locked (no longer available).

From I<sup>2</sup>C perspective, this block can be read and written if not locked by the I<sup>2</sup>C section lock.

#### 8.1.3.7 NFC Key Header

The NFC Key Header bytes (NFC\_KH0, NFC\_KH1, NFC\_KH2, NFC\_KH3) define the status for the related NFC key.

## NTAG 5 link - NFC Forum-compliant I<sup>2</sup>C bridge

The programming of NFC Key Header can be done in only one direction from lower state to higher and it is irreversible from NFC perspective.

Same rules apply from I<sup>2</sup>C perspective, as long as not locked by the I<sup>2</sup>C section lock. Once locked (as per table below) cannot be updated anymore from I2C interface.

Table below shows the location of the NFC Key Headers in the configuration memory. When using password authentication, these bytes and blocks are all RFU.

NOTE: Key headers are only available for NTP5332 in AES mode.

Table 22. NFC Key Header (KHx) location

| Block A | Address          | Puto 0 | Puto 1   | Puto 2 | Puto 2 |  |

|---------|------------------|--------|----------|--------|--------|--|

| NFC     | I <sup>2</sup> C | Byte 0 | Byte 1   | Byte 2 | Byte 3 |  |

| 10h     | 1010h            | RFU    | NFC_KH0* | RFU    |        |  |

| 12h     | 1012h            | RFU    | NFC_KH1* | RFU    |        |  |

| 14h     | 1014h            | RFU    | NFC_KH2* | RFU    |        |  |

| 16h     | 1016h            | RFU    | NFC_KH3* | RFU    |        |  |

If the Global Crypto Header is in the "Activate and locked" state, all crypto settings (Key Headers, Keys and Privileges) are locked and cannot longer be modified.

Table 23. NFC Key Header Values

| Value | Status               | Description                                                                                                                                                                                                                                                                    |

|-------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 81h   | Not active (default) | The related Key and the Key Privileges can be read and written with the READ CONFIG and WRITE CONFIG commands. The related key is not active and cannot be used. The Key Privileges of the related Key are not valid.                                                          |

| E7h   | Active and locked    | The related Key and its privileges are active and locked and cannot be modified any longer. The related Key cannot be read or written with the READ CONFIG and WRITE CONFIG commands. The related Key Header and Key Privileges can only be read with the READ CONFIG command. |

| FFh   | Disabled             | Related Key is disabled and cannot be used                                                                                                                                                                                                                                     |

**Remark:** It is recommended to set the key header for not required keys to disabled (FFh).

#### 8.1.3.8 NFC Key Privileges

The NFC Key Privileges bytes define the privileges for the related key. Writing with WRITE CONFIG command to the related block depends on the status of the related NFC Key Header (see Table 23)

From I<sup>2</sup>C perspective, this block can be read and written if not locked by the I<sup>2</sup>C section lock.

Table shows the location of the Key Privileges in the configuration memory.

NOTE: Key privileges are only available for NTP5332.

## NTAG 5 link - NFC Forum-compliant I<sup>2</sup>C bridge

Table 24. NFC Key Privileges (KPx) location

| Block A | Address          | Pyrto 0 | Puto 1 | Puto 2 | Byte 3 |

|---------|------------------|---------|--------|--------|--------|

| NFC     | I <sup>2</sup> C | Byte 0  | Byte 1 | Byte 2 |        |

| 11h     | 1011h            | NFC_KP0 |        |        |        |

| 13h     | 1013h            | NFC_KP1 | RFU    |        |        |

| 15h     | 1015h            | NFC_KP2 |        | RFU    |        |

| 17h     | 1017h            | NFC_KP3 | RFU    |        |        |

Table 25 shows the definition of the Key Privileges bytes KPx. The bits define the privileges for the related key used with mutual authentication. If the related bit is set to 1b, the access for the dependent area/feature is granted after mutual authentication with the related key.

Table 25. Definition of NFC Key Privileges bytes KPx

| Bit | Privilege               | Description                                                                                                                             |  |  |  |

|-----|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7   | Restricted AREA_1 Write | Write access to restricted user memory AREA_1                                                                                           |  |  |  |

| 6   | Restricted AREA_1 Read  | Read access to restricted user memory AREA_1                                                                                            |  |  |  |

| 5   | Crypto Config           | Preset of Authentication Limit                                                                                                          |  |  |  |

| 4   | EAS/AFI                 | Access for write alike command for EAS and AFI as following: PROTECT EAS/AFI SET EAS RESET EAS LOCK EAS WRITE EAS ID WRITE AFI LOCK AFI |  |  |  |

| 3   | Destroy                 | Access to the DESTROY functionality                                                                                                     |  |  |  |

| 2   | Privacy                 | Enable/disable of the PRIVACY mode                                                                                                      |  |  |  |

| 1   | Write                   | Write access to protected user memory area                                                                                              |  |  |  |

| 0   | Read                    | Read access to protected user memory area                                                                                               |  |  |  |

#### 8.1.3.9 Keys and Passwords

The keys or passwords are stored in the configuration memory. The usage of the individual keys depends on the related Key Privileges.

The state of the keys (including read and write access with the READ CONFIG and WRITE CONFIG commands) depends on the status of the related Key Header and the status of the Global Crypto Header.

From I<sup>2</sup>C perspective, these blocks can be written if not locked by the I<sup>2</sup>C section lock.

Table below shows the location of the 128-bit AES <u>Table 26</u> keys in the configuration memory.