# 3 Pin Microprocessor Supervisor Circuit

November 2017 Rev. 2.0.2

## **GENERAL DESCRIPTION**

The SP809/SP810 are low power microprocessor ( $\mu P$ ) supervisory circuits used to monitor power supplies in  $\mu P$  and digital systems.

They provide applications with benefits of circuit reliability and low cost by eliminating external components. If the VCC supply voltage falls below preset threshold then a reset signal is asserted for at least 140ms after  $V_{\text{CC}}$  has risen above the reset threshold.

Both the SP809 and SP810 were designed with a reset comparator to help identify invalid signals, which last less than 140ms. The only difference between them is that they have an active-low  $\overline{\text{RESET}}$  output and active-high RESET output, respectively. Low supply current (1µA) makes SP809/SP810 ideal for portable equipment.

The devices are available in 3 pin SOT-23 package.

| Part Number | Output Type           |

|-------------|-----------------------|

| SP809N      | Open Drain Active Low |

| SP809       | Push-Pull Low         |

| SP810       | Push-Pull Active High |

## **APPLICATIONS**

- Portable Electronic Devices

- Electrical Power Meters

- Digital Still Cameras

- µP Power Monitoring

#### **FEATURES**

- Ultra Low Supply Current 1µA (typ)

- Guaranteed Reset valid to V<sub>CC</sub> = 0.9V

- 140ms Power-On Reset Pulse Width

- Internally Fixed Threshold

2.3V, 2.6V, 2.9V, 3.1V, 4.4V, 4.6V

- 1.5% Voltage Threshold Tolerance

- 3 Pin SOT-23 Package

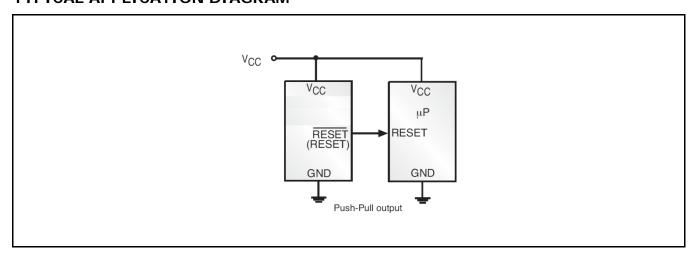

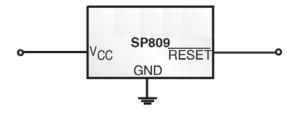

## TYPICAL APPLICATION DIAGRAM

Fig. 1: SP809 / SP810 Application Diagram

# 3 Pin Microprocessor Supervisor Circuit

## **ABSOLUTE MAXIMUM RATINGS**

These are stress ratings only and functional operation of the device at these ratings or any other above those indicated in the operation sections of the specifications below is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

| Vcc                                      | 0.3V to 6.5V     |

|------------------------------------------|------------------|

| RESET, RESET                             | 0.3V to Vcc+0.3V |

| Output Current (RESET, RESET)            | 20mA             |

| Power Dissipation (T <sub>A</sub> =70°C) | 320mW            |

| Junction Temperature                     | 125°C            |

| Storage Temperature                      | 65°C to 150°C    |

## **OPERATING RATINGS**

Input Voltage Range  $V_{\text{CC}}$  ..... 0.9V to 6V Junction Temperature Range ..... -40°C to 85°C

## **ELECTRICAL SPECIFICATIONS**

Specifications with standard type are for an Operating Temperature of  $T_A = 25\,^{\circ}\text{C}$  only; limits applying over the full Operating Temperature range are denoted by a "•". Minimum and Maximum limits are guaranteed through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_A = 25\,^{\circ}\text{C}$ , and are provided for reference purposes only. Unless otherwise indicated,  $T_A = 25\,^{\circ}\text{C}$ .

| Parameter                                     | Min.               | Тур. | Max.  | Units |   | Conditions                                               |

|-----------------------------------------------|--------------------|------|-------|-------|---|----------------------------------------------------------|

| Operating Voltage Range Vcc                   | 0.9                |      | 6.0   | V     |   |                                                          |

| Supply Current Icc                            |                    | 1.0  | 3.0   | μΑ    |   | $V_{CC} = V_{TH} + 0.1V$                                 |

|                                               | 2.265              | 2.3  | 2.335 |       |   | $T_A = +25$ °C                                           |

|                                               | 2.254              |      | 2.346 |       | • | T <sub>A</sub> =-40°C to 85°C                            |

|                                               | 2.561              | 2.6  | 2.639 | -     |   | $T_A = +25$ °C                                           |

|                                               | 2.548              |      | 2.652 |       | • | T <sub>A</sub> =-40°C to 85°C                            |

|                                               | 2.857              | 2.9  | 2.944 |       |   | $T_A = +25$ °C                                           |

| Reset Threshold V <sub>TH</sub>               | 2.842              |      | 2.958 | V     | • | T <sub>A</sub> =-40°C to 85°C                            |

| Reset Threshold VTH                           | 3.054              | 3.1  | 3.147 | V     |   | $T_A = +25$ °C                                           |

|                                               | 3.038              |      | 3.162 |       | • | T <sub>A</sub> =-40°C to 85°C                            |

|                                               | 4.334              | 4.4  | 4.466 |       | 1 |                                                          |

|                                               | 4.312              |      | 4.488 |       | • | T <sub>A</sub> =-40°C to 85°C                            |

|                                               | 4.531              | 4.6  | 4.669 |       |   | T <sub>A</sub> =+25°C                                    |

|                                               | 4.508              |      | 4.692 |       | • | T <sub>A</sub> =-40°C to 85°C                            |

| V <sub>CC</sub> Reset Delay t <sub>TRIP</sub> |                    | 20   |       | μs    |   | $V_{CC} = V_{TH}$ to $(V_{TH} - 0.1V)$ , $V_{TH} = 3.1V$ |

| Dood Active Timesout Deviced t                | 140                | 230  | 560   |       |   | $T_A = +25$ °C                                           |

| Reset Active Timeout Period trp               | 100                |      | 1030  | ms    | • | T <sub>A</sub> =-40°C to 85°C                            |

| RESET Output Voltage VoH                      | 0.8Vcc             |      |       | V     |   | $V_{CC}=V_{TH}$ - 0.1V, $I_{SOURCE}=1.2mA$               |

| RESET Output Voltage Vol                      |                    |      | 0.3   | V     |   | $V_{CC} = V_{TH} + 0.1V$ , $I_{SINK} = 1.2mA$            |

| RESET Output Voltage V <sub>OH</sub>          | 0.8V <sub>CC</sub> |      |       | W     |   | $V_{CC}=V_{TH} + 0.1V$ , $I_{SOURCE} = 1.2mA$            |

| RESET Output Voltage Vol                      |                    |      | 0.3   | V     |   | $V_{CC}=V_{TH}$ - 0.1V, $I_{SINK}=1.2mA$                 |

Note 1: RESET output is for SP809; RESET output is for SP810.

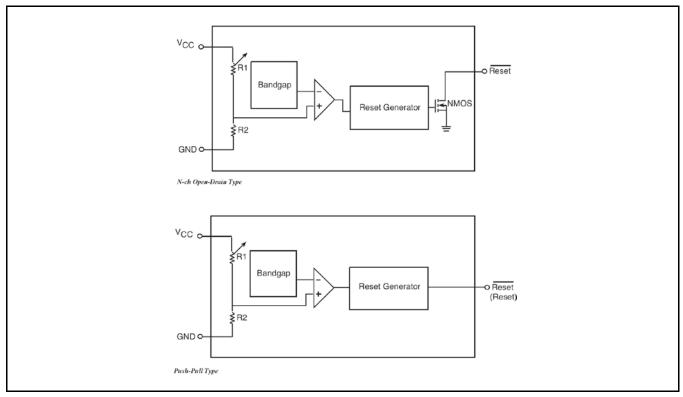

# **BLOCK DIAGRAM**

Fig. 2: SP809 / SP810 Block Diagram

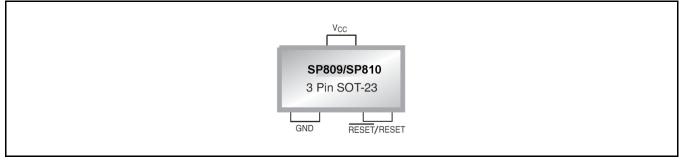

## **PIN ASSIGNMENT**

Fig. 3: SP809 / SP810 Pin Assignment

# **PIN DESCRIPTION**

| Name            | Pin Number | Description                                                                              |

|-----------------|------------|------------------------------------------------------------------------------------------|

| GND             | 1          | Ground Signal                                                                            |

| RESET           | 2          | Active Low Output Pin. RESET Output remains high while VCC is below the reset threshold  |

| RESET           | 2          | Active High Output Pin. RESET Output remains high while VCC is below the reset threshold |

| V <sub>CC</sub> | 3          | Supply Voltage                                                                           |

# ORDERING INFORMATION<sup>(1)</sup>

| Part Number                      | Operating Temperature Range | Lead-Free          | Package | Packing Method |

|----------------------------------|-----------------------------|--------------------|---------|----------------|

| SP809EK-L-2-3/TR                 |                             |                    |         |                |

| SP809EK-L-2-6/TR                 |                             |                    |         |                |

| SP809EK-L-2-9/TR                 |                             |                    |         |                |

| SP809EK-L-3-1/TR <sup>(3)</sup>  |                             |                    |         |                |

| SP809EK-L-4-6/TR <sup>(3)</sup>  | 400C < T < + 0F0C           | Yes <sup>(2)</sup> | COTOO   | Tana & Daal    |

| SP809NEK-L-2-3/TR <sup>(3)</sup> | -40°C≤T <sub>A</sub> ≤+85°C | Yes                | SOT23-3 | Tape & Reel    |

| SP809NEK-L-2-9/TR <sup>(3)</sup> |                             |                    |         |                |

| SP809NEK-L-3-1/TR                |                             |                    |         |                |

| SP809NEK-L-4-6/TR <sup>(3)</sup> |                             |                    |         |                |

| SP810EK-L-4-4/TR <sup>(3)</sup>  |                             |                    |         |                |

#### NOTES:

- 1. Refer to <a href="www.exar.com/SP809">www.exar.com/SP809</a> and <a href="www.exar.com/SP810">www.exar.com/SP810</a> for most up-to-date Ordering Information.

- 2. Visit www.exar.com for additional information on Environmental Rating.

- 3. NRND Not Recommended for New Designs.

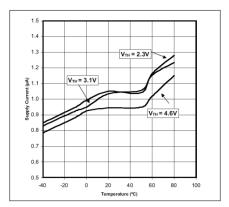

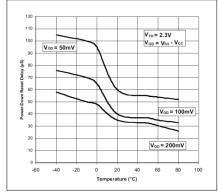

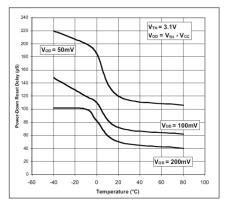

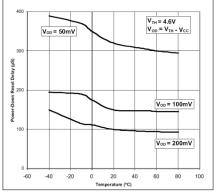

## TYPICAL PERFORMANCE CHARACTERISTICS

All data taken at  $T_A = 25\,^{\circ}\text{C}$ , unless otherwise specified - Schematic and BOM from Application Information section of this datasheet.

Fig. 4: Supply Current versus Temperature

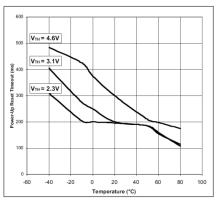

Fig. 5: Power-Down Reset Delay versus Temperature

Fig. 6: Power-Down Reset Delay versus Temperature

Fig. 7: Power-Down Reset Delay versus Temperature

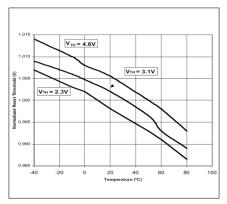

Fig. 8: Normalized Reset Threshold versus Temperature

Fig. 9: Power-Up Reset Time-out versus Temperature

#### THEORY OF OPERATION

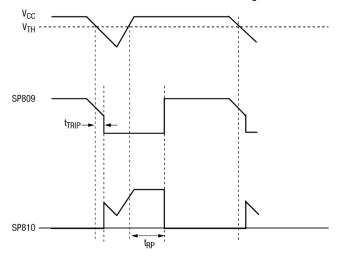

$\mu P$  will be activated at a valid reset state. These  $\mu P$  supervisory circuits assert reset to prevent code execution errors during power-up, power-down, or brownout conditions.

Reset is guaranteed to be a logic low for  $V_{TH} > V_{CC} > 0.9V$ . Once  $V_{CC}$  exceeded the reset threshold, an internal timer keeps RESET low for the reset timeout period; after this interval, RESET goes high.

If a brownout condition occ<u>urs</u> ( $V_{\text{CC}}$  drops below the reset threshold), RESET goes low. Any time  $V_{\text{CC}}$  goes below the reset threshold, the internal timer resets to zero, and RESET goes low. The internal timer is activated after  $V_{\text{CC}}$  returns above the reset threshold, and RESET remains low for the reset timeout period.

# BENEFIT OF HIGHLY ACCURATE RESET THRESHOLD

SP809/810 with specified voltage as  $5V\pm10\%$  or  $3V\pm10\%$  are ideal for systems using a

$5V\pm5\%$  or  $3V\pm5\%$  power supply. The reset is guaranteed to assert after the power supply falls below the minimum specified operating voltage range of the system ICs. The pretrimmed thresholds are reducing the range over which an undesirable reset may occur.

Fig. 10: Timing Waveforms

## APPLICATION INFORMATION

## **NEGATIVE GOING VCC TRANSIENTS**

In addition to issuing a reset to the  $\mu P$  during power-up, power-down, and brownout conditions, SP809 series are relatively resistant to short-duration negative-going  $V_{\text{CC}}$  transient.

# Ensuring a Valid Reset Output Down to $V_{\text{CC}}$ =0

When Vcc falls below 0.9V, SP809 RESET output no longer sinks current; it becomes an open circuit. In this case, high-impedance CMOS logic inputs connecting to RESET can drift to undetermined voltages. Therefore, SP809/810 with CMOS is perfect for most applications of Vcc down to 0.9V.

However in applications where  $\overline{\text{RESET}}$  must be valid down to OV, adding a pull-down resistor to  $\overline{\text{RESET}}$  causes any leakage currents to flow to ground, holding  $\overline{\text{RESET}}$  low.

# INTERFACING TO µP WITH BIDIRECTIONAL RESET PINS

The RESET output on the SP809N is open drain, this device interfaces easily with  $\mu Ps$  that have bidirectional reset pins. Connecting the  $\mu Ps$  supervisor's RESET output directly to the microcontroller's RESET pin with a single pull-up resistor allows either device to assert reset.

#### **TEST CIRCUIT**

Fig. 11: Test Circuit

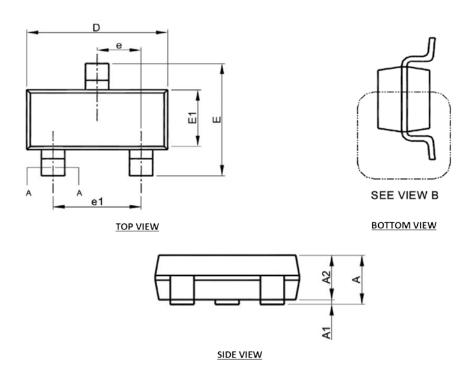

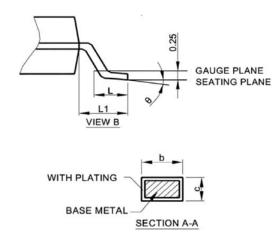

## **PACKAGE SPECIFICATION**

## **3-PIN SOT23**

| S                     | SOT         | T-23     |  |  |

|-----------------------|-------------|----------|--|--|

| S<br>M<br>B<br>O<br>L | MILLIMETERS |          |  |  |

| ů.                    | MIN.        | MAX.     |  |  |

| Α                     | 0.95        | 1.45     |  |  |

| A1                    | 0.00        | 0.15     |  |  |

| A2                    | 0.90        | 1.30     |  |  |

| b                     | 0.30        | 0.50     |  |  |

| С                     | 0.08        | 0.22     |  |  |

| D                     | 2.80        | 3.00     |  |  |

| E                     | 2.60        | 3.00     |  |  |

| E1                    | 1.50        | 1.70     |  |  |

| е                     | 0.95        | BSC      |  |  |

| e1                    | 1.90        | BSC      |  |  |

| L                     | 0.30        | 0.60     |  |  |

| L1                    | 0.60        | 0.60 REF |  |  |

| θ                     | 0°          | 8°       |  |  |

TERMINAL DETAILS

- 1. Refer to Jedec MO-178

- Dimension "D" does not include mold flash, protrusions or gate burrs.

Mold flash, protrusion or gate burrs shall not exceed 10mils per side.

- 3. Dimension "E1" does not include inter-lead flash or protursions.

- 4. All dimensions are milimeters.

Drawing No. : POD - 00000128

Revision: A

# 3 Pin Microprocessor Supervisor Circuit

#### **REVISION HISTORY**

| Revision | Date          | Description                                                                                               |

|----------|---------------|-----------------------------------------------------------------------------------------------------------|

| 2.0.0    | 2011          | Reformat of Datasheet<br>Correction of package drawing                                                    |

| 2.0.1    |               | Correct Reset Delay conditions. Updated to MaxLinear logo. Updated format and ordering information table. |

| 2.0.2    | November 2017 | Corrected typo from rev 2.0.1, added 2 missing overlines to RESET in Electrical Specifications.           |

#### Corporate Headquarters:

5966 La Place Court Suite 100 Carlsbad, CA 92008 Tel.:+1 (760) 692-0711 Fax: +1 (760) 444-8598

www.maxlinear.com

#### **High Performance Analog:**

1060 Rincon Circle San Jose, CA 95131 Tel.: +1 (669) 265-6100 Fax: +1 (669) 265-6101

Email: powertechsupport@exar.com

www.exar.com

The content of this document is furnished for informational use only, is subject to change without notice, and should not be construed as a commitment by MaxLinear, Inc.. MaxLinear, Inc. assumes no responsibility or liability for any errors or inaccuracies that may appear in the informational content contained in this guide. Complying with all applicable copyright laws is the responsibility of the user. Without limiting the rights under copyright, no part of this document may be reproduced into, stored in, or introduced into a retrieval system, or transmitted in any form or by any means (electronic, mechanical, photocopying, recording, or otherwise), or for any purpose, without the express written permission of MaxLinear, Inc.

Maxlinear, Inc. does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless MaxLinear, Inc. receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of MaxLinear, Inc. is adequately protected under the circumstances.

MaxLinear, Inc. may have patents, patent applications, trademarks, copyrights, or other intellectual property rights covering subject matter in this document. Except as expressly provided in any written license agreement from MaxLinear, Inc., the furnishing of this document does not give you any license to these patents, trademarks, copyrights, or other intellectual property.

Company and product names may be registered trademarks or trademarks of the respective owners with which they are associated.

© 2011 - 2017 MaxLinear, Inc. All rights reserved.